开发板:DE0-NANO;

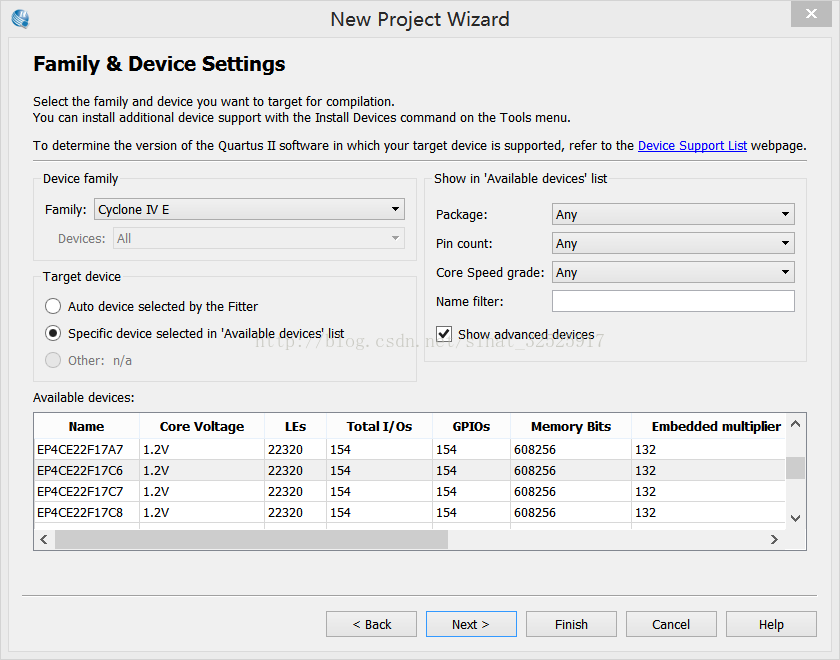

型号:Cyclone Ⅳ系列,EP4CE22F17C6;

开发平台:Quartus II 15.0;

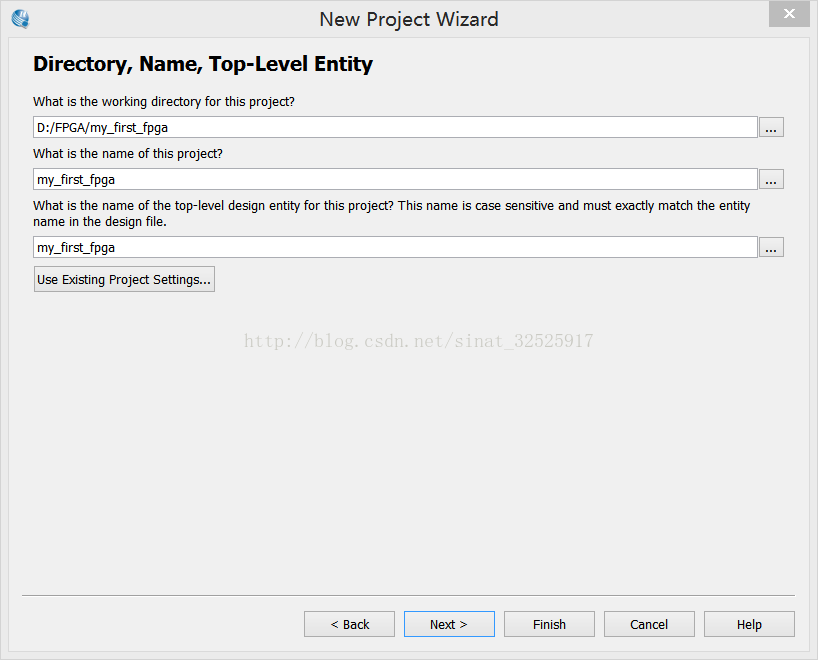

File → New Project Wizard → Next → 选择程序目录、填写project名称(目录、名称必须全英文)

Next → Empty project → Next → Next → 选择开发板型号(本开发板对应Cyclone Ⅳ E系列,型号EP4CE22F17C6)

Next → 选择Simulation工具为ModelSim-Altera(之前已经和Quartus II一起装好了),语言为Verilog HDL

Next → 检查全部基础设置参数 → Finish,得到下图

File → New → Verilog HDL File

在空白区域写入Verilog工程代码,以下图为例,写好后点击保存,名称和工程名称相同即可

编写时序测试文件 → File → New → Verilog HDL File

编写完成后保存、编译。

现在开始用ModelSim进行RTL仿真。

右键左侧栏内工程名“my_first_fpga” → 选择“Settings...”

选中“Compile test bench”

点击一旁的"Test Benches..." → New → 填写刚刚保存的时序测试文件名称

点击File name右边的“...”,选中该时序文件

点击ADD后如图,之后一路点OK即可回到程序页面

回到程序页面后,设置完毕可以开始仿真。

点击Tools → Run Simulation Tool → RTL Simulation,即可启动ModelSim进行波形仿真

单击上方红色的圆形“stop”停止现有波形 → 摁Ctrl+A全选波形 → 摁Delete删除全部波形

最左侧sim工具栏右击工程名“my_first_fpga” → “Add Wave” → 单击波形栏左下角的“Toggle leaf names <-> full names”

全选信号 → Ctrl+G组合键实行自动分组 → 右击任意信号,选择Radix中的Unsigned → Ctrl+S保存信号

在最下面的命令窗口输入“restart” 后回车→ 点OK → 输入命令“run 0.1ms”后回车

点击左上角的Zoom Full(下图第三个),可以得到适当比例的波形图,然后可以通过前两个放大、缩小波形来细致观察

得到适合观察的波形如下图:

仿真后得到想要的结果,则可以进行管脚分配,为后续录入程序做准备

在工程界面工具栏选择“Assignments → Pin Planner”,在location一栏对应板子的输入输出管脚,输入相应管脚名称(注意大小写必须完全相同)

在烧录程序之前,还要编写SDC时序约束文件

在工具栏选择File → New → SDC file

写入时序约束文件如下图(绿色部分为注释,可不加),Ctrl+S保存为sdc文件

开始最后的全编译:

工具栏Processing → Start Compilation,成功后得到下图

编译成功后,就可以烧写到板子上了,工具栏Tools → Programmer

得到上图后,点击Hardware Setup,若板子的USB已经连好却找不到,则需要进行驱动,驱动方式引用下文:

USB Blaster驱动方法引用博文:Win7、Win8、Win10系统USB-Blaster驱动程序无法安装的解决办法

驱动完成后,显示如上图的USB-Blaster即可,点击左边的Add File,找到工程文件夹中out_files里面的编译完成后生成的sof文件:

点击open后,点击start,成功录入后如下图:

如果程序没错,则板子上便已经开始显示烧录的程序功能了。

-Finished-

2747

2747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?