详细看了这里的几篇spi时序的介绍,然后再总结了一下

http://blog.csdn.net/ce123/article/details/6923417

发现还是自己总结的比较好接受理解。

应该是几篇文章的混合版吧

1 spi定义

串行外设接口(Serial Peripheral Interface Bus,SPI),是一种高速的,全双工的,同步的通信总线,并且在芯片管教上只占用四根线。

优缺点

SPI接口具有如下优点:

1) 支持全双工操作;

2) 操作简单;

3) 数据传输速率较高。

同时,它也具有如下缺点:

1) 需要占用主机较多的口线(每个从机都需要一根片选线);

2) 只支持单个主机。

3) 没有指定的流控制,没有应答机制确认是否接收到数据。

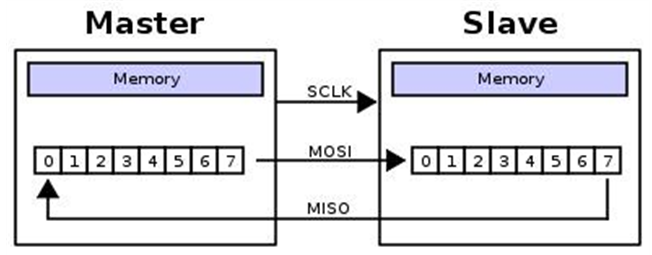

SCLK: 时钟信号,由主设备产生

MOSI: 主设备数据输出,从设备数据输入

MISO: 主设备数据输入,从设备数据输出

/SS: 从设备使能信号,由主设备控制

CPOL与CPHA的不同组合,将决定spi以哪一种时序进行传输。

CPOL:时钟空闲极性。CPOL=0,空闲SCLK电平为低电平,CPOL=1,空闲SCLK电平为高电平

CPHA:数据采样相位。CPHA=0,每个SCLK时钟周期的第一个跳变沿采样,CPHA=1,每个SCLK时钟周期的第二个跳变沿采样。

2 时序

在CPOL与CPHA下的四种不同时序

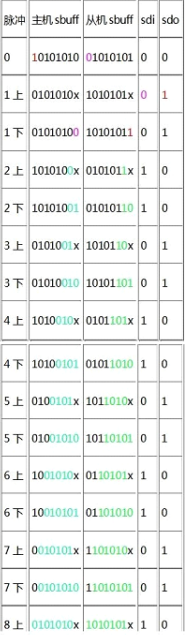

传输时序:如当CPOL=0,CPHA=0时,

时钟空闲为低电平,时钟的第一个跳变沿采样。

下降沿发送,上升沿接受,高位先发送。

主机将/SS拉低选择某个从机,根据主机要发送的数据,从高位到低位,依次将MOSI置为高或低,当SCLK出现上升沿时,主机读取MISO的高低电平,当SCLK出现下降沿时,主机通过MOSI输出高低电平。当/SS为高时结束。

注意:

主设备的MSB是在SCLK的上升沿的前办个时钟周期输出的与/SS无关

从设备的MSB是在/SS为低电平时,立刻输出的。与SCLK无关

3 数据传输:

在一个SPI时钟周期内,会完成如下操作:

1) 主机通过MOSI线发送1位数据(从MSB到LSB的顺序),从机通过该线读取这1位数据(放到低位,随着数据的接受不断的往高位移动);

2) 从机通过MISO线发送1位数据(从MSB到LSB的顺序),主机通过该线读取这1位数据(放到低位,随着数据的接受不断的往高位移动)。

这是通过移位寄存器来实现的。如下图所示,主机和从机各有一个移位寄存器,且二者连接成环。随着时钟脉冲,数据按照从高位到低位的方式依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

传输一个字节的实例。

399

399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?