5.1某机为定长指令字结构,指令长度16位;每个操作数的地址码长6位,指令分为无操作数、单操作数和双操作数三类。若双操作数指令已有K种,无操作数指令已有L种,问单操作数指令最多可能有多少种?

答:

对于双操作数,操作码长度为16-2*6=4位;

已知双操作数已有K种,所以留有(24-K)=16-K 个编码给单操作数。

对于单操作数,操作码长度为16-6=10位,可扩展位为6位;

已知无操作数已有L种,设单操作数有Y种,那么有:

L=[(24-K)*26-Y]*26

所以单操作数指令最多可能有Y=(24-K)*26-L/(26)

5.11讨论RISC和CISC在指令系统方面的主要区别

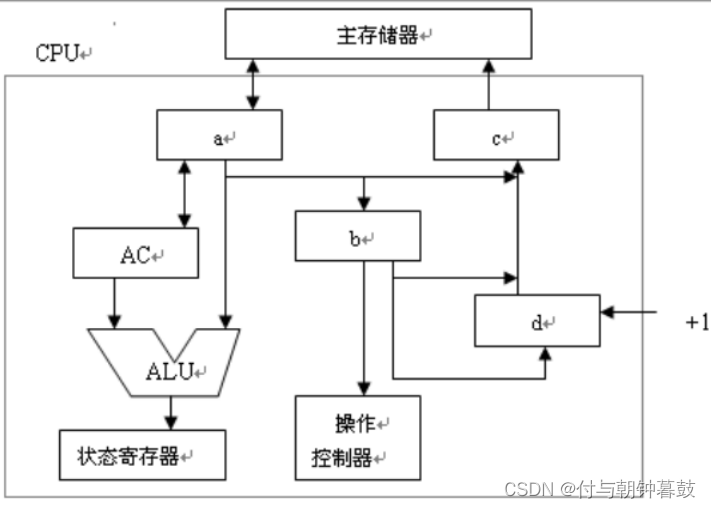

6.1、CPU 结构如下图所示,其中有一个累加寄存器AC 、一个状态条件寄存器和其他 4个寄存器,各部件之间的连线表示数据通路,箭头表示信息传送方向。

(1) 标明 4 个寄存器的名称。

(2) 简述指令从主存取出送到控制器的数据通路。

(3) 简述数据在运算器和主存之间进行存取访问的数据通路

答:

(1)a为 MDR,b为 IR,c为 MAR,d为 PC

(2) 取指令的数据通路:

PC→MAR → MM →MDR → IR

(3)数据从主存取出的数据通路(设数据地址为 X)

X→MAR → MM →MDR →ALU →AC

数据存入主存的数据通路(设数据地址为 Y)

Y →MAR,AC →MDR →MM

6.4微指令分为水平型微指令和垂直型微指令两类。水平型微指令可同时执行若干个微操作,所以执行指令的速度比垂直型微指令快。在实现微程序时,取下一条微指令和执行本条微指令一般是微操作进行的,而微指令之间是顺序执行的。实现机器指令的微程序一般是存放在只读存储器中的,而用户可写的控制存储器则由随机存储器组成。

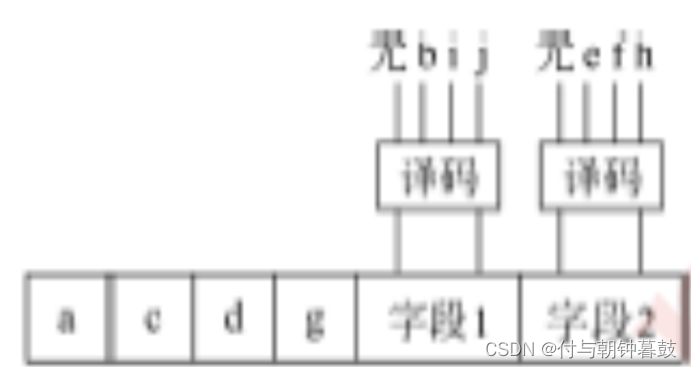

6.5某机有8 条微指令I1 ~ I8 ,每条微指令所含的微命令控制信号如表所列。a ~ j 分别代表10种不同性质的微命令信号,假设一条微指令的操作控制字段为8位,请安排微指令的操作控制字段格式,并将全部微指令代码化。

解:

因为微指令的操作控制字段只有8 位,所以不能采用直接控制法。又因为微指令中有多个微命令是兼容性的微命令,如微指令I1 中的微命令a ~ e ,故也不能采用最短编码法。最终选用字段编码法和直接控制法相结合的方法。将互斥的微命令安排在同一段内,兼容的微命令安排在不同的段内。b 、i 、j 这3个微命令是互斥的微命令,把它们安排在一个段内,e 、f 、h 这3 个微命令也是互斥的,把它们也安排在另一个段内。

字段1 的译码器输出对应的微命令为

00 无

01 b

10 i

11 j

字段2 的译码器输出对应的微命令为

00 无

01 e

10 f

11 h

将全部8条微指令代码化可以得到

I1 :

I2 :

I3 :

I4 :

I5 :

I6 :

I7 :

I8 :

6.13微机A和B采用不同的主频的CPU芯片,片内逻辑电路完全相同。

若A机主频是8MHz,平均指令执行速度为0.4MIPS;B机主频为12MHz,则:

(1)A机CPU的主振周期是多少微秒?

(2)A机的平均指令周期为多少微秒?

(3)B机平均指令执行的速度是多少MIPS?

解:

A机CPU的主频周期 =1/主频= 1/8MHz=0.125us

A机的平均指令周期 = 1/0.4MIPS=2.5us

A机的一个指令周期包含2.5/0.125=20个主频周期

B机的主频周期 =1/主频= 1/ 12MHz = 1/12(us)

因为微机A和B的片内逻辑电路完全相同,故B机的一个指令周期也包含20个主频周期,所以 B机的平均指令周期 = 20/12=5/3(us) ,B机的平均指令执行速度 = 3/5=0.6MIPS

6.15造成流水线阻塞的因素有多个。试列举3个造成流水线阻塞的因素,并给出其中两个的化解措施。

答:资源冲突(结构相关),数据冲突(重点),控制冲突都会造成流水线阻塞。

结构相关解决方式为:

1.前一个指令访存时,后一个指令暂停一个时钟周期(拖慢一拍),再执行。

2.增设一个功能部件

数据冲突解决方式为:

1.将遇到数据相关的指令以及后续指令,都暂停1到n个周期,直到数据相关问题消失后再执行

2.设置专用的通路,当数据发生数据相关的时候,第2条指令的操作数直接从数据处理部件读取而不需要等数据存入再读(这种技术又称数据旁路技术)

6.17机器加电后第一条执行的指令地址时怎样形成的?

答:CPU执行的第一条指令不在内存中,内存是由RAM组成的,而RAM不断电可以保存信息,一旦断电,RAM中的信息将会丢失,所以CPU要执行的第一条指令被固化在ROM中。由reset信号设置PC的初始值。

7.1计算机存储系统分哪几个层次?每一层次主要采用什么存储介质?其存储容量和存取速度的相对值如何变化?

答:

存储层次:

存储介质:

寄存器---电路 cache----SRAM 主存----DRAM 辅存----磁表面存储

存储容量和存取速度变化

7.3设某流水线计算机主存的读/写时间为100ns,有一个指令和数据合一的Cache,己知该Cache的读/写时间为10ns,取指令的命中率为98%,取数的命中率为95%。在执行某类程序时,约有1/5指令需要存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置

Cache后,与无Cache比较,计算机的运算速度可提高多少倍?

答:

有cache的情况:

平均访存时间=平均取指时间+平均取数时间

=(98%*10ns+(1-98%)*(10ns+100ns))+(95%*10ns+(1-95%)*(10ns+100ns))/5

=12ns+3ns=15ns

无cache的情况

平均访存时间=平均取指时间+平均取数时间

=100*1+100*1/5=120ns

速度提高倍数

120ns/15ns=8倍

7.7 一个组相联cache,由64个存储块组成,每组包含4个存储块,主存由8192个存储块组成,每块由32字组成,访存地址为字地址。问:

(1)主存和cache地址各多少位?地址映像是几路组相联?

(2)在主存地址格式中,区号、组号、块号、块内地址各多少位?

答:

(1) 主存单元数为8192*32=218,主存地址为18位。

cache单元数为64*32=211,cache地址为11位。

因每组包含4个块,所以是4路组相联

(2)主存地址:每块32字,即块内地址b=5位;

4路组相联,即块号r=2位;

组数为64/4=16,即组号c=4位;

主存块数/cache组数=8192/16=29,即t+r=9,所以区号t=7。

7.12某程序对页面要求访问的序列为P3P4P2P6P4P3P7P4P3P6P3P4P8P4P6。

(1)设主存容量为3个页面时,求FIFO和LRU替换算法的命中率(假设开始时主存为空)。

(2)当主存容量为4个页面时,上述两种替换算法各自的命中率又是多少?

(3)程序运行时,CPU访问主存的命中率会增加还是减小?

答:

当采用FIFO替换算法时,命中率为20%;当采用LRU替换算法时,命中率为40%。

当采用FIFO替换算法时,命中率为40%;当采用LRU替换算法时,命中率为60%。

(3)以上得出的命中率是访存改变页面时的命中率,根据局部性原理,在某页调入主存后,一般CPU会访问该页很多次(每次都命中),所以CPU访问主存的命中率会大大超过上述的数据。

3472

3472

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?