一、简介

SPI 协议是由摩托罗拉公司提出的通讯协议 (Serial Peripheral Interface),即串行外围设备接口,是一种高速全双工的通信总线。它被广泛地使用在 ADC、LCD 等设备与 MCU 间,要求通讯速率较高的场合。

二、物理层

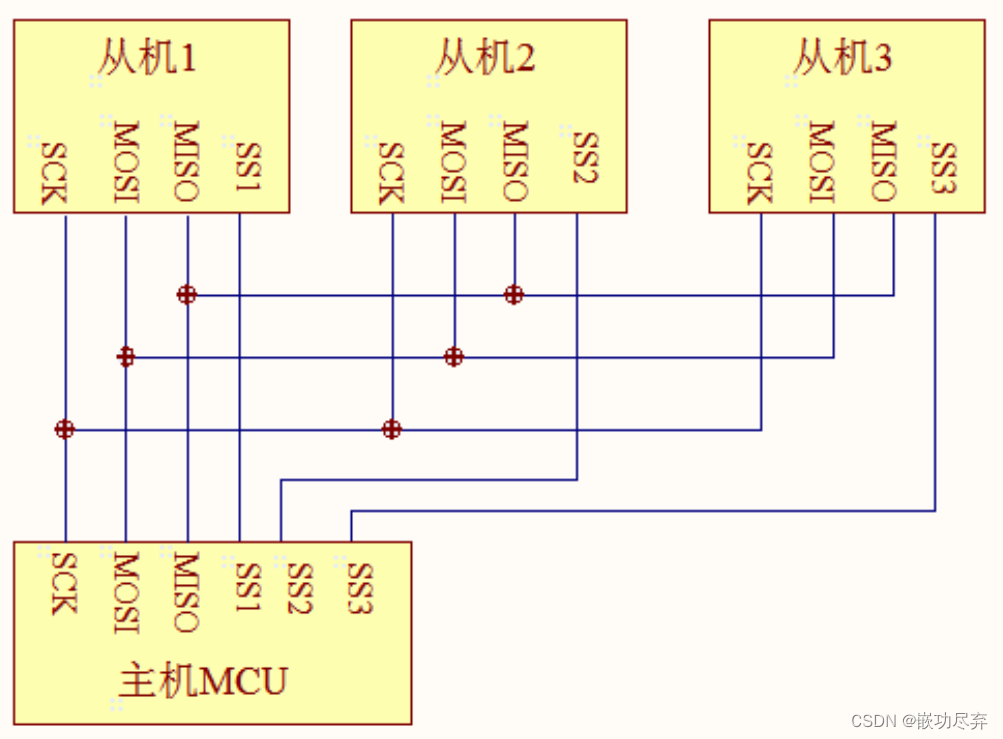

SPI 通讯设备之间的常用连接方式见下图

SPI

通讯使用

3

条总线及片选线,

3

条总线分别为

SCK

、

MOSI

、

MISO

,片选线为,它们的作用介绍如下:

(1) ( Slave Select):从设备选择信号线,常称为片选信号线,也称为 NSS、CS,以下用 NSS 表示。当有多个 SPI 从设备与 SPI 主机相连时,设备的其它信号线 SCK、MOSI 及 MISO 同时并联到相 同的 SPI 总线上,即无论有多少个从设备,都共同只使用这 3 条总线;而每个从设备都有独立的这一条 NSS 信号线,本信号线独占主机的一个引脚,即有多少个从设备,就有多少条片选信号 线。I2C 协议中通过设备地址来寻址、选中总线上的某个设备并与其进行通讯;而 SPI 协议中没有设备地址,它使用 NSS 信号线来寻址,当主机要选择从设备时,把该从设备的 NSS 信号线设置为低电平,该从设备即被选中,即片选有效,接着主机开始与被选中的从设备进行 SPI 通讯。所以 SPI 通讯以 NSS 线置低电平为开始信号,以 NSS 线被拉高作为结束信号。

(2) SCK (Serial Clock) :时钟信号线,用于通讯数据同步。它由通讯主机产生,决定了通讯的速率,不同的设备支持的最高时钟频率不一样,如 STM32 的 SPI 时钟频率最大为 f pclk /2 ,两个设备之间 通讯时,通讯速率受限于低速设备。(3) MOSI (Master Output , Slave Input) :主设备输出 / 从设备输入引脚。主机的数据从这条信号线输出,从机由这条信号线读入主机发送的数据,即这条线上数据的方向为主机到从机。(4) MISO(Master Input, , Slave Output) :主设备输入 / 从设备输出引脚。主机从这条信号线读入数据,从机的数据由这条信号线输出到主机,即在这条线上数据的方向为从机到主机。

三、协议层

与

I2C

的类似,

SPI

协议定义了通讯的起始和停止信号、数据有效性、时钟同步等环节

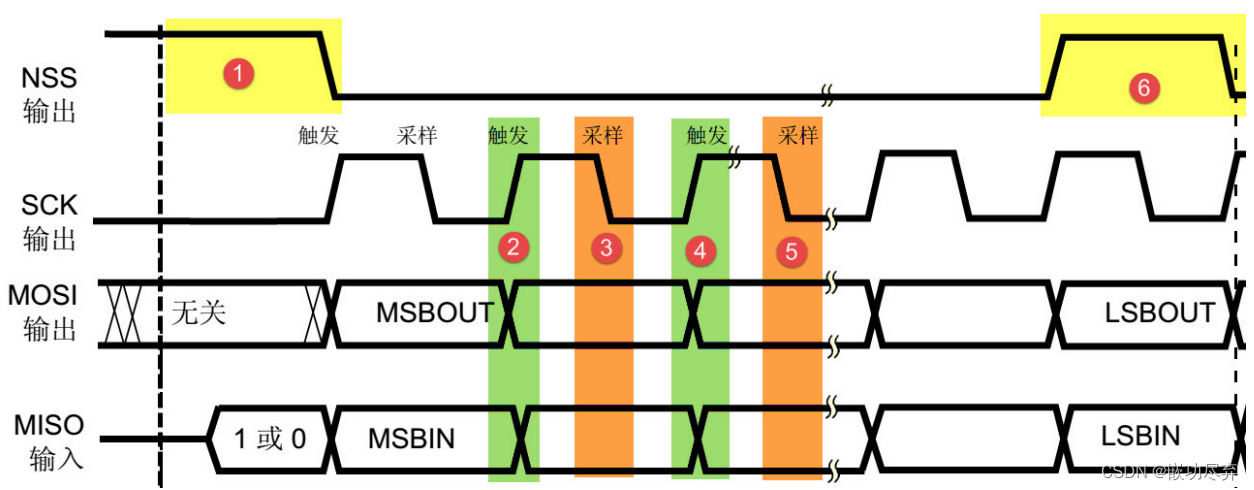

这是一个主机的通讯时序。

NSS

、

SCK

、

MOSI

信号都由主机控制产生,而

MISO

的信号由从机产生,主机通过该信号线读取从机的数据。

MOSI

与

MISO

的信号只在

NSS 为低电平的时候才有效,在

SCK

的每个时钟周期

MOSI

和

MISO

传输一位数据。

3.1 起始和停止信号

在上图

中的①标号处,

NSS

信号线由高变低,是

SPI

通讯的起始信号。

NSS

是每个从机各自独占的信号线,当从机在自己的

NSS

线检测到起始信号后,就知道自己被主机选中了,开

始准备与主机通讯。在图中的⑥标号处,

NSS

信号由低变高,是

SPI

通讯的停止信号,表示本次通

讯结束,从机的选中状态被取消。

3.2 数据有效性

<

https://blog.csdn.net/2301_76655007/article/details/137338978?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522171214204316800186566742%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=171214204316800186566742&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~first_rank_ecpm_v1~rank_v31_ecpm-1-137338978-null-null.142^v100^pc_search_result_base2&utm_term=IIC%E9%80%9A%E4%BF%A1%E8%AF%A6%E8%A7%A3%E2%80%94%E2%80%94STM32%20IIC%E5%AE%9E%E9%AA%8C%28%E9%87%8E%E7%81%AB%E6%8C%87%E5%8D%97%E8%80%85%29&spm=1018.2226.3001.4187

https://blog.csdn.net/2301_76655007/article/details/137338978?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522171214204316800186566742%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=171214204316800186566742&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~first_rank_ecpm_v1~rank_v31_ecpm-1-137338978-null-null.142^v100^pc_search_result_base2&utm_term=IIC%E9%80%9A%E4%BF%A1%E8%AF%A6%E8%A7%A3%E2%80%94%E2%80%94STM32%20IIC%E5%AE%9E%E9%AA%8C%28%E9%87%8E%E7%81%AB%E6%8C%87%E5%8D%97%E8%80%85%29&spm=1018.2226.3001.4187 最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

299

299

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?