(实验文件和实验报告私信,知识付费,只需一杯奶茶钱~~~)

背景知识

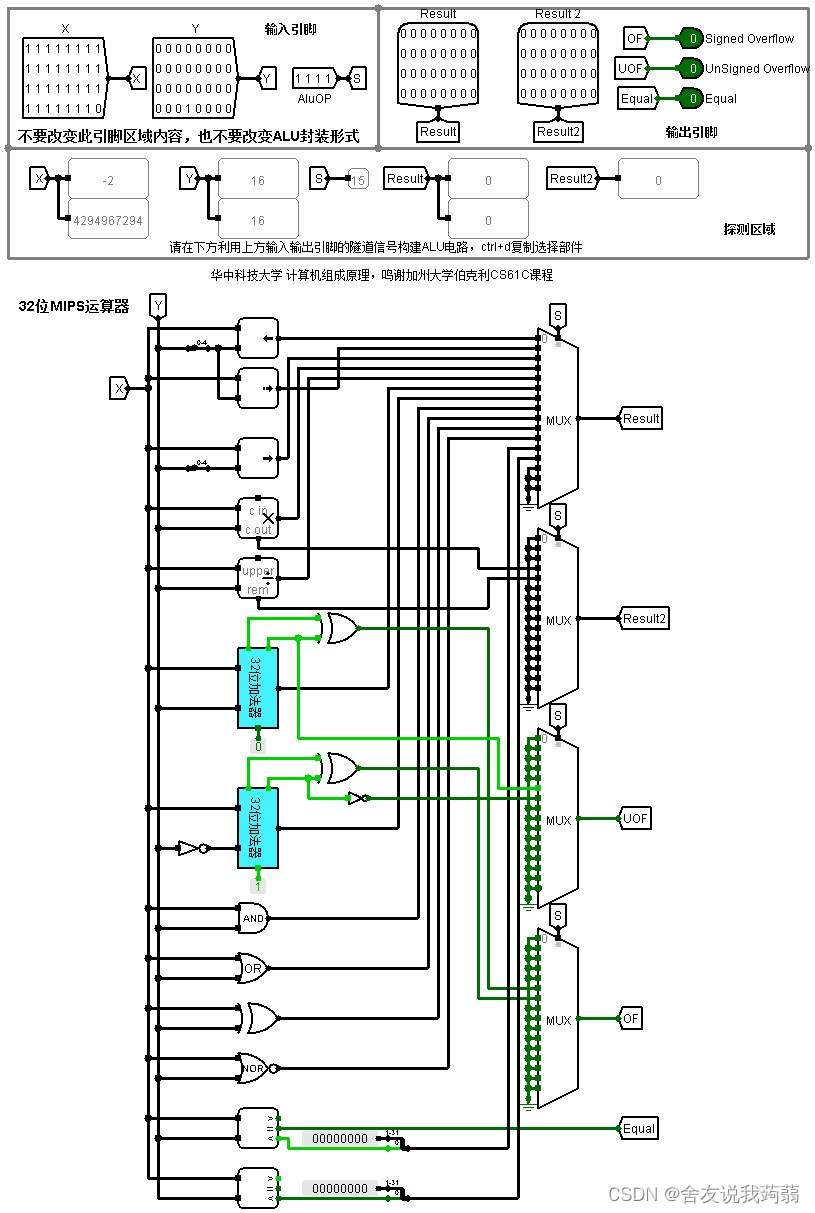

算术逻辑运算单元(ALU)是计算机的核心部件,实现的基本功能包括加、减、乘、除等算术运算以及与、或、非等逻辑运算,实现上述算术以及逻辑运算功能的部件就是构造ALU的基本逻辑单元部件。ALU模块的输入输出为:X、Y为输入数,S为运算选择控制端,Result(及Result2)为运算结果,OF/UOF为有符号溢出/无符号溢出,Equal为比较相等。

实验要求

在给定的子电路中,设计CLA74182、4位快速加法器,扩展组成32位加法器,在ALU电路中连接剩余的线路,得到线路准确的ALU单元。

实验过程

利用Logisim软件打开工程文件alu.circ,完成74182、4位加法器,扩展组成32位加法器。

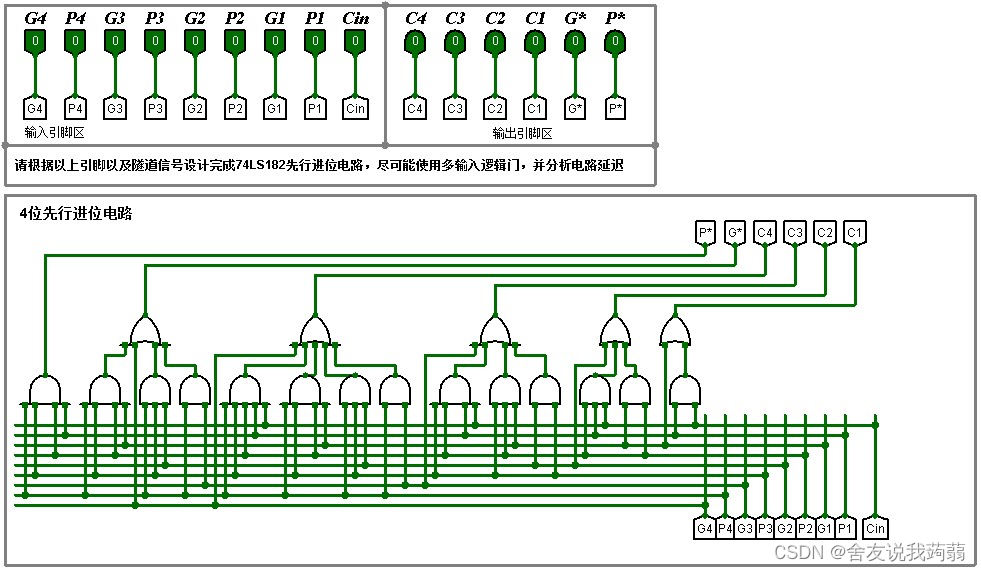

一、74182先行进位

全加器虽然弥补了半加器无法实现多位相加的缺陷,可从前面的实验不难看出,高位进行运算时必须等待低位的进位信号,导致延迟的增加。

而当机器数数位固定时,各位的进位信号可通过更复杂的设计直接得到,无需等待低位给出进位信号,因此出现了先行进位电路,又称超前进位加法器( Carry Lookahead Adder )。

由全加器可知:

Ci+1 = Ai · Bi + Ai · Ci + Bi · Ci = Ai · Bi + ( Ai + Bi ) · Ci

设:

生成信号(Generate):Ai · Bi

传递信号(Propagate):Ai + Bi

则:Ci+1 = Gi + Pi · Ci

C4-C1、G*、P*为输出,P4-P1、G4-G1、Cin为输入,其逻辑表达式为:

C4=P4 P3 P2 P1 Cin + P4 P3 P2 G1 + P4 P3 G2 + P4 G3 + G4

C3=P3 P2 P1 Cin + P3 P2 G1 + P3 G2 + G3

C2=P2 P1 Cin + P2 G1 + G2

C1=P1 Cin + G1

成组进位生成函数:G*=P4 P3 P2 G1 + P4 P3 G2 + P4 G3 + G4

成组进位传递函数:P*=P4 P3 P2 P1

4位先行进位74182电路如图所示:

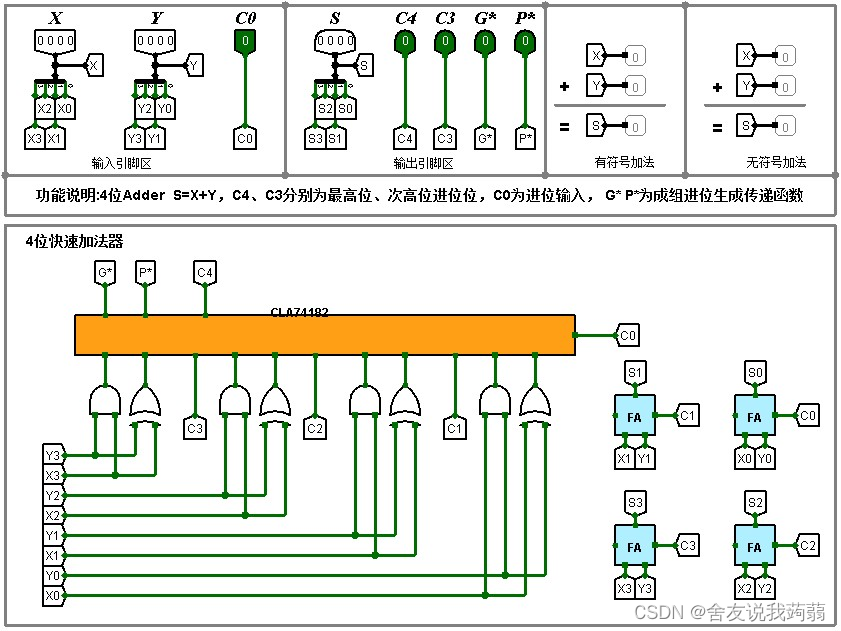

二、4位快速加法器

4位快速加法器使用了前面设计的182,182的输入Gi、Pi由Xi、Yi产生。

Si=Xi⊕Yi⊕Ci-1

Gi=XiYi

Pi=Xi⊕Yi

4位快速加法器电路如图所示:

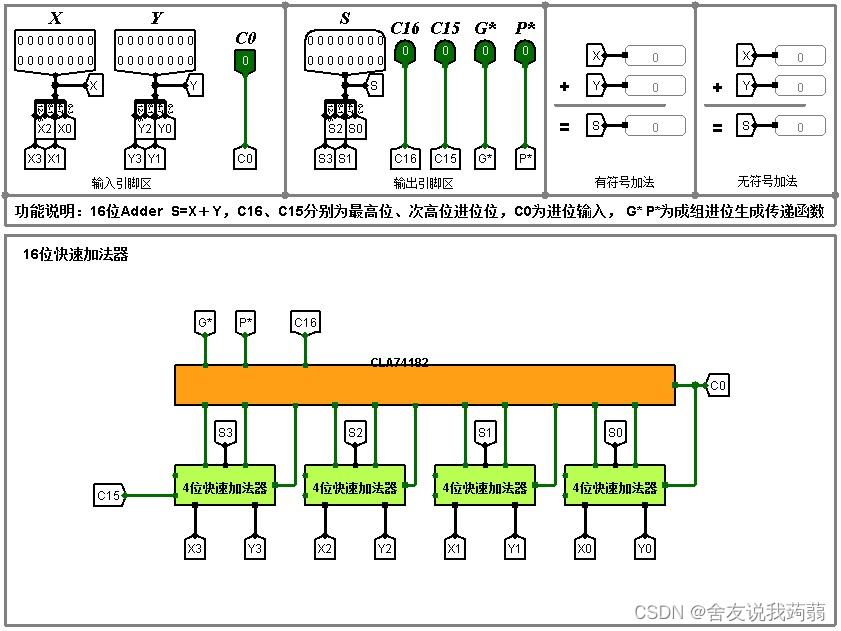

三、扩展组成16位快速加法器

1、利用四位先行进位电路和四位快速加法器构造十六位组间先行进位,组内先行进位快速加法器。

2、相当于由4位扩展为16位,进一步的升级。重点理解扩展的含义。

3、注意:C15接口为次高位进位。并且每4位的进位C1、C2、C3、C4是由74128的上端接口连到4位快速加法器的进位输入端。

16位快速加法器电路如图所示:

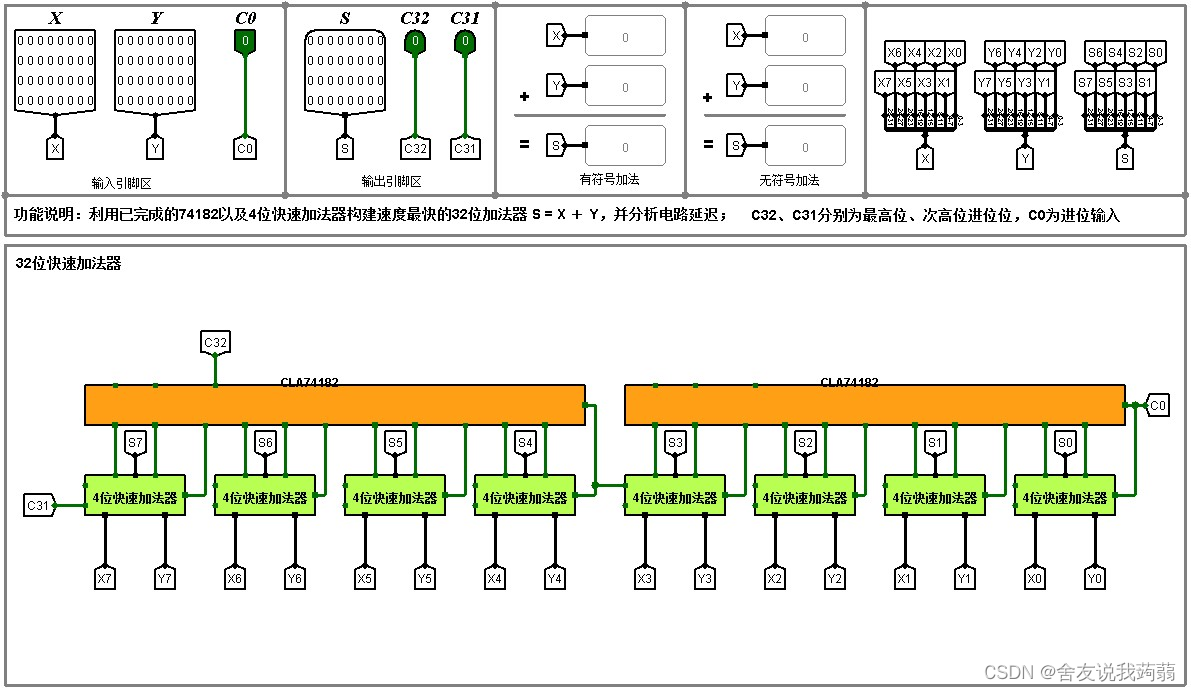

四、扩展组成32位快速加法器

可能方案:

-

2个16位加法器直接串联,C16 信号采用下层的进位输出

-

2个16位加法器直接串联,C16 进位输入采用上层的进位输出

-

在16位快速加法器的基础上再增加一级组间先行进位电路,类似6464位快速加法器的方法。

32位快速加法器电路如图所示:

五、算术逻辑运算单元ALU

“☆算术逻辑运算单元ALU”子电路需要按照运算功能添加相应的功能部件,在对应子电路中进行线路的连接,并在“★ALU自动测试”子电路中进行测试。

算术逻辑运算单元ALU电路如图所示:

ALU引脚功能:

X、Y,32位操作数

AluOP运算器功能码

Result运算结果

Result2ALU结果第二部分用于乘法指令结果的高位或除法指令的余数位

OF有符号加减运算的溢出标志

UOF无符号加减运算溢出标志(溢出条件为加法和小于加数,减法差大于被减数)

Equal操作数相等则为1

运算器功能码:

0000,逻辑左移,Y取低5位作为移位次数

0001,算术右移,Y取低5位作为移位次数

0010,逻辑右移,Y取低5位作为移位次数

0011,无符号乘法

0100,无符号除法

0101,Result=X+Y,并设置OF/UOF(有符号溢出/无符号溢出)

0110,Result=X-Y,并设置OF/UOF(有符号溢出/无符号溢出)

0111,按位与

1000,按位或

1001,按位异或

1010,按位或非

1011,有符号比较

1100,无符号比较

实验总结

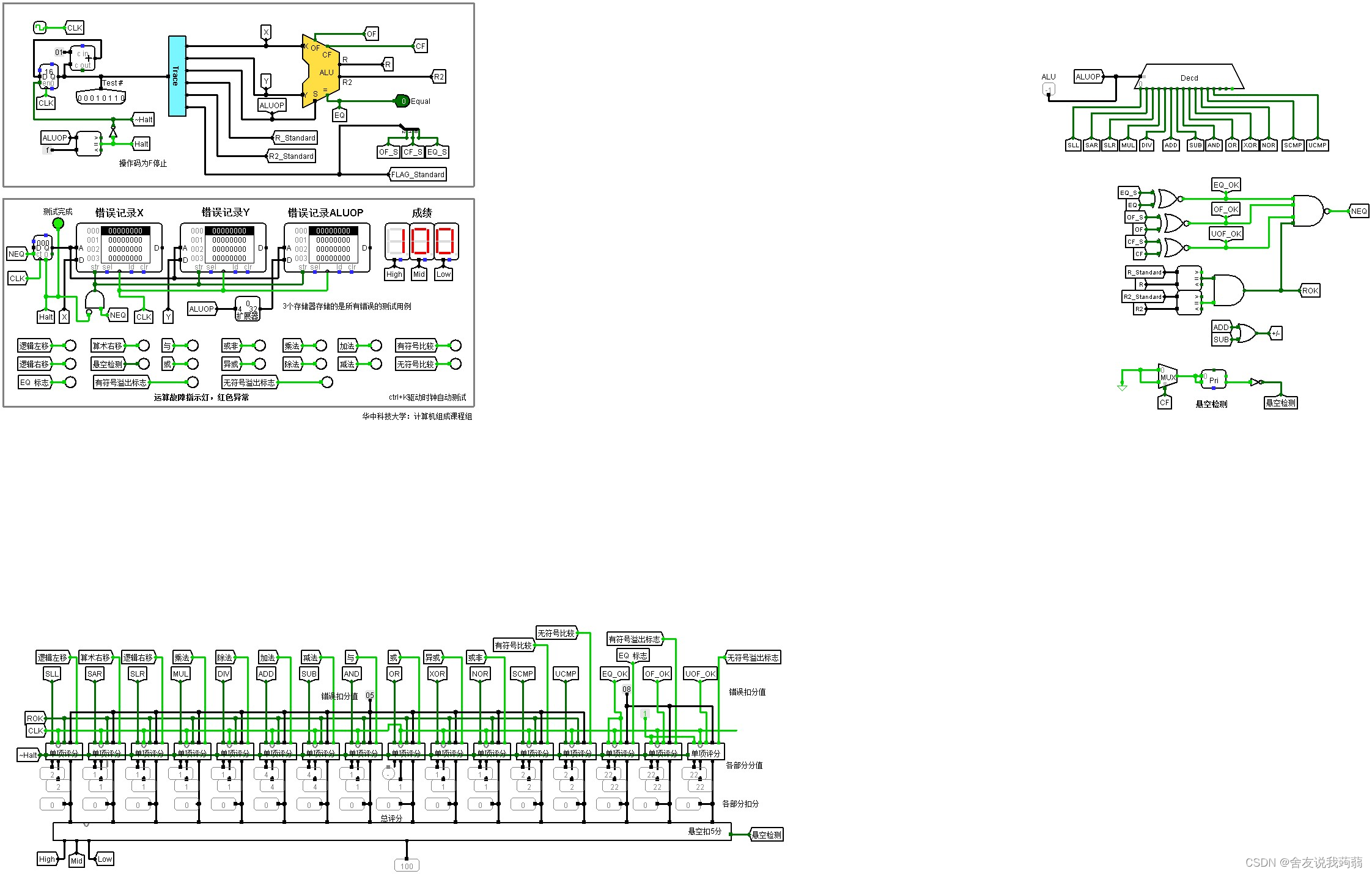

★ALU自动测试电路图如下:

运算结果的溢出的判断:

无符号的加法溢出判断: 看最高位是否有进位1。

无符号的减法溢出判断: 看最高位是否有进位0。

有符号的加减法溢出判断:符号位的进位C32, 最高数值位的进位C31

V = C32

C31

当 V = 0时表示没有溢出

当V = 1时表示有溢出

本文介绍了如何在Logisim软件中设计和扩展4位加法器,实现先行进位和快速加法,最终构建32位算术逻辑运算单元(ALU),涉及进位逻辑、溢出判断和多种运算功能的实现。

本文介绍了如何在Logisim软件中设计和扩展4位加法器,实现先行进位和快速加法,最终构建32位算术逻辑运算单元(ALU),涉及进位逻辑、溢出判断和多种运算功能的实现。

990

990

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?