修改SCH文件的图纸大小,通过右侧的property 选sheet大小 由A4→A3即可

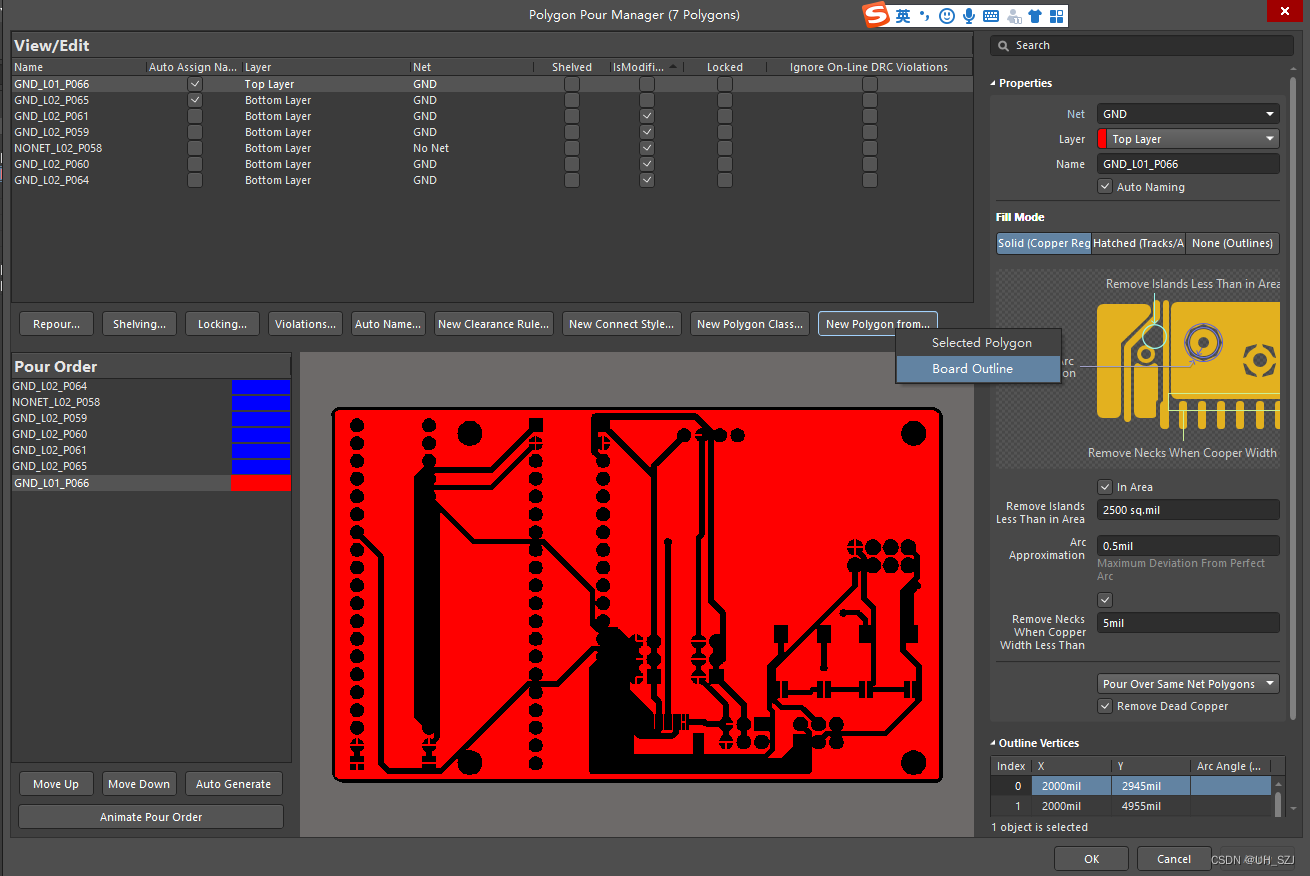

铺铜选项介绍

常用快捷键

“shift + 空格” 改变走线模式

shitf+空格,切换到圆角走线形态,再按“,”或“.”可改变R半径.

0、原理图下切换电气栅格快捷键:Shift+E

1、shift+C 去除阴影 /多选

2、T+G 打开封装管理器

3、N 隐藏(hide) 暂时隐藏飞线/显示n

4、2;3; PCB模式下的2维模式和3维模式快捷键

5、Ctrl+D 调出隐藏设置面板

6、Ctrl+W 快捷布线

7、shift+右键 旋转三维图

8、小键盘 * 直接放过孔

9、Ctrl+shift+G PCB模式下设置栅格大小

10、shift+Ctrl+X 分屏模式下设置交叉选中模式 也可以通过Design>corss select mode 来开启

11、L 可将TOP-layer的器件移动到底层,首先先选中元器件,左键按住不松,再按下L即可

12、空格 旋转器件90°

13、X、Y 水平翻转、垂直翻转器件 使用方法同L

14、Ctrl+M 测距快捷键

15、shift+s 切换显示层,单层显示等n

16、T+G+M 快捷敷铜

17、单独按L 可打开层管理窗口,可以查看层分布

18、AD中的port 可以跨原理图进行连接,但使用时需要指定反向,一般一发一收,但也可以设置成双向

19、shift 按住+cursor hover 在布线上,可查看PCB中的通路

20、bom表 点击report>bill of materials>>properties>>colums 选择相应的group进行排列 最后点击export 导出文件

基本步骤

见图片

需要注意的问题

1、从立创EDA中导出的原理图文件需要先(打开-保存为-关闭-重新打开)才能显示出原理图(20年旧版)

2、一般在高速线路中,信号线的布局需要进行等长处理,并按照相关数据手册或标准进行布线,以防止高频噪音对信号的完整性造成影响

3、变更3D模式下的板子颜色 ,先进入层管理,点击view option ,改变TOP solder Mask即可

4、关于泪滴的作用

1、避免电路板受到巨大外力的冲撞时,导线与焊盘或者导线与导孔的接触点断开,也可使PCB电路板显得更加美观

2、焊接上,可以保护焊盘,避免多次焊接时焊盘的脱落。

3、生产时可以避免蚀刻不均,以及过孔偏位出现的裂缝等。

4、信号传输时平滑阻抗,减少阻抗的急剧跳变,避免高频信号传输时由于线宽突然变小而造成反射,可使走线与元件焊盘之间的连接趋于平稳过渡化。

-

怎么添加泪滴

-

5、问题记录

1、地线一般不需要额外处理,通常画地线时,地线的宽度要大于电源线的宽度大于普通走线的宽度。但实际应用过程中,因为MCU的引脚通常紧凑又窄小,所以地线宽度应和普通走线一样,避免过宽而无法自动布线。

6、PCB View Configuration

可以让板子层次更为清晰

绘制4层板

1、点击layer stack Manager

2、右键点击insert layer below:选择signal或plane

signal可正常布线,后续再添加敷铜,也可以直接添加plane。

常用分布顺序 Siganl_1(Top),POWER(Inner_1),GND(Inner_2),Siganl_2(Bottom)

3、中间层signal层进行布线,和放置vias

出现过问题,在放置via,并手动连线时,出现规则判断错误的问题,后通过fanout操作解决这以问题,但不知道具体影响。

扇出前需要设置规则,建立相应区域或选择器件

扇出主要用于BGA或其他具备密集触点的器件,批量给引脚打过孔,并引出导线。

Gerber文件生成-

【转载】(嘉立创建议 )Altium Designer生成Gerber文件的设置_嘉立创eda导入gerber-CSDN博客

单独网络覆铜

选择solid region 不要选择Polygon Pour

打样前检查

1、多层板时,内部信号层的信号线需要注意避开 开槽位置。

2、封装与实物是否匹配,引脚序号是否对应

3、电气规则判断务必通过后才能进行打样

4、设计需求需要明确,设计之前需要罗列

5、电源线宽是否为15mil以上

6、DIP封装孔径是否大于30mil

7、三极管的各引脚与封装序号是否对应

8、PCB是否需要额外开关控制电源

关于板子上的USB

以STM32为例,所画板子中添加的USB接口一定要(尽量)能够进行程序的烧录,一定要注意添加相应的拨码开关对相应的通信进行转换,CH340芯片在常态下会钳位通信引脚至高电平或低电平,所以在串口1通信其他传感器时需要断开与CH340的连接(通过拨码开关或跳线帽选择,实现分时复用串口)。

4477

4477

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?