有关逻辑门电路

有关高级逻辑门电路

编码器和译码器

触发器和计数器

1,有关逻辑门电路

CMOS管,NMOS管,OC,TTL等等,都是由三极管和MOS管,加上电源电阻二级管组成的

三极管,分为左边的基极(信号),对于NPN结三极管(最常见)上面的集电极(供电),下面的发射极(接地),以及右边最后被放大或缩小的信号

但是对于PNP结三极管,下面的发射极(供电),上面的集电极接地。

但TTL中有种接受端为两个口,处于接地状态,只要有一个是低电压,对面的电流就会反相流过来流入地面,起不到接受端输入高电压的效果

左边的信号电压太大,上面的发射极电流就直接导入地面,发射极电流导入右边的就少了,

因为不需要,那么这时就是饱和了,基极电流直接大于集电极电流

左边的信号电压太小,上面的发射极电流就不导地,大部分流入右边,右边没有信号波动,

因为基极因为电压达不到0.7v,电流太小,被截止了

左边的信号电压在放大区,上面的发射极电流就下面和右边都流入,

同时左边电压大于0.7v,基极电流小于集电极电流,信号被供电放大,放大系数为集电极电流/基极电流

三种状态,由这些电压电流电阻确定,但是三极管是电流控制的元器件

MOS管,又叫场效应管,分为栅极,源极和漏极,构成了P沟道和N沟道(衬底为箭头指向内外)

N沟道,栅极连接左边的外部电源,与源极产生电位差,大于Vt后,源极接地,电流从漏极流向源极(通常采用正电源)

N沟道衬底连接电路中的最低电位

P沟道,栅极连接左边的外部电源,与源极产生电位差,大于Vt后,源极接电压,电流从源极流向漏极(通常采用负电源)

P沟道衬底连接电路中的最高电位

最后也就是看栅极有没有电压来,同时源极漏极电压小不小,这样左边小于右边电压就是截止状态,导不通就是高电阻,Vcc给这边的电压就打,F端的分压就大

卡诺图是对逻辑表达式用二维表来表示,目的为了优化逻辑表达式

比如一个逻辑电路,用逻辑表达式表示就是Y=AB'+A'C+BC+C'D,可以先画一个二维表,AB为列,CD为行,把表达式中含有表格属性的空格填上1,

这样卡诺图就做好了,再以1,2,4,8(2的指数方)的形式上涨来确定圈的大小,来圈住这些1,根据圈子来重新定义逻辑表达式。

这样就做到了卡诺图的简化。

逻辑表达式中

乘法是与,加法是或,上面有横线是非

逻辑AND表达式:F=A⋅B

逻辑OR表达式:F=A+B

逻辑NOT表达式:F= A

如何优化逻辑表达式

举个例子F=AB'+BC+ABCD+B'=B'(1+A)+BC(1+AD)=B'+BC=B'(1+C)+BC=B'+C(B'+B)=B'+C

先是合并同类项,然后消除冗余因子,比如(1+A),(1+AD)

2,有关高级逻辑门电路

TTL,与非门,最为经典,但是不同组合还会组成或非,与或等等

由T1,T2,D3,T4,T5组成(T是三极管,D是二极管,T1是双发射极三极管)

1,当T1两个发射极有一个是低电平,或者两个都是低电平时,来自外部的Vcc就会顺着T1流向地面,电压没有被使用到,

这时T1基极处电压很小,没法导通T2,T5(总共1.4v),加上T1集电极就是2.1v,可以把它们看成开路,

由于这个Vcc它还与T2,T5那边的线并联,电压可以从它们那边入手

因为T2开路,所以不管Vcc和T4之间的电阻,T4基极的电压和Vcc一样,

这样这份电压就可以导通T4和D3(总共1.4v),F输出高电平1(2.8~3.6)

2,当T1两个发射极都是高电平时 (比如3.6v),T1那边的电压就是4.3v了,

这时就可以导通T2,T5(二次钳位),把它们当成短路

这个时候T4基极的电压是Vbe5+Vce2<1.4v,无法导通T4和D3,这时F输出低电平0(0.1~0.3)

3结:在输入0.7v~2.8v之间,T2和T5逐渐可以导通,F电压极速的下降,但是在输入电压为0.7v~1.4v之间有噪声容限,

这时T1逐渐导通,在这之间F电压下降的小,还处于高电压状态

到了1.4v后,就是T2和T5导通,F电压会极速流失

OC门属于TTL电路大类中的一个分支

当两个F想要线与时,TTL不允许,因为直接连线,上面的电流太大会把下面的三极管经过F2给击穿烧毁

这时OC门就可以实现线与,因为它在TTL电路的基础上,把T4,D3给去了,换成电阻,

这样就可以实现高电平和线与

TSL三态门,基于TTL改进的电路,在TTL电路底下接一个电路,如果输入端EN=1,则底下的电路不起作用,TTL电路正常运行

如果EN=0,则底下的电路T8导通,Vcc的电压顺着T4T8那条线流失了,这时如果T2和T5也没导通,那么F就是高阻抗(悬浮导线)

多个三态门可以由一条总线连起来,连接任意多门

CMOS和NMOS管都是集成电路,但是CMOS是N,P两沟道都有的mos管组合,NMOS只有N沟道mos管

这里就是看栅极和源漏极的电压符不符合,有没有导通,没有就是截止状态,电阻大,分压也大,反之电阻小,分压小

注意CMOS电路也可以下面接个电路EN,构成三态门

重点在于构造出逻辑表达式

3,编码器和译码器

编码器是一种将输入数据转换为特定格式的模块

译码器是一种将已编码数据重新转换回原始格式的模块

编码器就是多端输入,少端输出,比如二进制转十进制

译码器就是少端输入,多端输出,比如十六进制转二进制

典型的像74ls138译码器和75ls151编码器,太多了不做赘述,总结就是输入决定输出,没有难度

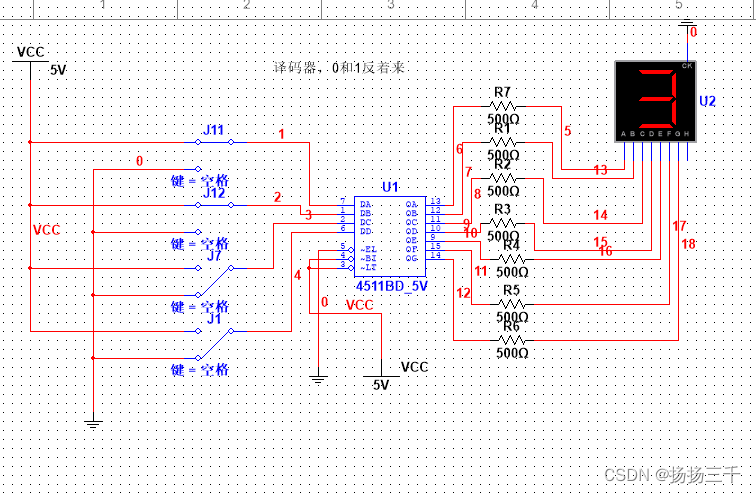

这就是一种译码器,这里0和1是反着来的。

4,触发器和计数器

触发器和计数器都可以组成时序逻辑电路

因为它们输入端之间会相互影响的同时,输出端也可以影响输入端,

而且关键在于上个时刻的状态会记住,从而影响下一个时刻的输出

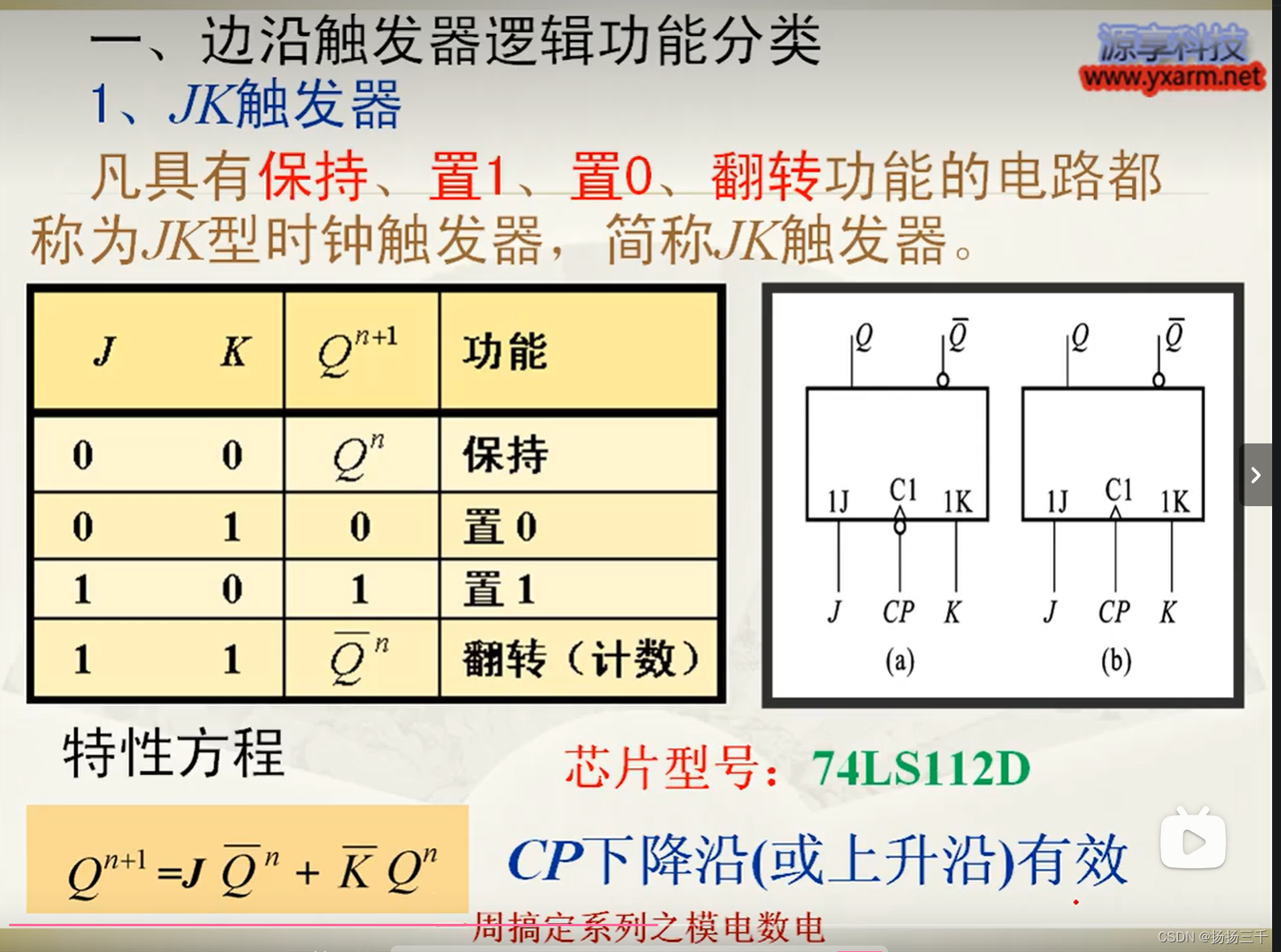

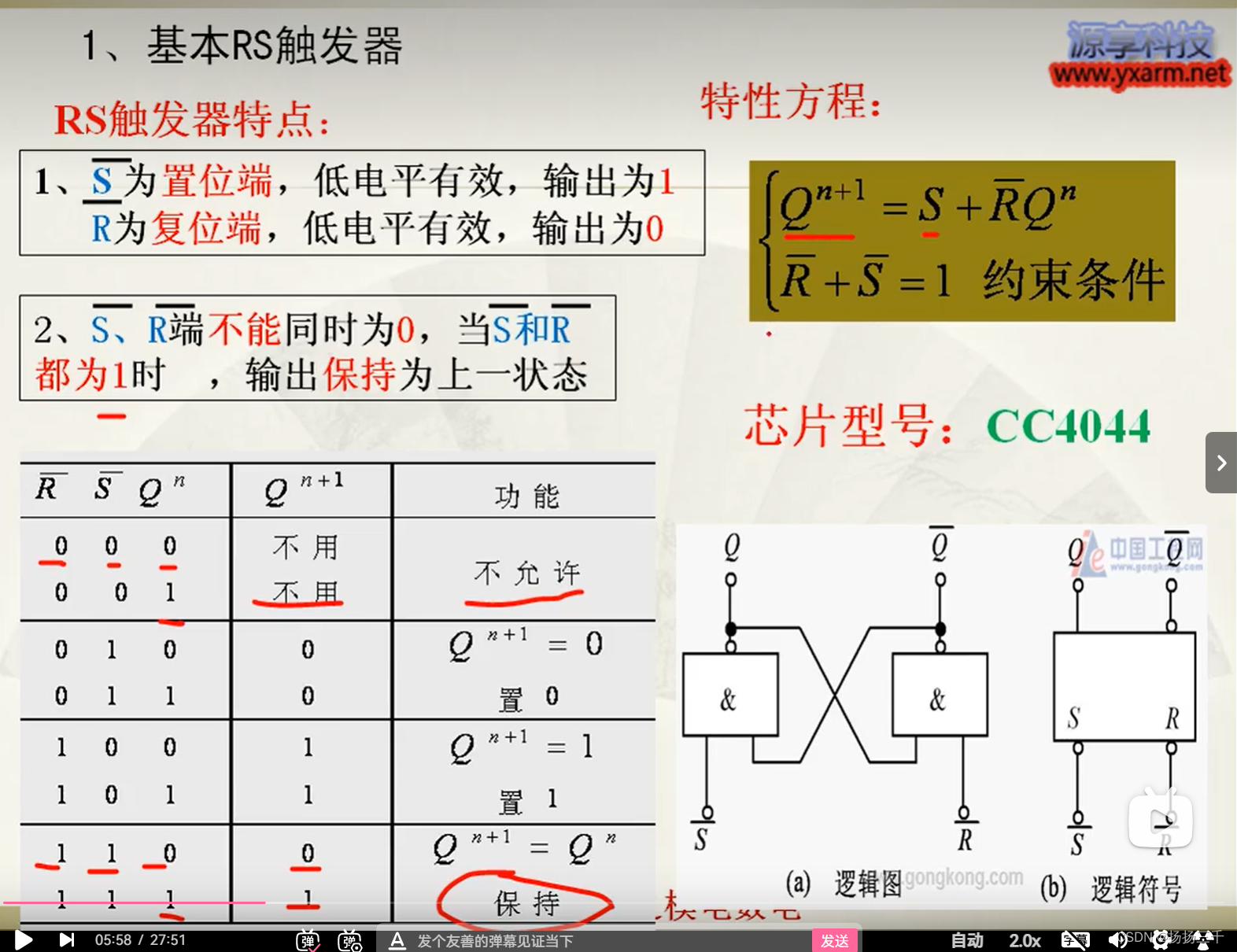

常见的触发器有RS,JK,D,T型,

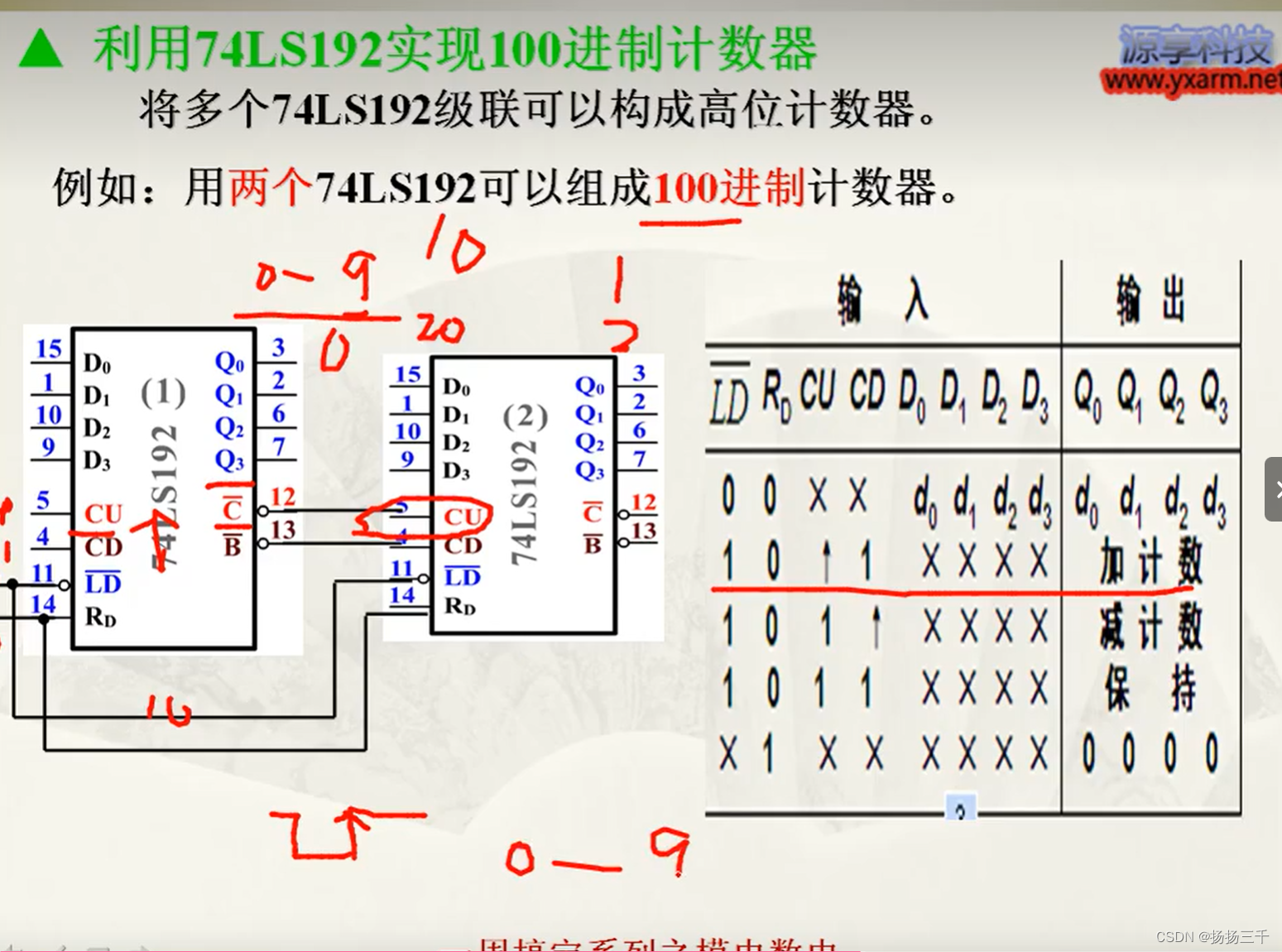

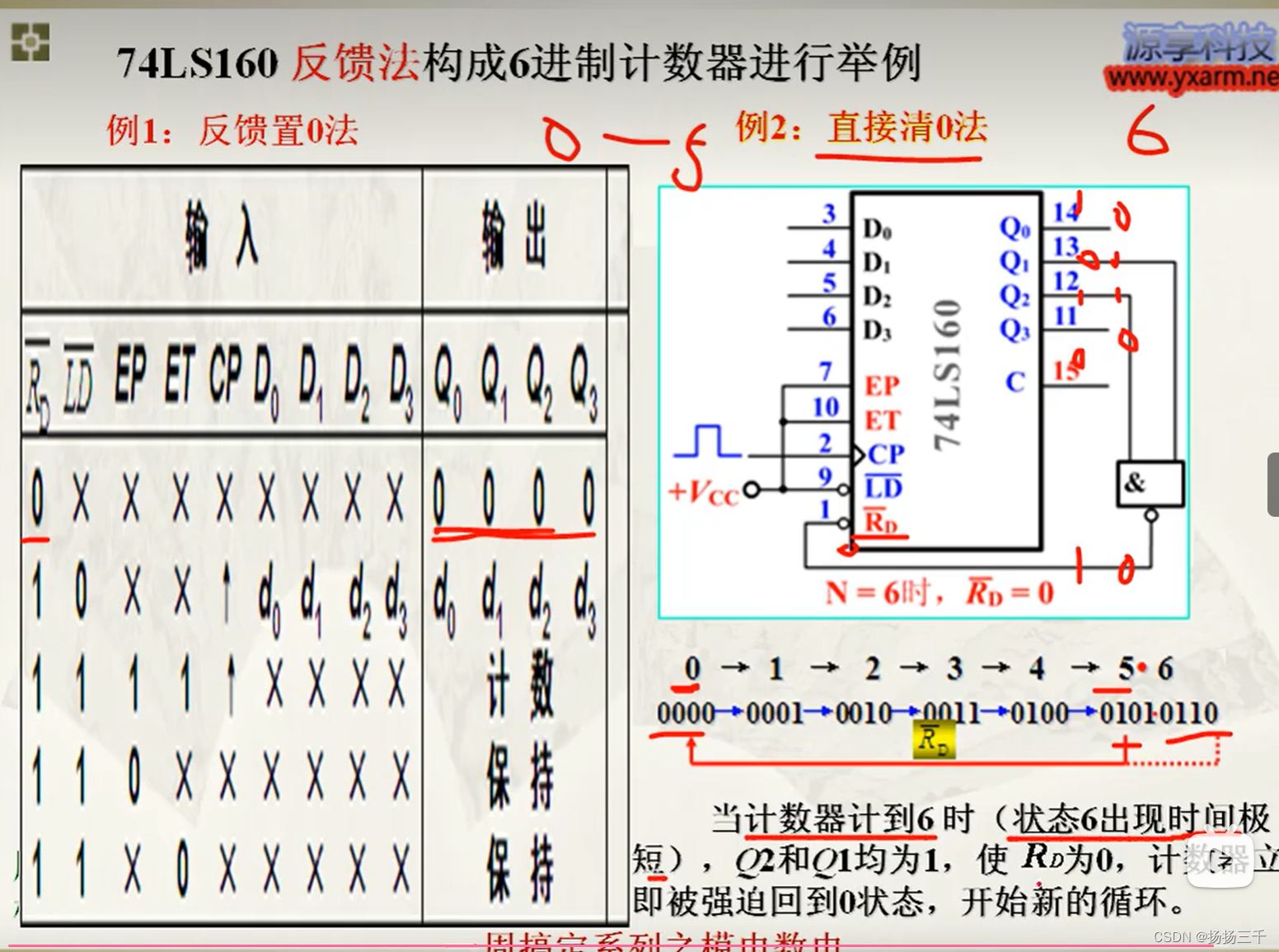

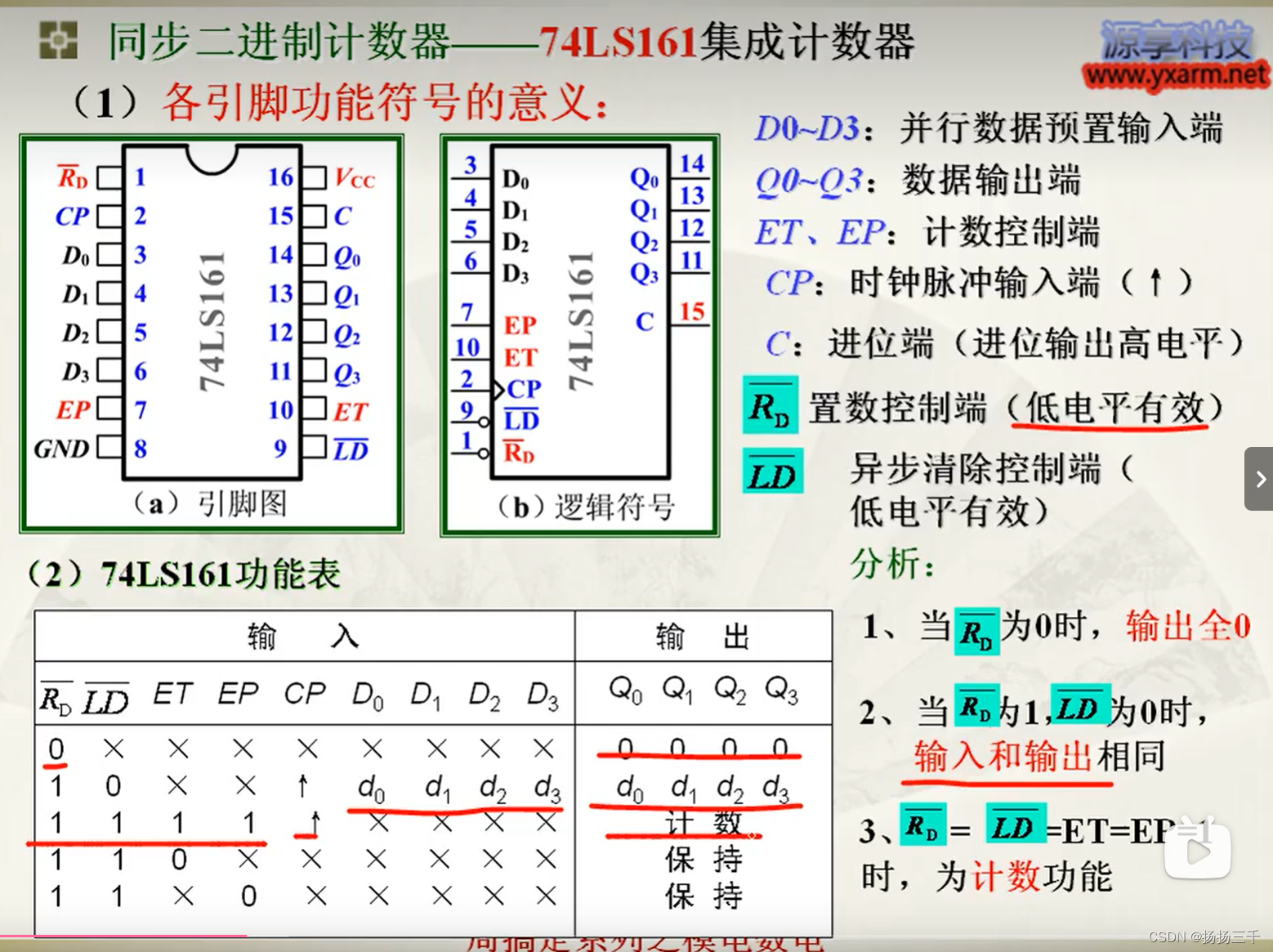

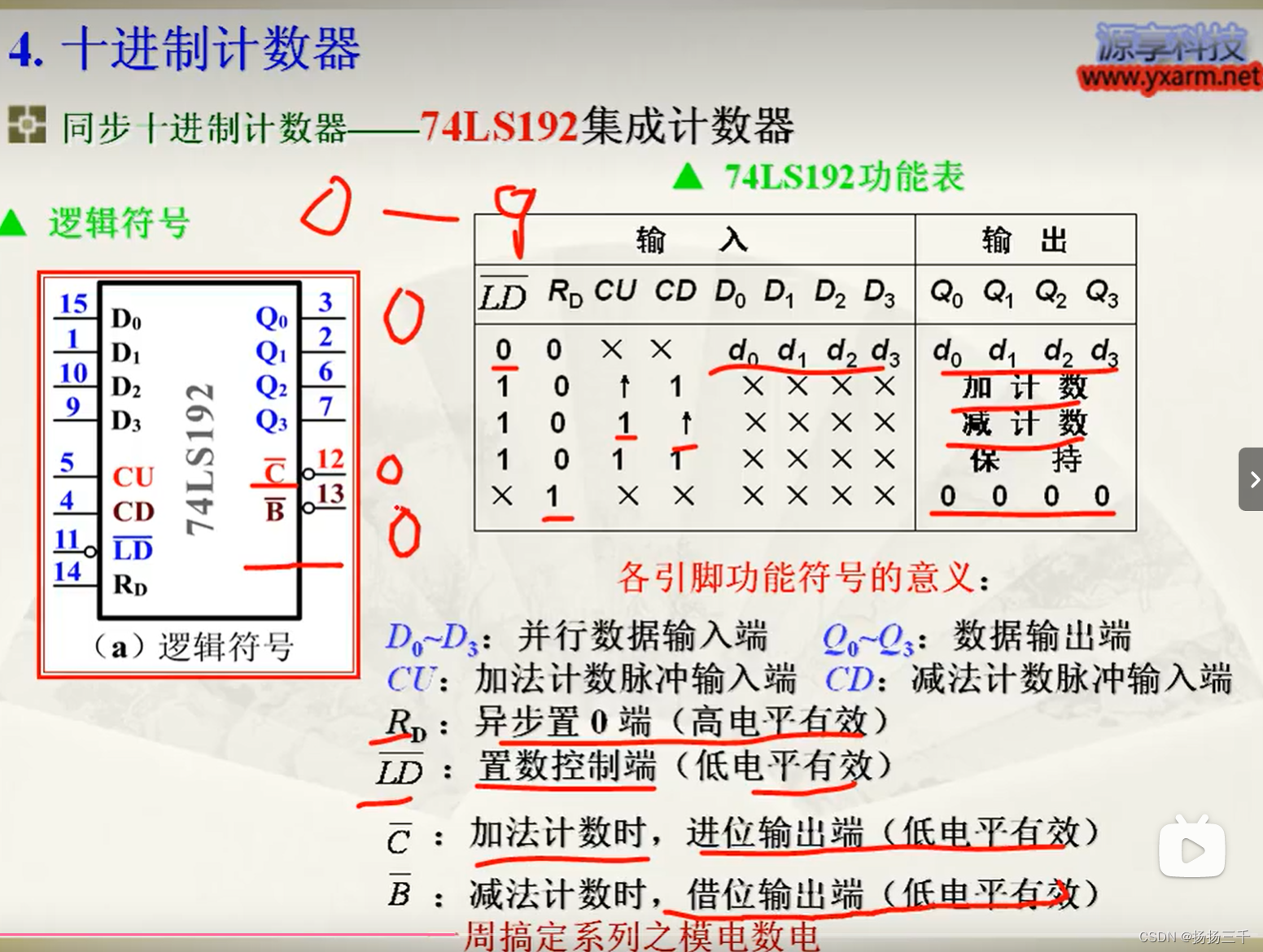

常见的计数器,像74ls161等,可以构成很多进制的计数器

具体学习建议看图+实操,因为记住了容易忘,可以在设计数字电路的时候去学习

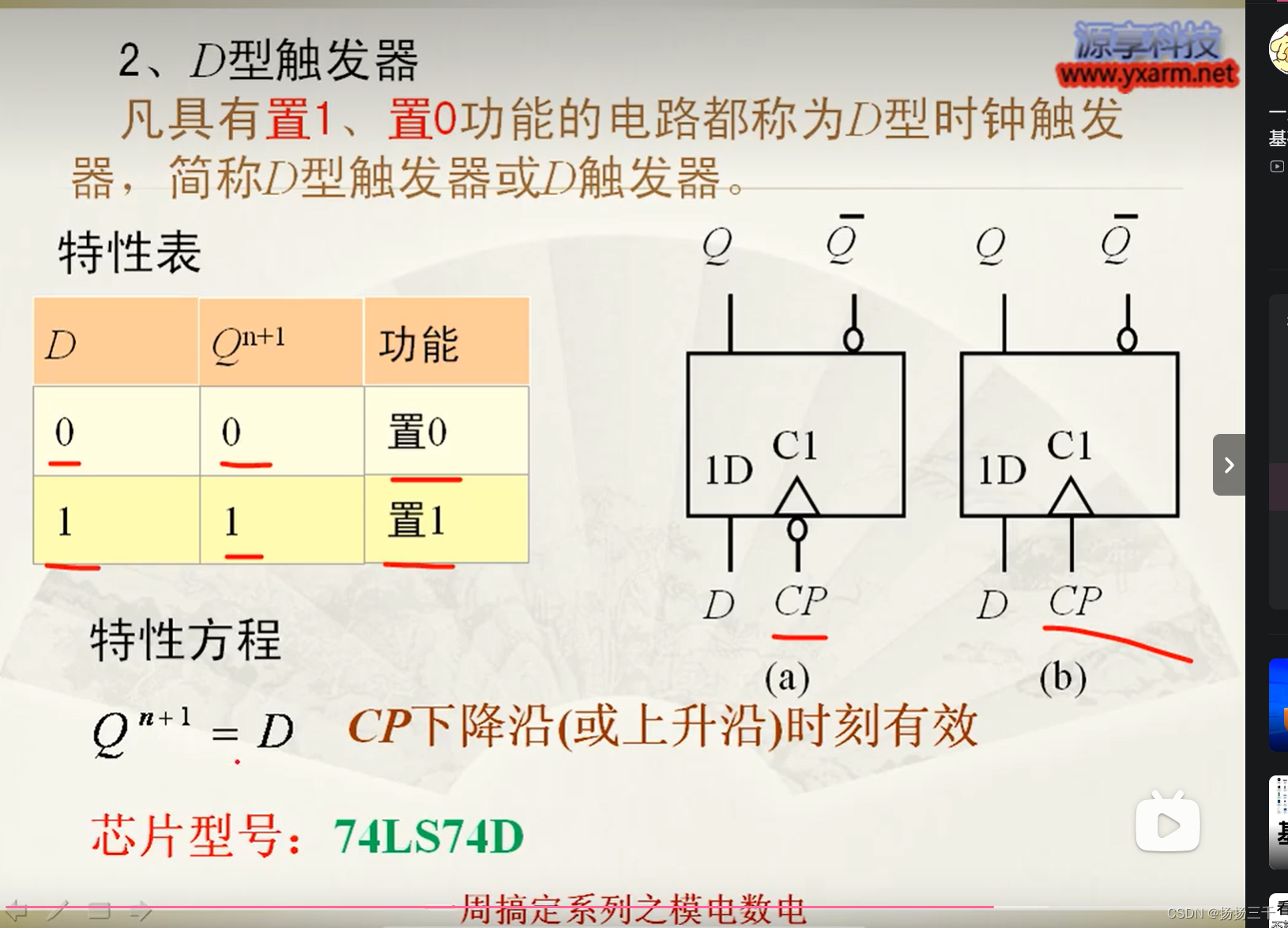

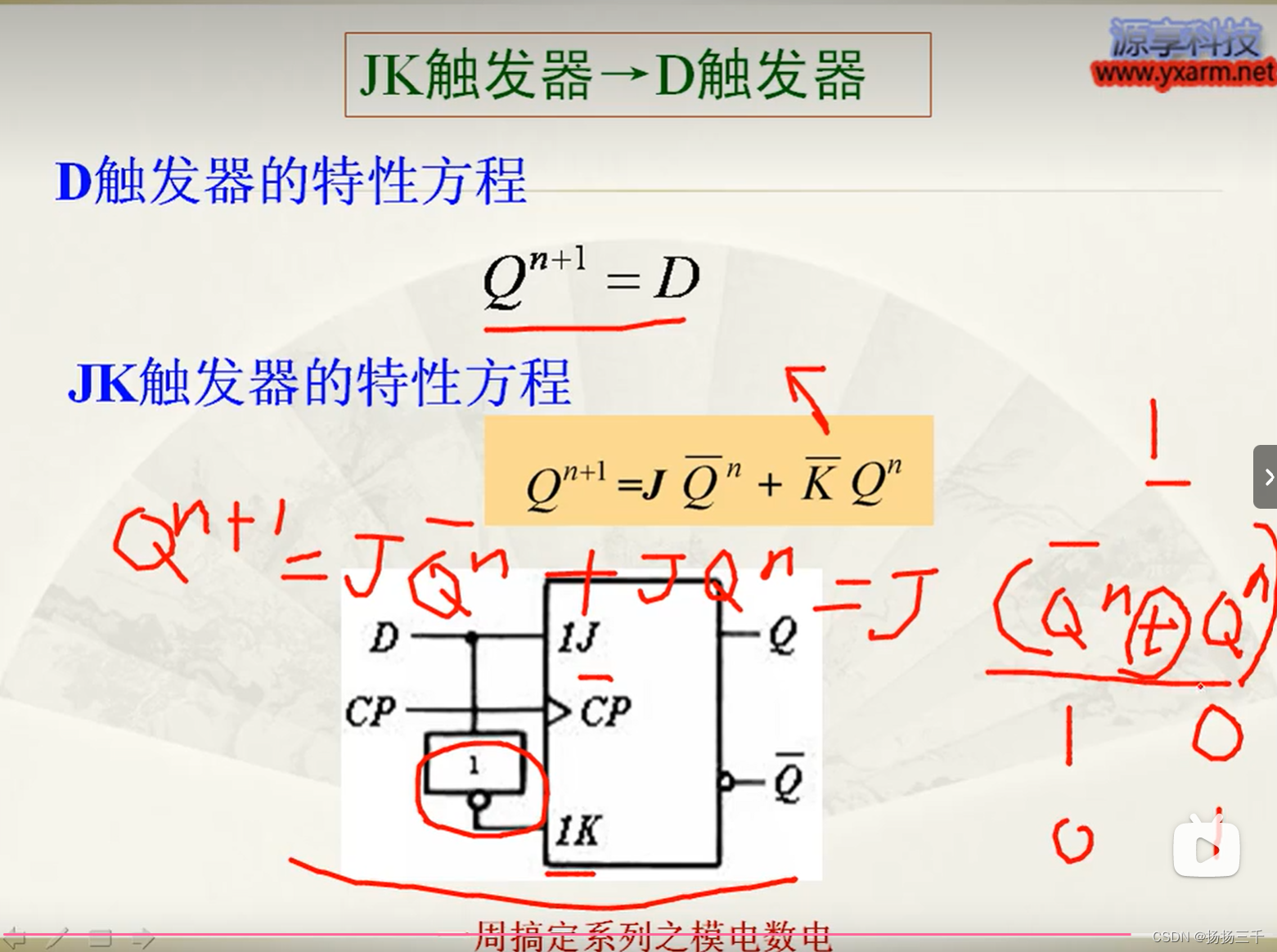

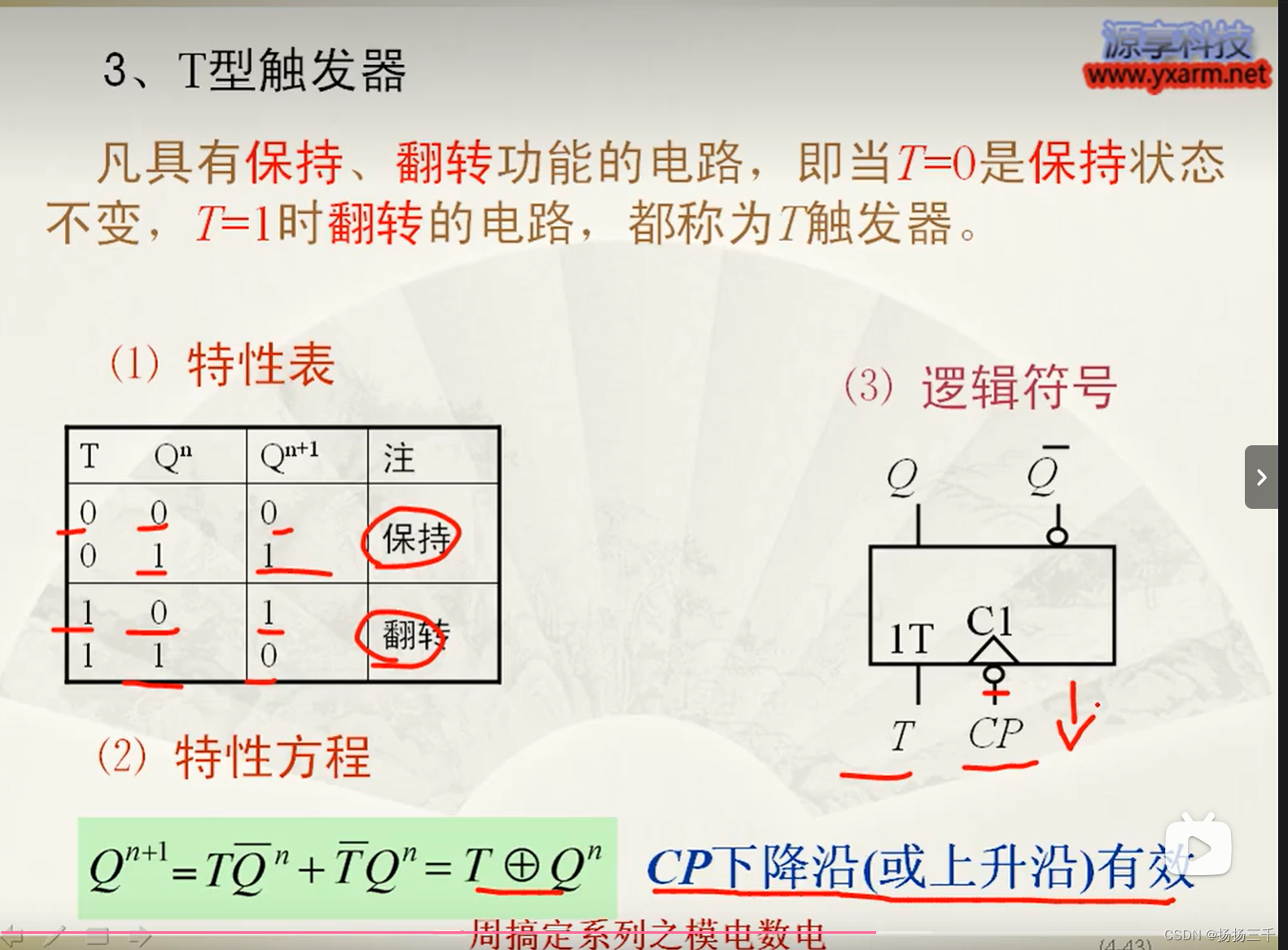

这是触发器(感谢大佬的图片)

D型触发器

T型触发器

JK型触发器

RS型触发器

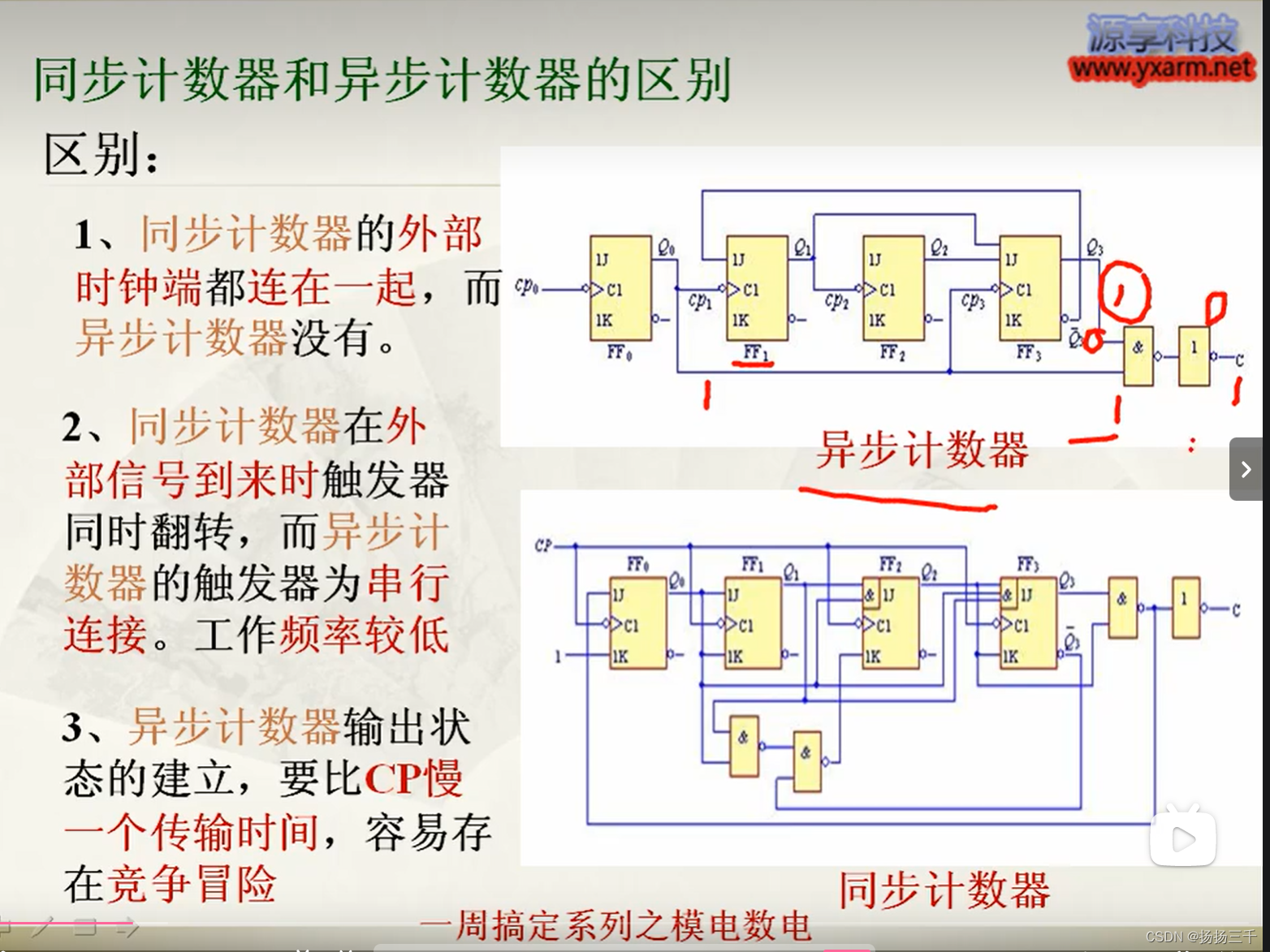

接下来是各种计数器(感谢大佬的图片)

(1),叠加自制100进制

(2),门电路反馈计数器

(3),同步二进制计数器

(4),同步十进制计数器

(5),同步异步计数器

这里提一嘴:设计类似数字电路时,会用到同步置数法和异步置零法,前者是在时钟信号的特定边沿到来时才生效,加1减1之类的,后者是当清零信号发生时,无论时钟信号的状态如何,都会立即将寄存器或计数器的值清零。这两种方法在对时序逻辑电路的学习中会经常学到。

432

432

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?