(1)半加器和全加器的区别:半加器没有进位输入,但全加器有进位输入。

(2)半加器和全加器均有加数、被加数、和(一位位宽)、进位输出。

(3)硬件使用:两个按键 key1、key2 两个LED灯, 一个表示进位输出,一个表示和。

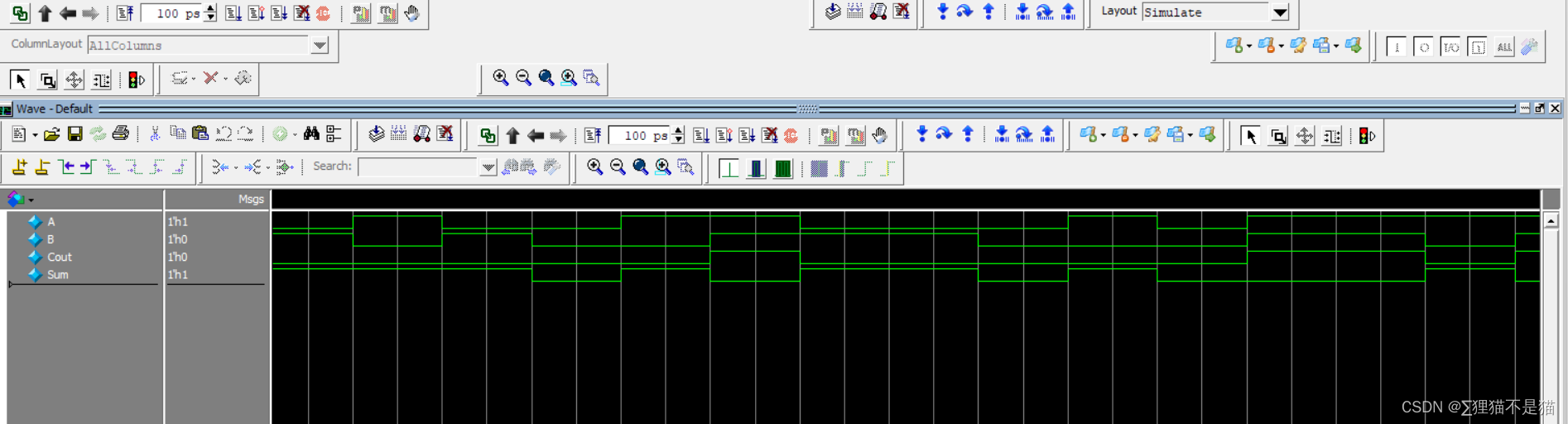

(4)modelsim波形窗口 快捷键:ctrl+g -模块化分组

(5)modelsim工具栏 layout-reset 各种窗口初始化 任意窗口 右上角“+” 所有选项卡放在一个界面内。

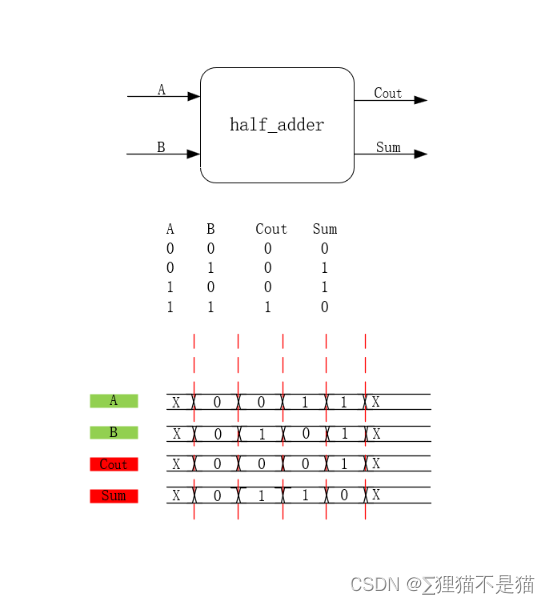

(6)visio框图:

(7)Verilog实现代码:

module half_adder(A,B,Cout,Sum);

input A;

input B;

output Cout;

output Sum;

assign {Cout,Sum} = A + B;

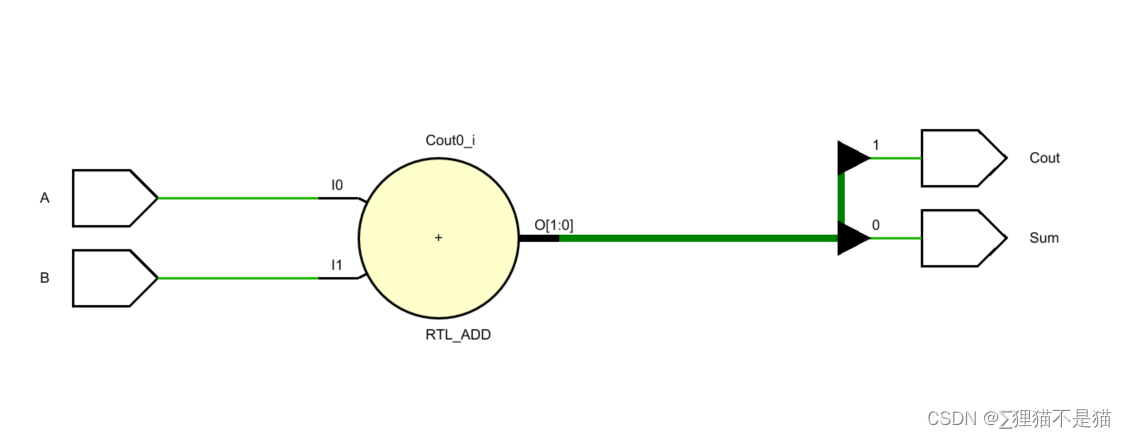

endmodule (8)RTL视图:

(9)仿真文件代码:

`timescale 1ns/1ns

module half_adder_tb;

reg A;

reg B;

wire Cout;

wire Sum;

half_adder half_adder_inst(

.A(A),

.B(B),

.Cout(Cout),

.Sum(Sum)

);

initial begin

A <= 1'd0;

B <= 1'd0;

#2000;

$stop;

end

always #10 A<= {$random} % 2;

always #10 B<= {$random} % 2;

endmodule

(10)仿真波形:

(11)引脚绑定:

(12)bin文件生成位置:runs/ impl_1文件夹下

1924

1924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?