吹水系列,概括一下FPGA的前沿技术,新时代应用和未来发展趋势,了解一下也好跟同事吹牛皮,其实没啥大用,闲着写写就当开拓思维了

1.传统FPGA架构的缺陷

在制造FPGA芯片时,随着单个硅片面积的增大,其工艺良品率会急速下降,这便是FPGA发想要进一步增加集成度与性能时所面临的问题。

如上一篇文章所言,在制程工艺发展几近极限的今天,各大厂商都转向致力于FPGA芯片架构的创新,以延续摩尔定律;然而无论提出如何新颖的观点,晶体管集成度的增加仍然是FPGA发展的绝对需求;由于单个晶体管的尺寸已经很难减少,增加硅片面积自然就成为了增加芯片集成度的最佳方法。

然而增加芯片面积也会有更高的工艺需求,这就导致硅片上芯片的良品率难以保障。例如,对于早期的芯片工艺,当硅片面积为1.5时,该硅片上的芯片良率大概有22%,可当硅片面积扩充四倍即6

时,良率就只剩下0.25%了。也就是说,4个独立的1.5

硅片与1个统一的6

硅片并不一致,虽然它们的总面积相同,但其能生产出来的合格芯片数量却大相径庭。

因此要想提高FPGA芯片集成度,则既要增加硅片总面积,又要减小单个硅片面积以保证良品率,人们自然想到的办法便是化整为零,将许多小面积硅片互联起来从而提高FPGA芯片集成度,这就是所谓的3D FPGA技术。

2. 3D-FPGA技术

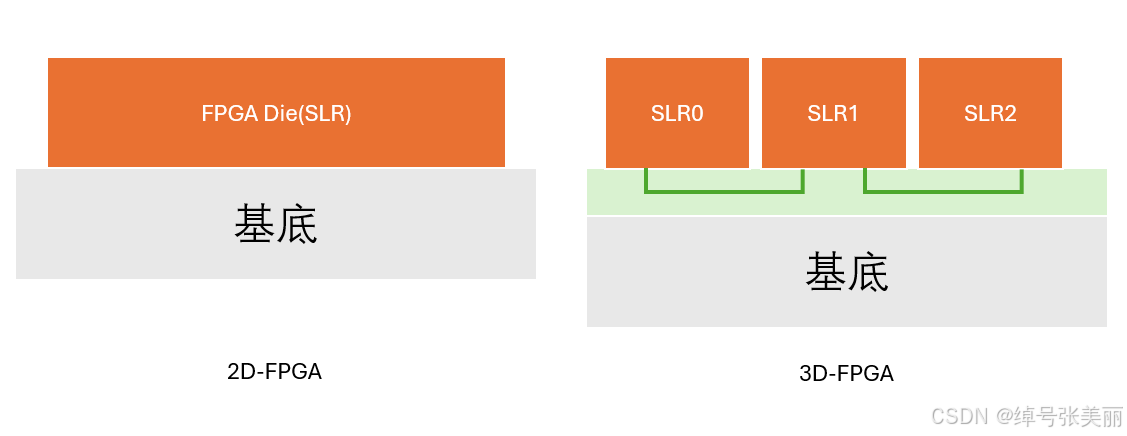

现今的3D-FPGA技术并不是“真3D”,其电路元器件并非是在三维空间中排列,布线也只是局限在一个二维平面之内;这个“3D”并不是几何概念,而是一个集合概念:例如对于传统的2D-FPGA,其芯片上各个元器件均在一个“位面”之内,它们可以通过这个“位面”之内的电线相连接;而对于3D-FPGA来说,FPGA上的元器件可能不在一个“位面”内,它们之间可能需要类似于“虫洞”这样连接不同“位面”的电线相沟通;这里“虫洞”就相当于连接不同硅片的电线。简单示意图如下

如图所示,3D-FPGA技术将FPGA硅片分割成若干份,再使用大量连线将其互相连接。虽然这些连线可以实现片间的沟通,但是为了避免这类通信所带来的延时问题,设计者们也会尽可能的将具备相同功能的FPGA块布置在一个硅片之上,避免片间的频繁通信。

当然这样的“伪3D”技术只是一种过渡,人们对电路元件呈三维空间排列的“真3D”技术也有所建树。例如2019年Intel发布的Foveros封装技术,并已应用于其CPU芯片上,所以“真3D”FPGA的出现也不会太远了。

3.Xilinx的SSI技术

3.1 SSI技术原理

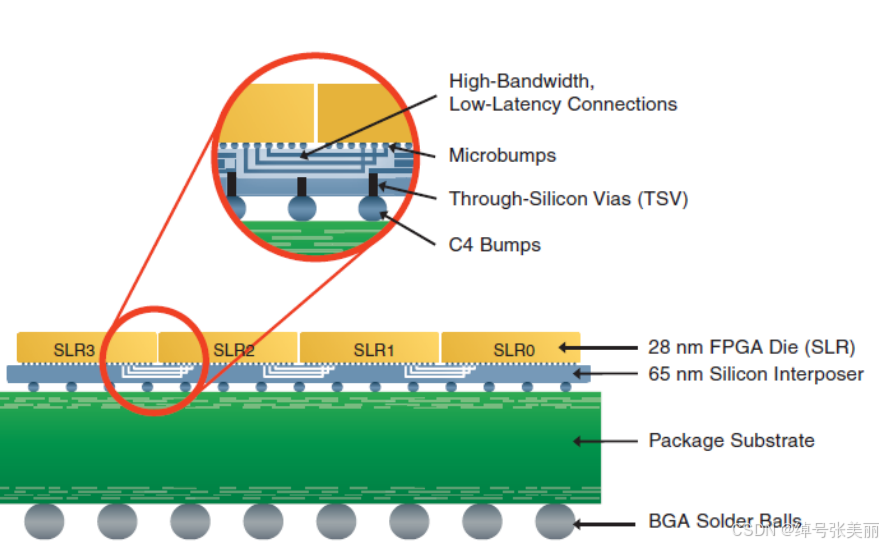

SSI(堆叠硅片互联)是Xilinx(已被AMD收购)的3D-FPGA解决方案。其技术示意图如下:

如图SSI技术在FPGA硅片与基底之间加了一层硅中阶层,再刻蚀电路将不同FPGA块连接起来;由于这一层只需要做简单的连线,因此不需要十分精密的工艺,如图该工程只采用了65nm制程。

3.2 SSI技术优缺点

SSI技术十分适用于对新一代制程工艺的跟进迭代。每当新一代制程工艺问世时,此时的工艺并不成熟,很难保证良率合格;此时SSI技术可以提高良率,克服工艺早期的缺陷,从而更快的跟进迭代,迅速抢占市场。

然而它的缺点也很突出,这由它的结构所决定。片间连线造成的延时会降低芯片的性能,稳定性与开发容易度;此外,FPGA不同功能块的分离,可能会在一些应用中显著影响到工程的性能,同时增加了开发者的开发难度与开发工具的适配难度。

因此SSI能够快速迭代技术,但在开发中可能需要额外考虑芯片的划分布局,方能充分利用新制程的优势。

4.Intel的EMIB技术及FPGA异构化趋势

4.1 EMIB技术原理

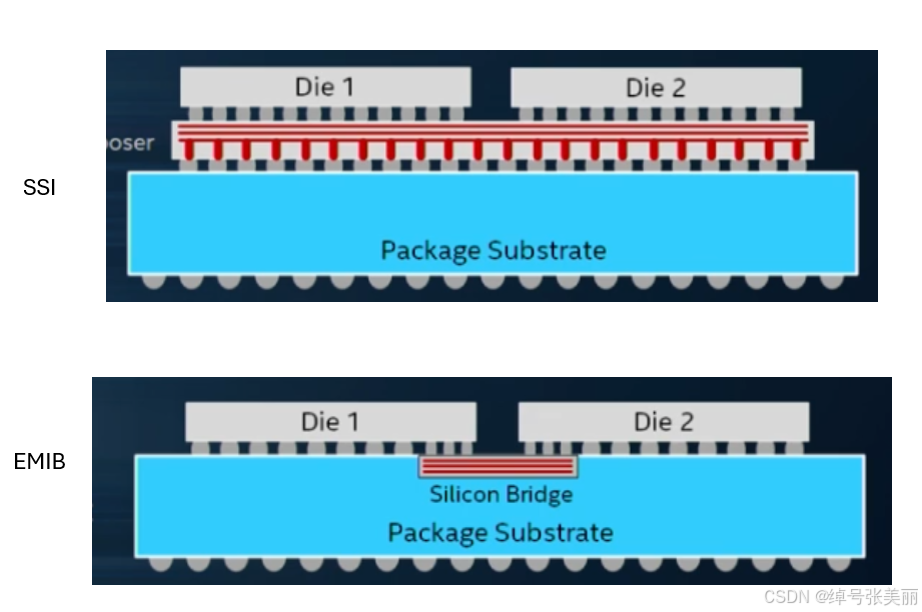

EMIB(嵌入式多硅片互联桥接)技术是Intel公司的3D-FPGA技术。不同于SSI技术引入硅中介层统一实现硅片间的互联,EMIB技术在各个硅片之间直接进行连接,这大大降低了系统设计的复杂性.如图将SSI与EMIB技术相比较,EMIB省去了硅中介层的引入,直接在基底中实现各硅片I/O的连接,即硅桥(Silicon Bridge)。

4.2 EMIB技术特点

从图上可以看出,EMIB一方面规避了中介层的引入,从而避免了信号通过硅中介层产生的延时;另一方面省去了在中介层的大量布局走线,大大减少了系统设计的复杂性。这项技术在制程工艺成熟之后,呈现出了比较大的优势。

4.3 FPGA异构与EMIB的应用

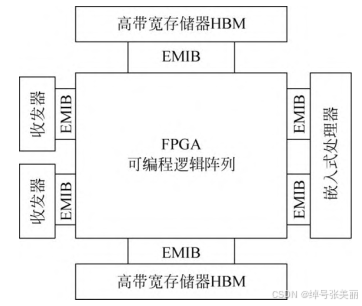

所谓异构,即多种大型处理器,如FPGA,CPU,ARM,DSP,AI引擎等,集成于一个系统,充分利用各大型处理器优势的技术,这是集成电路未来发展的关键趋势。

而对于这个趋势,各个大型处理器之间的连接与协同便是该技术的关键。EMIB不仅可以应用于FPGA各子模块的连接,同时也能应用于FPGA与其他电路的连接。如图所示,这是Intel的Stratix10系列FPGA结构图,FPGA通过EMIB技术与其它处理器相连接协同工作。

4.4 EMIB技术的缺陷

相较于SSI技术的优势,EMIB在每代工艺发布初期时,由于良率低的缘故,很难及时跟进先进技术,从而在技术革新的早期不具备优势。此外,EMIB两端的器件可能存在一定差异,例如FPGA与HBM的收发器电气特性和制作工艺有所差别,这可能会导致一系列问题,例如两端发热不均等。

5.总结与预告

这一篇文章我们探讨了传统FPGA架构在提升集成度和性能时的工艺瓶颈,从而详细介绍了3D-FPGA技术的发展。我们重点分析了Xilinx的SSI和Intel的EMIB技术,SSI通过硅中阶层实现互联,适合快速迭代但存在性能和开发难度问题;EMIB则直接互联,简化设计并支持异构集成,但在工艺初期良率较低。除此之外,我们着重强调了FPGA异构化趋势及其在未来集成电路发展中的重要性。

3D-FPGA是FPGA发展的一大方向,而另一大方向便是”异构化“。下一篇我们将了解XIlinx和Intel最先进的FPGA芯片架构:ACAP与Agilex,从这两种芯片中我们能看到”异构化“趋势的现实依据,以及未来FPGA开发方式的变革方向。

612

612

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?