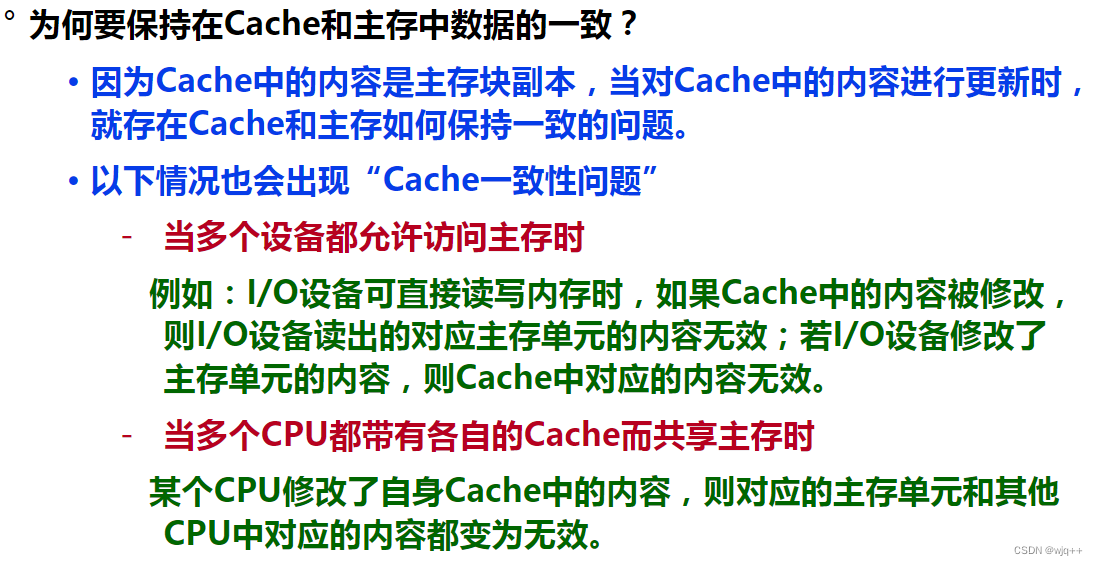

为什么会有cpu缓存一致性问题?

cpu缓存一致性指的:是缓存中和所其对应在主存中的数据的一致性。

因为cpu运算产生新数据后基于写回策略只更新缓存的值会导致缓存和主存不一致问题

解决cpu缓存一致性问题前,先了解写回策略是什么

了解写回策略前,先介绍三个术语:1.缓存命中,指的是cpu在缓存中根据cacheline的索引tag查找某个数据时成功找到 2.缺页,缓存没命中叫做缺页,页是存储单元,意思是缓存中没有这个单元,当发生缺页时,导致异常,cpu控制权交给操作系统,操作系统将缺失的数据存进缓存,缓存数据最小单元是一个cacheline,64字节,其中就包含了tag索引。数据存好后,切换回刚才的进程,从发生异常的指令指向,也就是再次查找,当然缓存命中。3.脏数据(dirty data) 指的是cpu产生新数据后只更新缓存中的值,不更新主存中的值,此时缓存中是新数据,主存中为过期数据,这个不一致的新数据叫做脏数据,由于新数据只能由cpu运算产生,脏数据只存在于缓存中

cpu的读/写策略

一、cpu的读策略在介绍缺页时讲过,有两种情况:1.缓存命中(找到) 2.缺页(没找到)

二、cpu的写操作有两种情况:

1.写命中(write hit):要写的单元在cache中存在

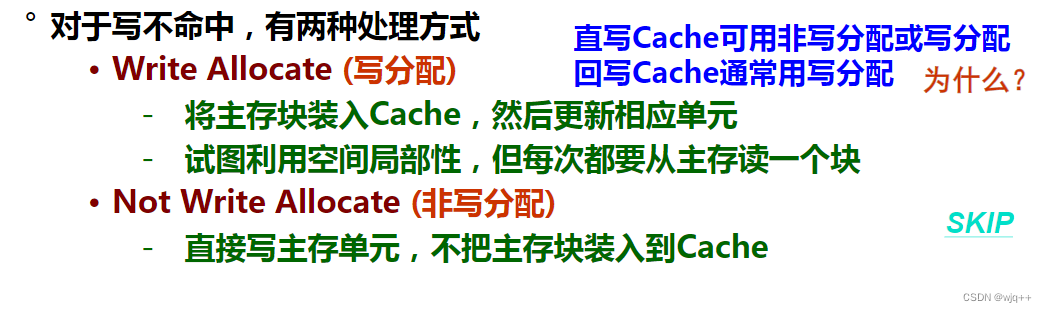

2.写不命中(write miss):要写的单元在cache中不存在

对于写命中,有两种处理方式:

a.wirte through(写直达策略)

- 同时写cache和主存单元

- 问题:每次写主存增加10%指令量,降低性能

b.write back(写回策略)

- 只写cache,不写主存

- 优点:相比写直达,大大降低主存带宽压力

7799

7799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?