Chapter 7 Linear Voltage Regulators

这一章我们介绍LDO.

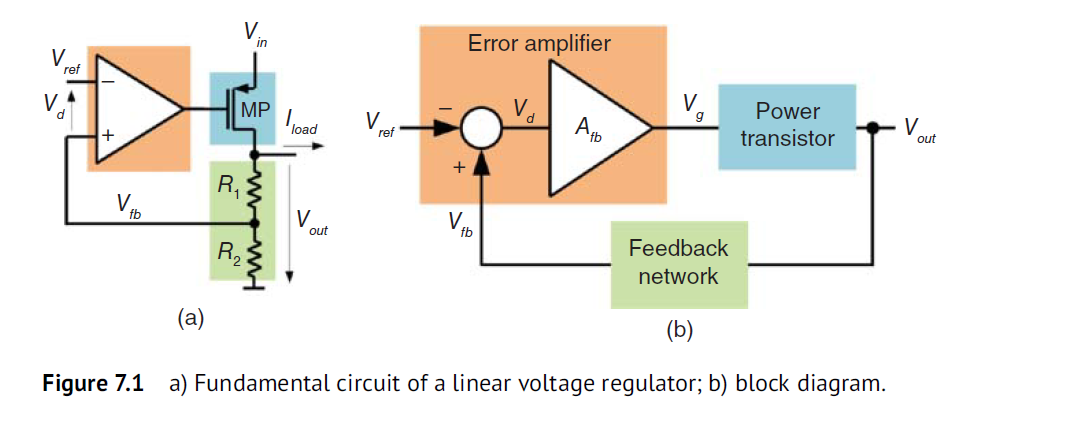

7.1 Fundamental Circuit and Control Concept

LDO基本原理图如下: 形成负反馈来稳定Vout电压. Vfb =R2 / (R1 + R2 )Vout = 𝛼 Vout.

小信号模型

rds = 1∕(𝜆ID), For 𝜆 = 1∕20V and ID = 20 mA we can estimate rds = 1 kΩ, 但是R1 R2 达到 10–100 kΩ. 因此输出电阻为rds.

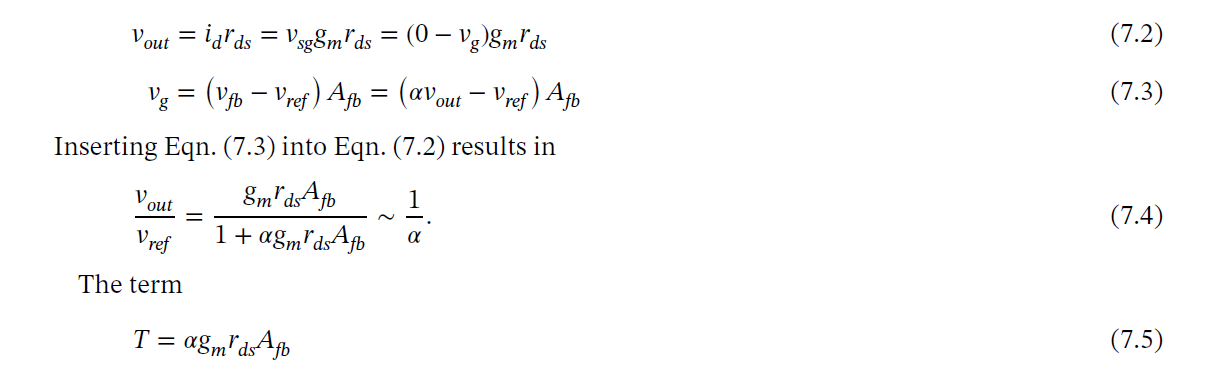

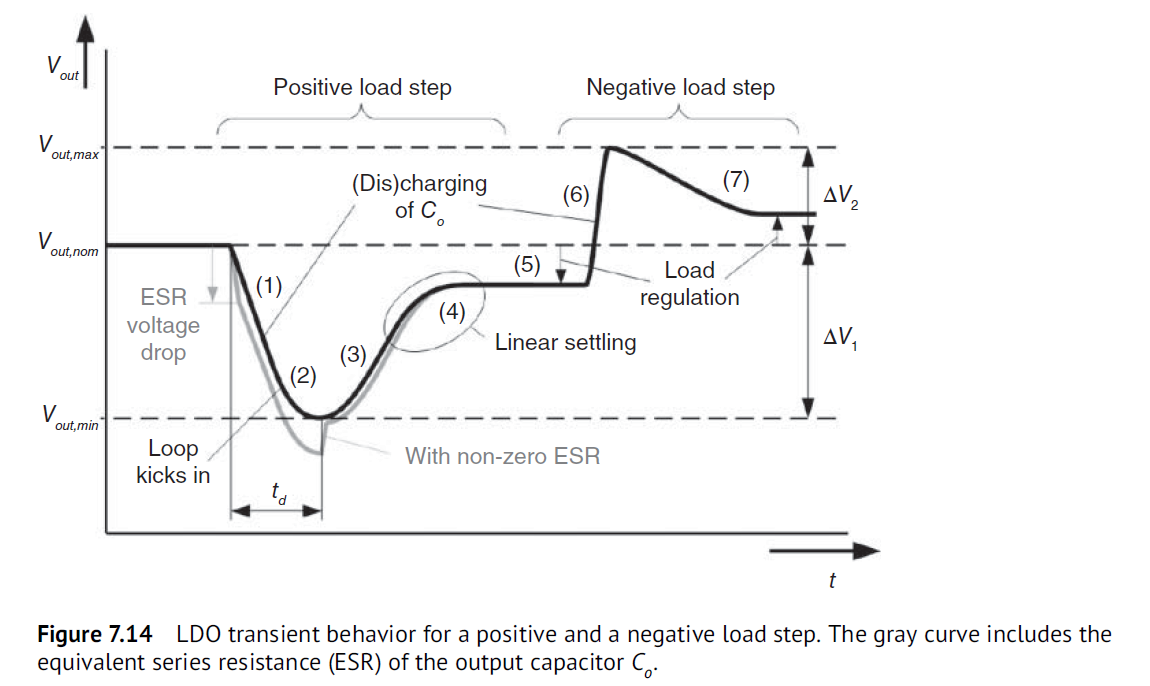

LDO也可采用NMOS做功率管, 面积为PMOS的 1/2 ~ 1/3, 但需要charge pump提供gate电压.

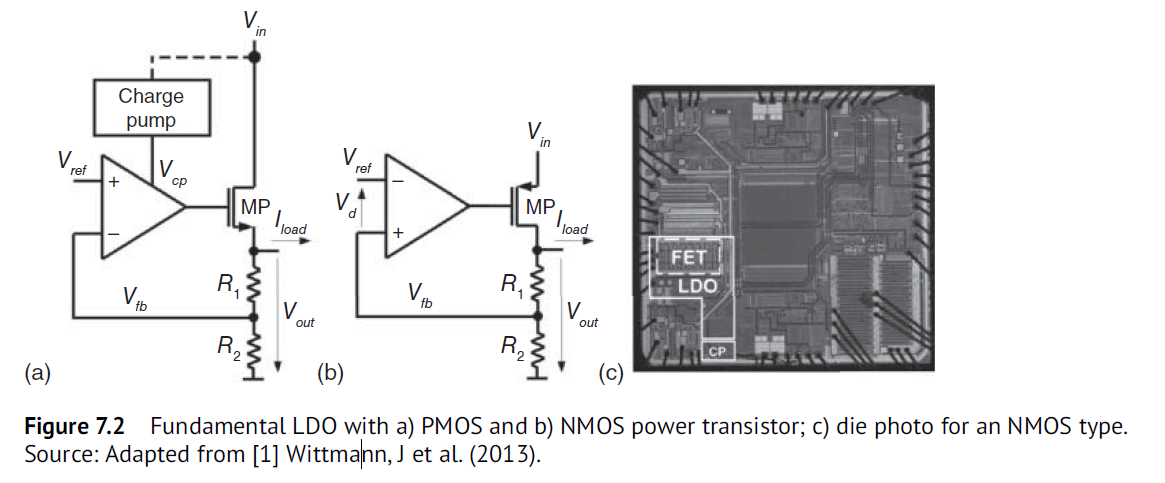

7.2 Dropout Voltage

当输入电压Vin降低时, 输出Vout也会降低. 需要确保 dropout voltage Vdo = Vin − Vout at 95% of the nominal output voltage, Vin = 0.95Vout,nom. 功率管尺寸需要确保能满足最大输出电流

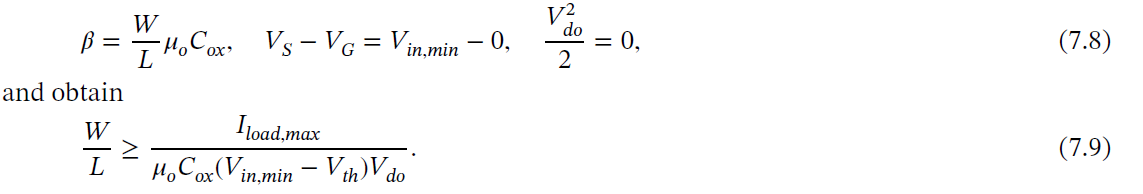

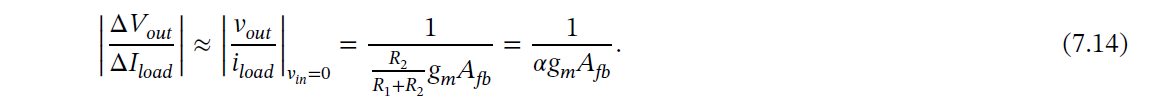

对于 PMOS:

对于 NMOS:

7.3 DC Parameters

7.3.1 Power Efficiency

LDO能达到的最高效率就是Vout/ Vin. LDO provides a “clean” output voltage.

𝜂 = Pout / Pin = VoutIload / VinIin = VoutIload / Vin(Iload + Iq) ≈ Vout / Vin

7.3.2 Current Efficiency

𝜂I = Iload / Iin 100% = Iload / (Iload + Iq) 100%. 大负载下接近100%.

7.3.3 Load Regulation

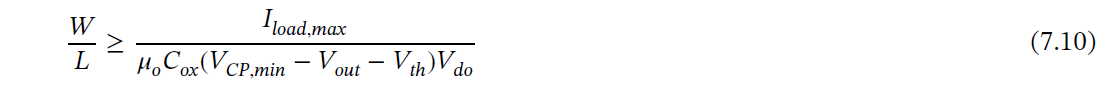

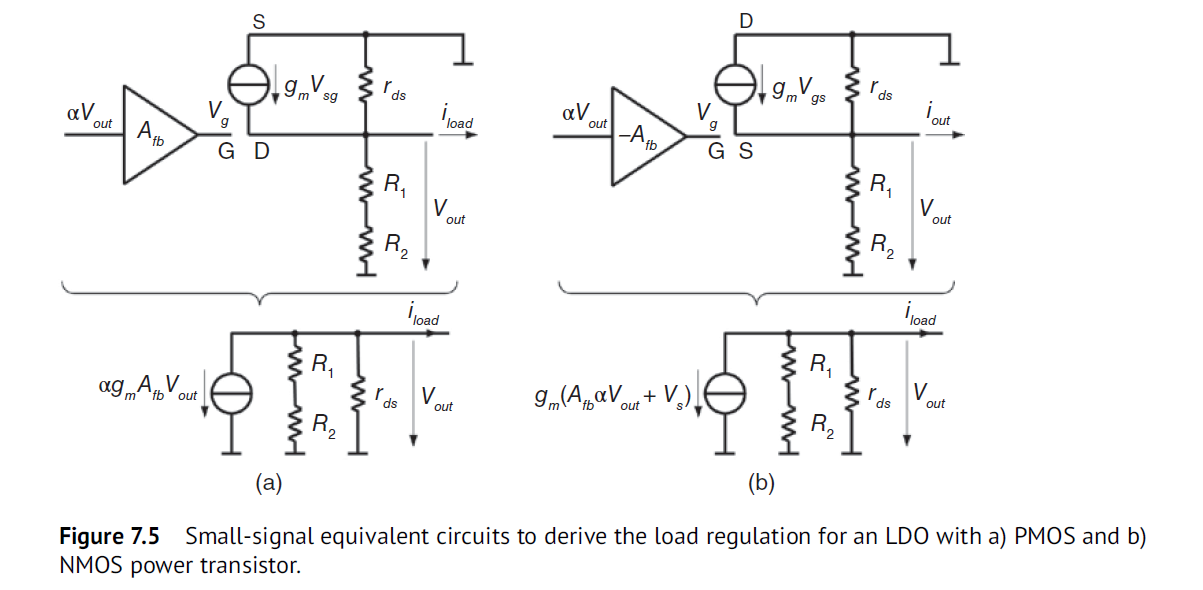

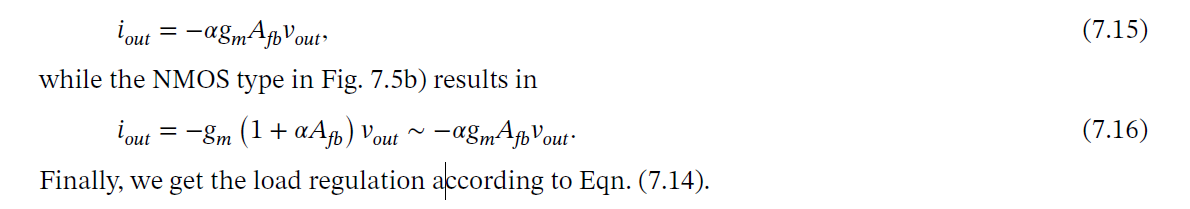

NMOS和PMOS的小信号模型如下

PMOS和NMOS的 load regulation 一样

PMOS和NMOS的 iload表达式类似

7.3.4 Line Regulation

PMOS和NMOS line regulation的小信号模型如下

[外链图片转存中…(img-vdzrZAf2-1742113400807)]

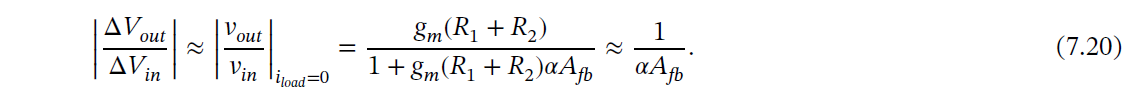

PMOS的 line regulation

NMOS的 line regulation

可以看到NMOS LDO的line regulation相比于PMOS, 小了gm rds倍, 大约为100倍. 直观理解 PMOS是source接vin 直接影响drain电流, NMOS的输入是drain不太影响电流.

7.4 The Error Amplifier

EA提供LDO环路的增益和补偿. 典型EA 的DC gain为40-60dB, 太高了 稳定性不好调.

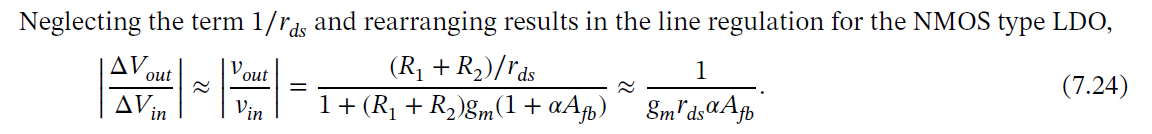

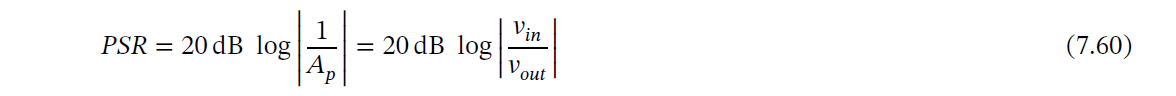

EA常用symmetrical 运放如下所示, 或者folded cascode

这是一个单极点OTA

slew rate为 SR = Ibias∕Couta

EA的电源可来自VIN经过pre-regulator. 或者启动结束后用Vout. 对于NMOS需要来自charge pump.

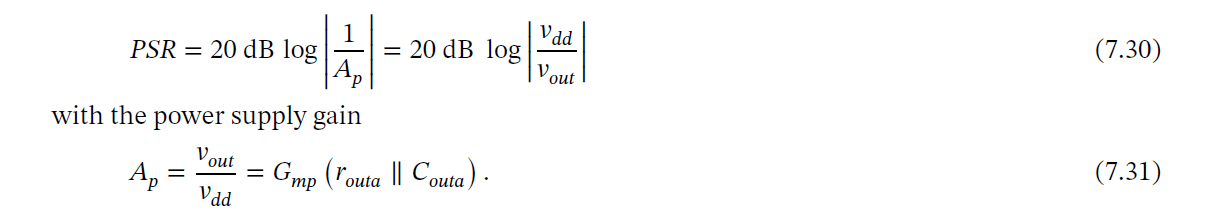

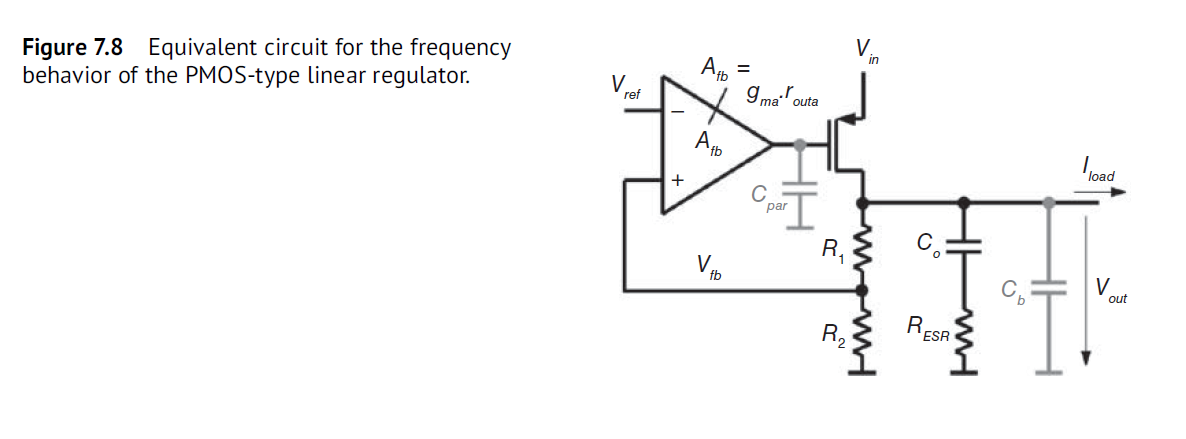

EA的power supply rejection (PSR) 对于LDO的整体PSR很重要. PSR的定义为Vdd/Vout

it means EA 的PSR为1, 即vdd的抖动直接影响vout, 对于PMOS LDO是好事, 可以降低整体的PSR.

对于NMOS, 需要采用Fig 7.7 complementary的形式, (flipped along the horizontal axis with PMOS and NMOS devices exchanged). 即NMOS为mirror-diode, PMOS为电流镜, 让EA的PSR为0.

这里PSR的讨论可参考文献 [2] Steyaert, M. and Sansen, W. (1990) Power supply rejection ratio in operational transconductance amplifiers. IEEE Transactions on Circuits and Systems,

7.5 Frequency Behavior and Stability

7.5.1 PMOS Type

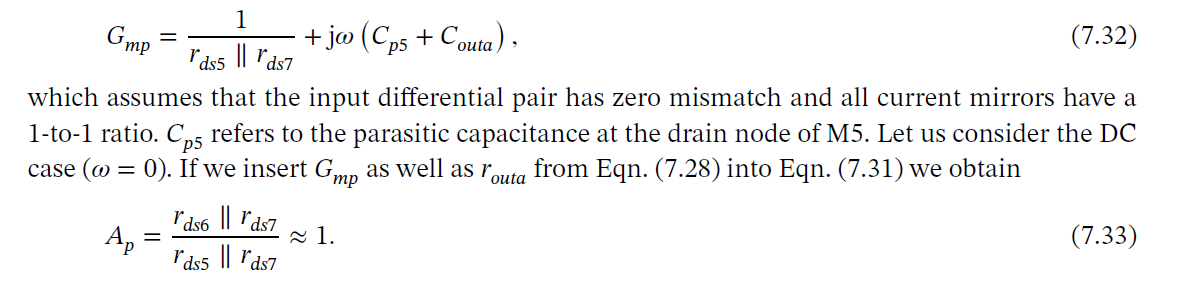

PMOS LDO等效电路如下

因此 Loop Gain

T(s) = gm zout(s) Afb(s)

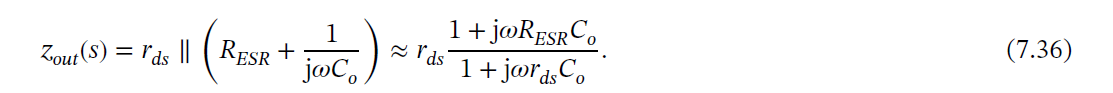

rds ≪ (R1 + R2), Resr添加了一个零点. RESR ≪ rds

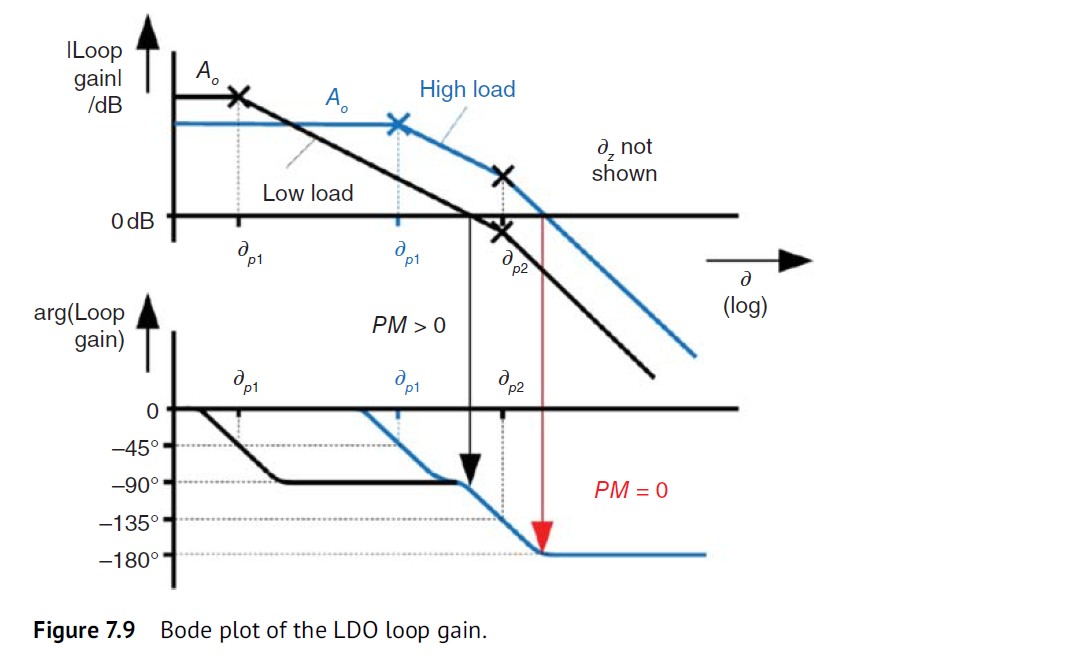

Loop Gain的 Phase的Gain图如下

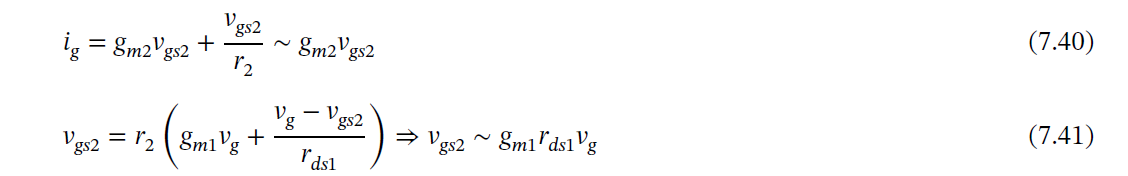

DC Gain T0=gm rds gma routa. 极点1 wp1在输出Cout, 极点2 wp2在PMOS gate处, 左零点(好零点)在输出电容Resr处

Frequency Compensation

wp1 随着LDO负载电流Iload发生偏移, rds ∝ 1 / Iload, wp1 ∝ Iload, 而Iload在uA到A之间变换, 极点1 变化很大.

整体设计思路是让wp1 或者 wp2成为主极点, 而且两者要分开. 传统LDO通常把输出作为主极点. Capless LDO把 wp2作为主极点.

我们假设wp1为主极点, 在Iload大时, wp1变大, 和wp2接近, 稳定性最差. 可采取下面方法增加Phase Margin, 确保60°

-

Lowering the DC loop gain To, 降低DC Gain. 即降低Afb的增益, 让GBW减小, 增加PM. 但是load regulation和line regulation会变差.

-

Reduce 𝜔p1, 通过增加Co来降低wp1. 但是LDO会变慢, load transient变差.

-

Compensation via 𝜔z by choice of RESR. Resr不固定, 通过添加电阻串联Resr

-

Increase 𝜔p2. 通过减少Cpar来增加wp2. 但是Cpar由power管gate电容决定. 所以一般是通过添加buffer, 减小routa, 来增加wp2.

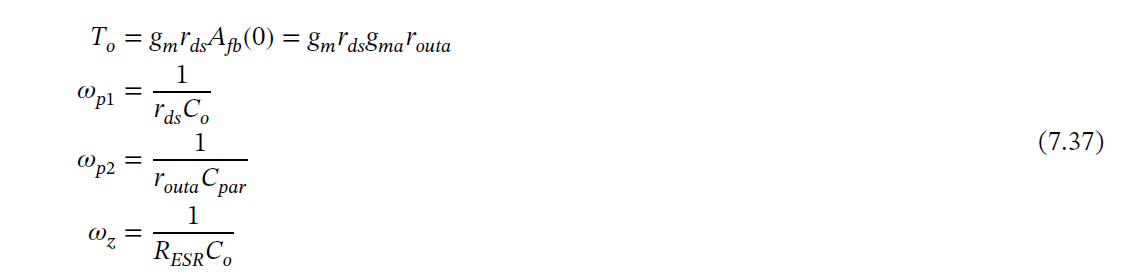

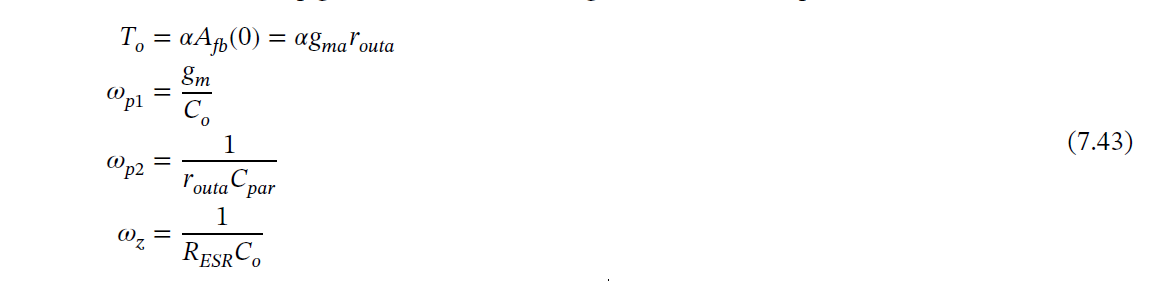

Inserting a Buffer

下图展示在EA和gate之间添加buffer. (a)

routb ≪ routa, 因此把gate处的极点2大大增加, 𝜔′p2 = 1 / (routb C′′par) ≫ 𝜔p2.

第三个极点wp3在EA输出处, 也很高频. 𝜔p3 = 1/ (routa C′par) > 𝜔p2. 如图 (b)所示

添加buffer可用简单的source folower ©. 其输出阻抗 routa ∼ 1∕gm 在10 kΩ级别. 而EA输出routa在1MΩ级别. 因此𝜔′p2 至少比wp2高10倍.

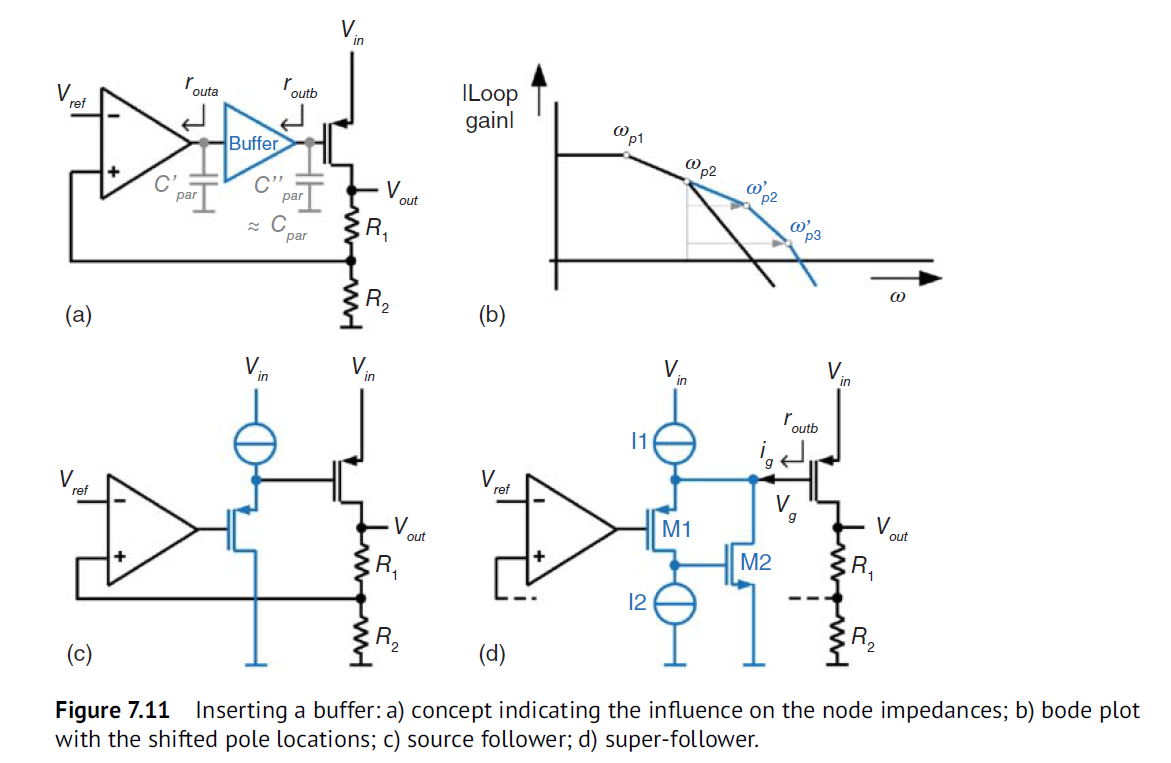

(d)中的super-follower能进一步降低输出阻抗. ig为M1流过的电流+M2流过的电流

输出阻抗 routb比单管source follower减小(gm2 rds1, 差不多100倍), 因此wp2能推远100倍.

因为wp1 和Iload成正比. 在大Iload电流下可以成比例adaptively increase增加I2, 进一步减小routb, 确保wp2’远离wp1.

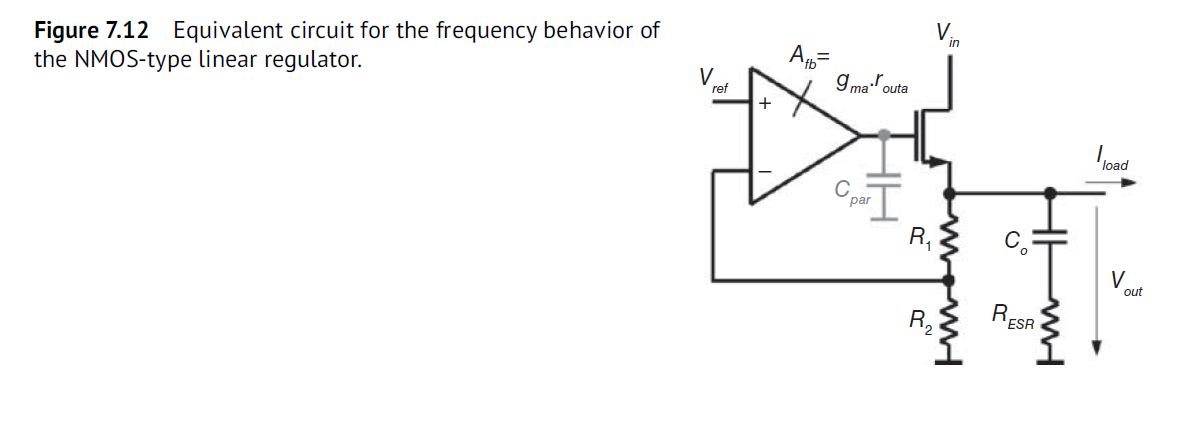

7.5.2 NMOS Type

NMOS等效电路如下图示

NMOS LDO的DC Gain T0比PMOS小了gm rds倍, 因为NMOS作为source follower. 极点1 wp1在Cout处, wp1=gm/C0. 极点2 wp2 在NMOS gate处. ESR零点.

因为gm ∝ Iload, 因此也可以加入buffer, 推远wp2. NMOS LDO的电源轨来自Vcp, 即额外charge pump.

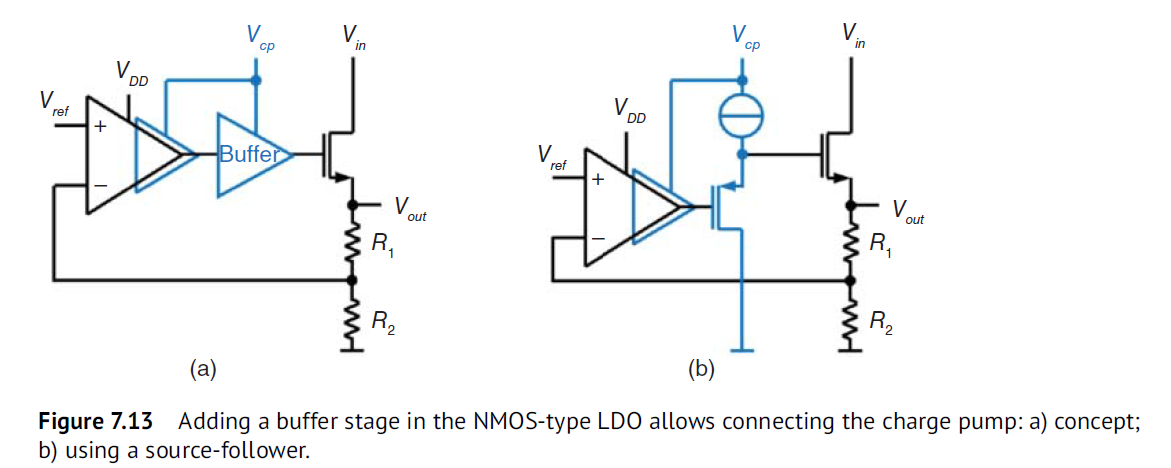

7.6 Transient Behavior

7.6.1 Voltage Under- and Over-Shoot

LDO的load transient如下图所示, 发生load瞬态时

- ΔVout /Δt = ΔIload / Co, Cout提供额外的负载, 在极短时间有ESR drop.

- 环路开始接管, 增加功率管电流, 直到输出电容停止discharging.

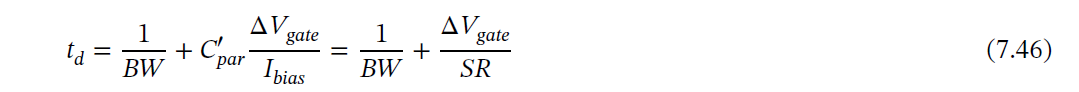

undershoot电压 ΔV1 = ΔIload / Co td.

LDO的响应时间td取决LDO闭环环路带宽(BW)和EA运放的slew rate, SR=Ibias/Couta. 添加buffer能极大减小Couta

因此 td = 1/BW + C′par ΔVgate/Ibias= 1/BW +ΔVgate/SR

环路带宽BW和Co成反比.

- 功率管电流超过load current, 输出Vout增加

- transient behavior取决于LDO的Phase Margin, 如果under-damp, 系统会ringing

- Vout最终值取决于load regulation的DC值. LDO可视为VDC+电阻, iLoad越大, 输出电压Vout越低.

- negative load step, 类似重载跳轻载, overshoot和undershoot电压类似,

- 环路接入, 把Vout regulate到最终电压.

输出电容Co能减小输出电压变化 slew rate, under shoot和over shoot, 但是也会降低带宽BW, 导致td变大, 即LDO的settle time变大.

7.6.2 Fast Transient Techniques

为了提高LDO的瞬态响应速度, 可以加入fast-transient loop(快环). 快环甚至可以bypass EA, 甚至buffer, 直接驱动功率管. 快环需要bandwidth很宽, 这样settle time才能小.

7.6.3 Slew Rate Enhancement

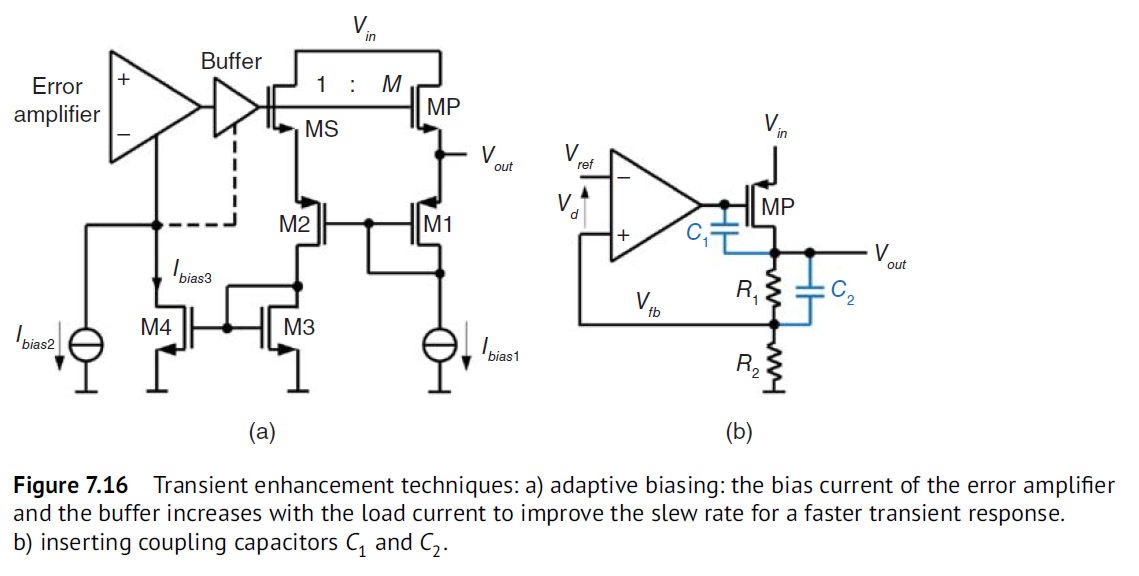

adaptive biasing 自适应偏置技术通过采样输出电流Iload, 动态调整偏置bias, 能在保证效率下, 提高slew rate. 如下图所示

MS为MP的采样管, M1和M2确保两者Vds相同, Ibias1相比Iload可忽略不计, 因此MS流过Iout/M电流, Ibias3 即为 adaptive bias, 再叠加固定Ibias2, 可供给EA和buffer做偏置.

7.6.4 Loop Bandwidth

上图Fig 7.16(b)中Capless LDO的miller补偿也可提高带宽. 假设Vout跌落, 通过C1传导, MP gate下降, 因此MP流过的电流增加, 补偿Vout. 另外bypass电容C2可以feedforward直接把Vout信息送给EA.

7.7 Noise in Linear Regulators

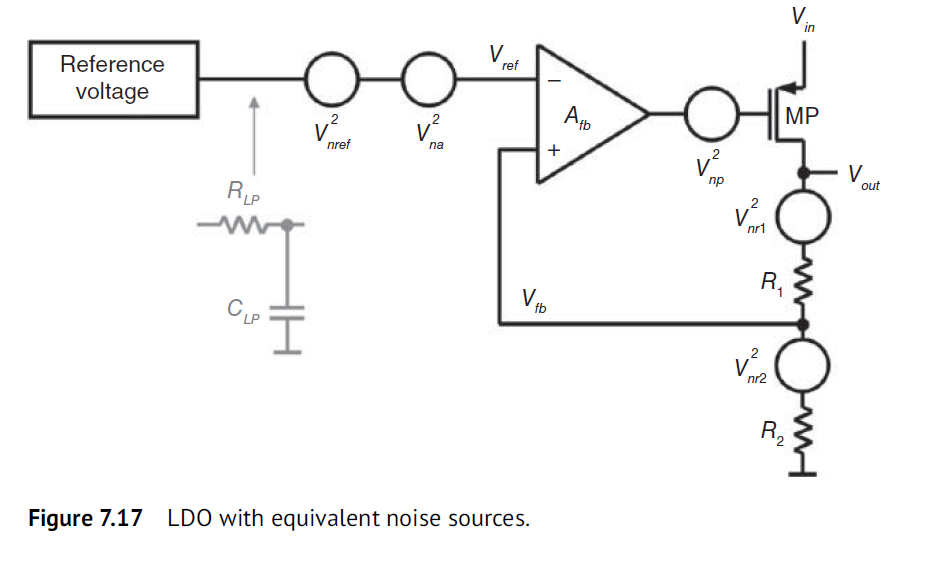

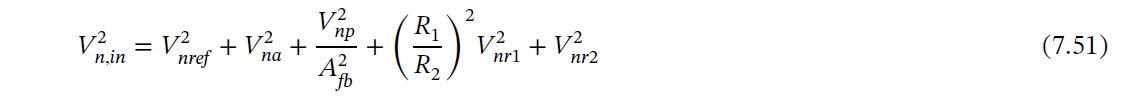

LDO的噪声如下图, 包括热(white)噪声, flicker noise (1/f -noise), 噪声在LDO的闭环带宽BW内积分.

input-referred noise计算方法为把每个噪声源除以相应到输入的gain, 对于LDO输入定义为EA的输入.

因此LDO的输入噪声为

R1和R2的噪声为 Vnr^2 = 4kT R BW. 功率管噪声要除以Afb因此可以忽略不计, R1和R2的噪声也较小.

LDO的噪声主要来源于基准噪声Vnref 和 EA自身噪声Vna.

可以通过在Vref处添加RC滤波, 设置cut-off频率fo很低来过滤输入基准噪声.

fo = 1/ (2π RLP CLP). For given BW的Vnref

LDO的输出噪声为输入噪声乘以LDO的闭环增益. 即Vn,out=Vn,in*1∕𝛼 = Vn,in * Vout/Vref.

注意噪声为RMS, 需要开平方.

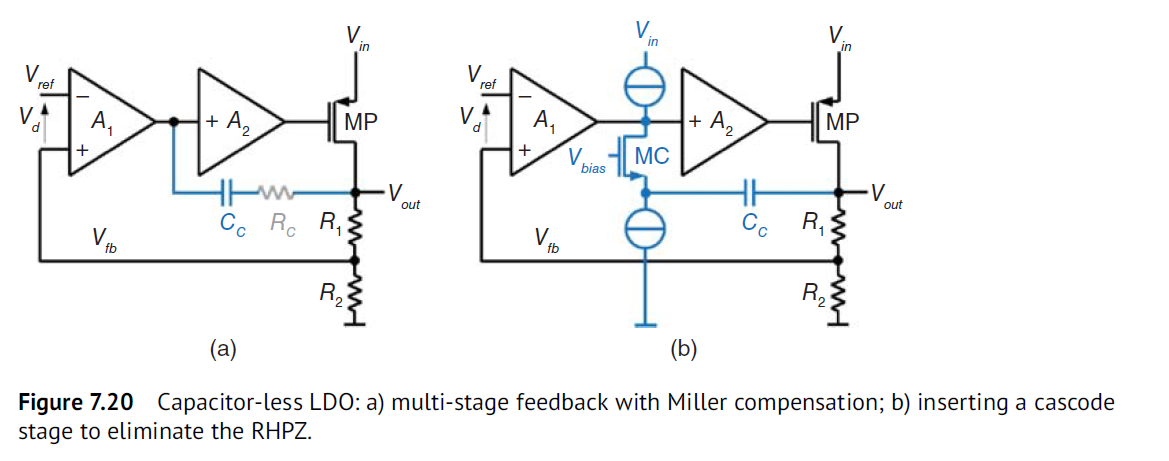

7.8 Power Supply Rejection

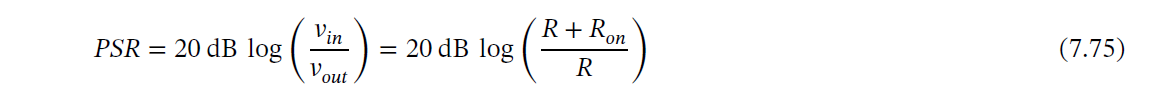

power supply rejection (PSR) 定义为LDO输出抑制输入ripple的能力

Ap=power supply gain. PSR有时也被称为power supply rejection ratio (PSRR). 但是在amplifier theory中, PSRR定义为 signal gain (from signal input to output) 除以 the power supply gain Ap.

PSR由多种因素叠加而成, (1) LDO regulation loop的PSR能力 (2) EA+power Stage的PSR.

(1) 考虑 LDO regulation loop, 在wp1即主极点之前, PSR=open-loop gain, 因此典型LDO在低频(1KHz)有80dB的PSR, 当频率高于主极点后, PSR开始减小.

(2) 考虑EA的PSR, 分PMOS和NMOS LDO. 功率管PMOS的source直接接vin, 因此需要EA的输出也sensitive to vin, 这样当vin变化时, PMOS功率管gate和source都以相同幅度变化, EA的PSR很低, 这样PMOS LDO整体的PSR最大. 对于PMOS LDO, EA输出级PMOS采用mirror-diode结构, 类似Fig 7.7结构, EA PSR就很低.

对于NMOS LDO, 因为功率管NMSO drain接输入, 需要EA的PSR很高, 这样NMOSLDO整体的PSR最大. 对于NMOS LDO, EA输出级NMOS采用mirror-diode结构, PMOS采用电流镜, Fig 7.7结构对偶, EA PSR就很高.

7.9 Soft-Start

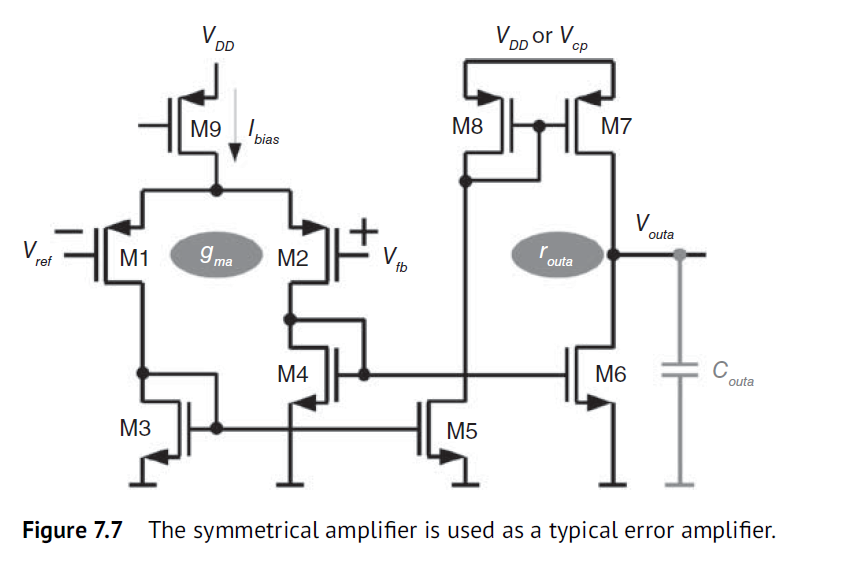

加入VIN后, LDO会启动, 功率管可能fully on, 造成in-rush电流很大, 造成器件损伤或者coupling造成ringing, 因此需要加入软起. 可用下面电路实现. Vs电压从0V达到VDD, 在Vs<Vref时, bypass M1, Vfb=Vs, 控制输出Vout的上升斜率为1–10 V/ms

7.10 Capacitor-Less LDO

Capless LDO无需外围PCB电容, 适合SOC集成方案. Capless LDO的输出电容Co为几百pF, 因此输出极点不是主极点. 一般把功率管gate作为主极点, 输出作为次极点. 输出次极点wp1和load有关, load越小wp1次极点越小, 越接近主极点. 因此capless LDO轻载下稳定性更有挑战.

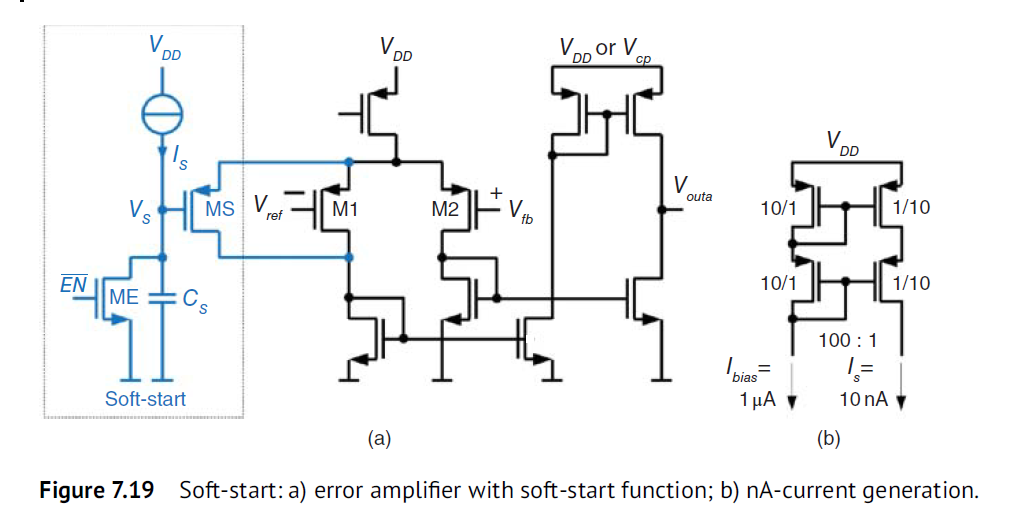

Cpaless LDO通过多级EA 实现high gain bandwidth. 通过miller补偿, 把主极点放在第一级的输出, 如下图所示.

A1输出处电容: C1 = A2 gm rds Cc . 主极点:

routa为EA A1输出电阻, gm, rds为功率管

Miller补偿会产生右零点(坏零点!) right half-plane zero. 即输入通过CC forward path抵消输出, A2gm* vin − sCc *vin. 因此右零点为

可通过串联Rc电阻消除右零点

Rc = 1∕(A2gm). 或者把零点落到左半平面. 缺点是1) gm随着负载变化. 2)R随着PVT变化大, 即使R采用和功率管相同管子, load dependency也存在.

可用Ahuja compensation according to [5], 如图Fig 7.20(b) 所示. 添加一个cascode来消除RHPZ. Vout可以通过Cc反馈回上级即A1输出. A1输出不能通过Cc forward path影响Vout. 这样就消除了右零点. 也称为indirect compensation, 很实用!

次级点在LDO输出, 被Cc推远后

7.11 Flipped Voltage Follower LDO

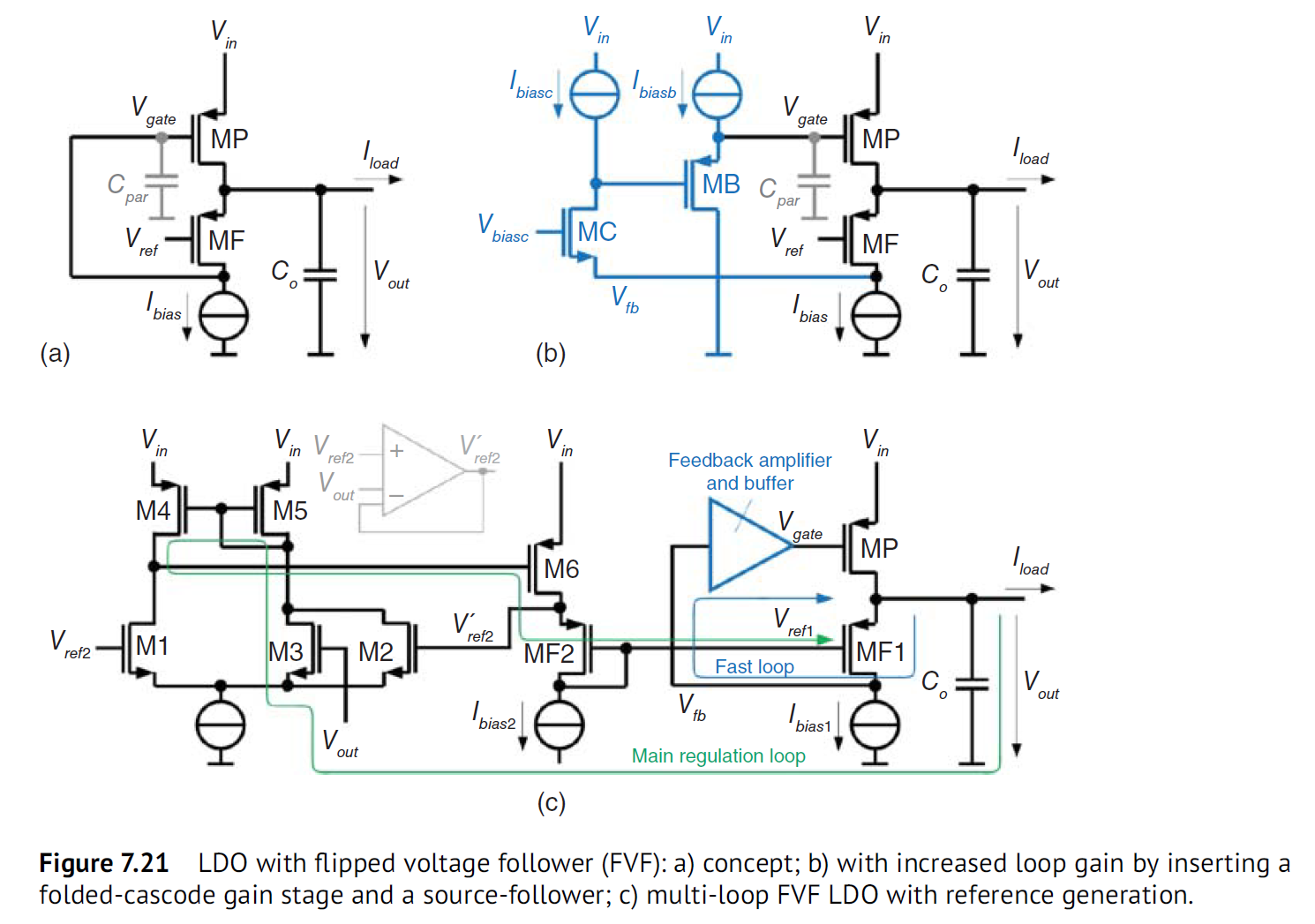

flipped voltage follower (FVF) 如下图(a)所示, 可实现快速load transient相应, 同时提供一个不错的稳态load-regulation. MP为功率管, MF和 Ibias形成了FVF.

因此Vout = Vref + Vsg,mf . 当Vout drop时, Vgate下降, 导致MP开启更多, 提供电流给Vout. MP和MF形成负反馈.

考虑(a)中的小信号负反馈模型可推导出 FVF LDO的DC Loop Gain

输出阻抗, rout

其中gm为功率管MP, gmf为MF管, rdsb为bias电流源的阻抗. DC loop大约为100 即40db, 因此load regulation不算特别高. gm ∝ Iload, 因此当iload最大时, rout达到最小值.

极点位置:

大多数FVF为Capless LDO, 因此主极点在MP的gate处, 但是也有design把主极点放在Co输出处. Co一般为片内电容, 100pF量级.

为了让主次极点分离, 可以在MP gate处加电容, 让主极点wp1更小. 在load最大时, 稳定性更有挑战.

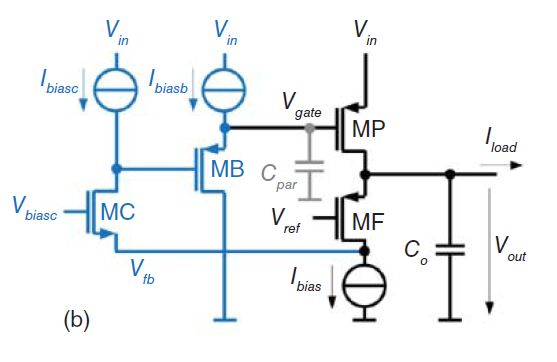

Capless FVF LDO的loop gain需要高gain-bandwidth 这样能快速响应Load transient, 可考虑(b)中结构, 添加casecode gain state. 同时添加buffer, 这样可以强力驱动MP gate处电容Cpar, 通过降低gate处r阻抗, wp1更大. 在MC的drain处引入了第三个极点. 不过(b)中结构可以关闭MP.

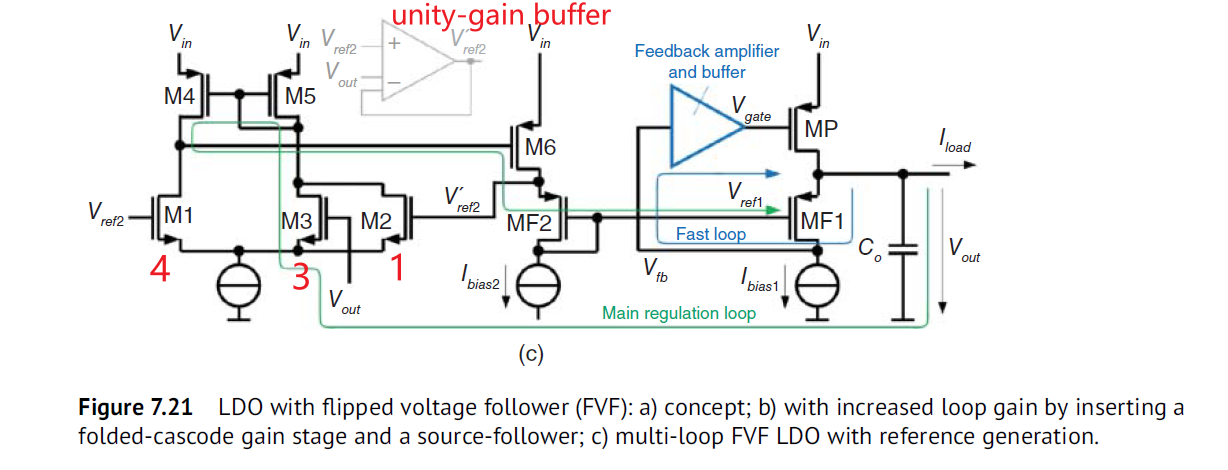

FVF LDO的 DC accuracy和load regulation不太好, 因为Vsg,mf会发生变化. ©展示了 带多环路控制的FVF LDO. M1-M6形成了带buffer能力的Vref, 如虚线框图所示. MF1和MF2的Vsg相同, 因此Vout=Vref2’=Vref2. M3的gate再接上Vout, 当Vout下降时, outer loop迅速响应, 确保Vref2’上升, 当MP gate下降, 提升load transient. The main loop bandwidth is slower than the fast FVF loop, such that the slow loop achieves excellent DC output regulation,while improved transient response is enabled by the fast high-frequency FVF loop.

参考文献 [9]A 0.65ns-response-time 3.01ps FOM fully-integrated low-dropout regulator with full-spectrum power-supply-rejection for wideband communication systems, in 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC),

7.12 The Shunt Regulator

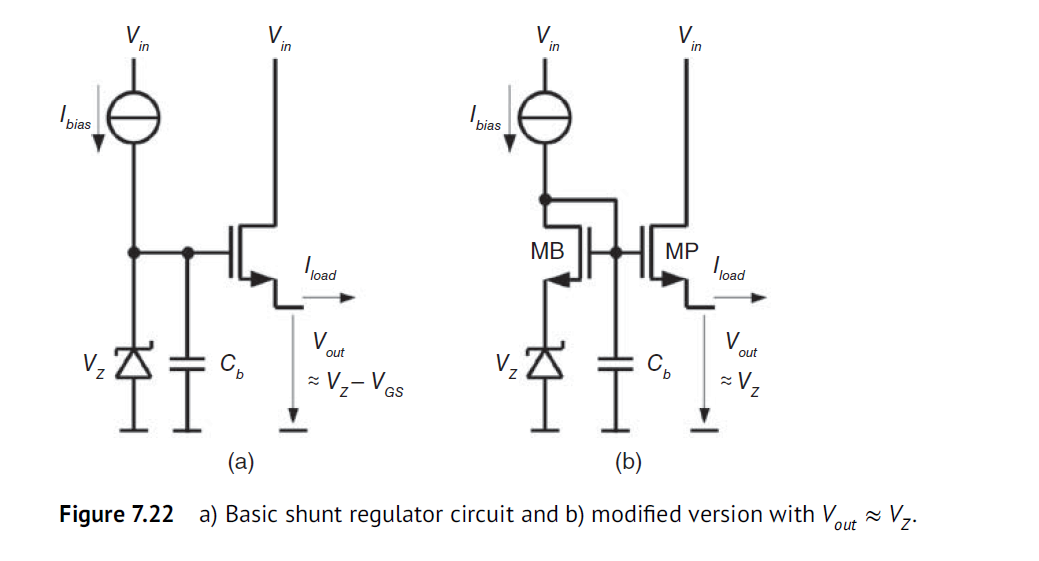

对电源要求不高的模块, 供电轨可以简单设计, 无需闭环LDO. 可用下图 Shunt Regulator结构, NMOS gate稳压, 输出Vout=Vgate-Vgs. Ibias为uA级别, MP size足够大, Vgs随着负载变化有限, Vgs变化为几百mV. 为了防止load step, Vout跌落对gate的couple, 可以在gate上放置Cb电容. 另外可以加入MB, cancel Vgs.

一般zener 管的耐压为5.5V, 如果需要Vout below 2V, 可用diode-connected NMOS替代Zener Diode. 或者用一串diode NMOS提供Vz电压.

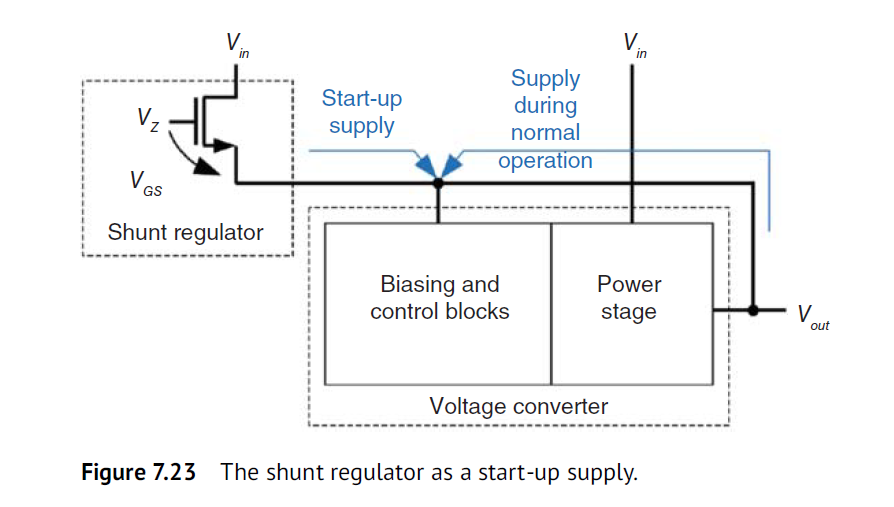

The Shunt Regulator as a Start-Up Supply

shunt regulator可作为启动电源, 等后面LDO建立好后, 再撤销掉shunt regulator. 或者LDO输出Vout比shunt regulator输出更高

7.13 Digital LDOs

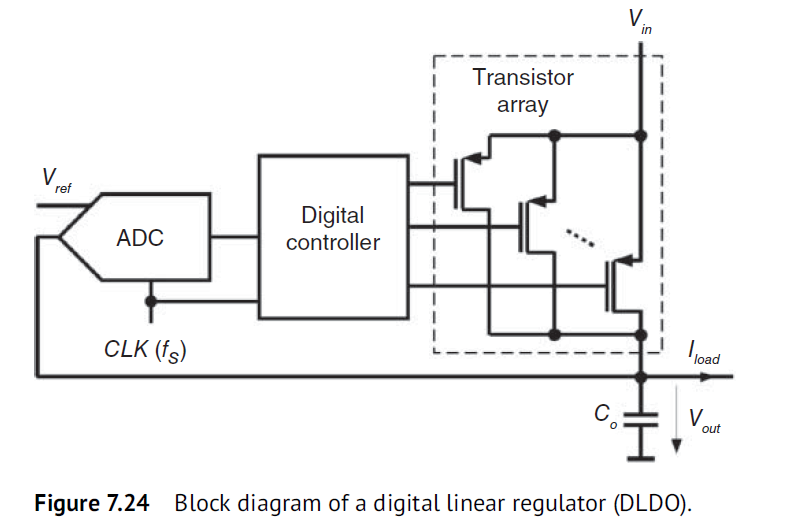

digital low-dropout regulator (DLDO) 数字LDO 如下所示, 由开关管矩阵+ADC+digital controller组成. DLDO 可用先进的CMOS工艺, 走数字流程.

7.13.1 The Transistor Array

开关管矩阵类似DAC, 很多管子fully on or off, 调节Vin到Vout的阻抗.

PMOS DLDO的功率管由于不需要工作在饱和区, 因此W/L可以取得较小. 缺点是阻抗随着Vin变化, PSR较差.

为了高PSR, 需要用NMOS DLDO, 让功率管工作在饱和区. 同样的drop voltage需要W/L更大, 另外NMOS需要charge pump.

7.13.2 The Analog-to-Digital Converter

ADC由时钟, 高速比较器, 和binary输出构成.

7.13.3 The Digital Controller

Digital control将 quantized error signal of the ADC转化为N bit的信号, 开关transistor array. 可由thermometer code (热编码), unsigned binary integer formats, or 2’s complement构成. 在数字领域, 为了快瞬态可用PID control.

7.13.4 Transient Response

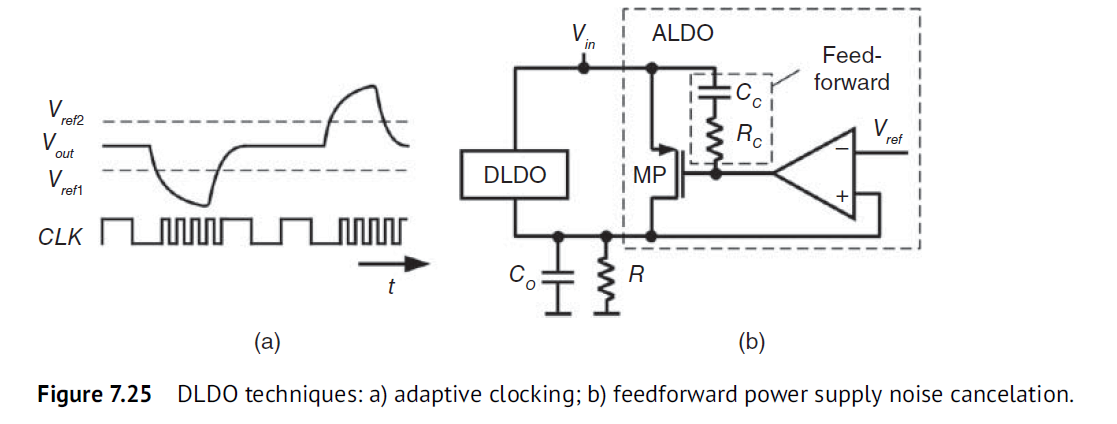

当发生快速load transient时, 由于ADC的sampling delay, Vout会延迟Vref, ADC可由synchronous (time-driven) and an asynchronous (event-driven)触发.

synchronous triggering需要2^N cycles for Vout to settle close to Vref. 因此settle time为2^N ⋅ 1∕fs

可设置Vref1和Vref2, 当Vout偏离windown后加速CLK频率. 或者采用DLDO+ALDO, 有一个feedforward path, 发生瞬态时, MP启动.

7.13.5 Power Supply Rejection

DLDO的PSR一般比ALDO差, 因为Vin到Vout的coupling由 DLDO的Ron和等效阻抗R=Vout∕Iload构成.

R越大, PSR越差. 也可用Fig 7.25中feedforward来改善PSR.

7.13.6 Limit Cycle Oscillations

由于ADC+DAC的引入, DLDO固有的limit cycle oscillations (LCO), 输出电压的频率<sampling frequency fs. Only if the digital control output forces Vout steadily to the zero error bin of the ADC LCO can be eliminated. This requirement is often fulfilled if the DAC has a higher resolution than the ADC.However,more special cases lead to LCO.

7.13.7 Summary

DLDO有几大优点: 小die 面积, process scalability, 低供电电压. 缺点是load transient响应慢, PSR, low output voltage ripple.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?