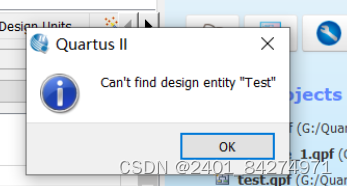

设置顶层模块:直接打开顶层模块打不开;

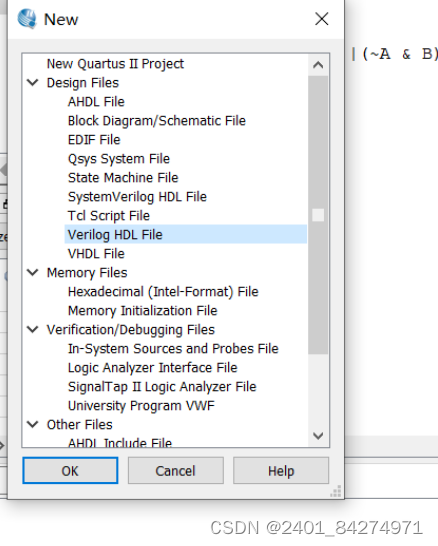

里面没有东西;需要verilog hdl 文件;

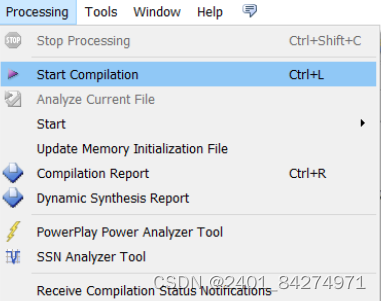

写完后也打不开需要全编译;然后就ok了。

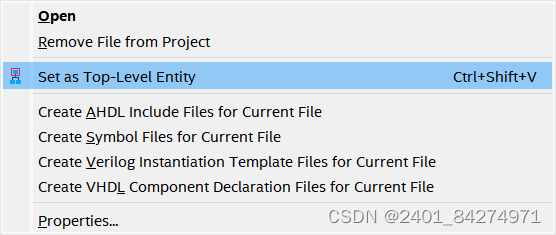

设置顶层模块;

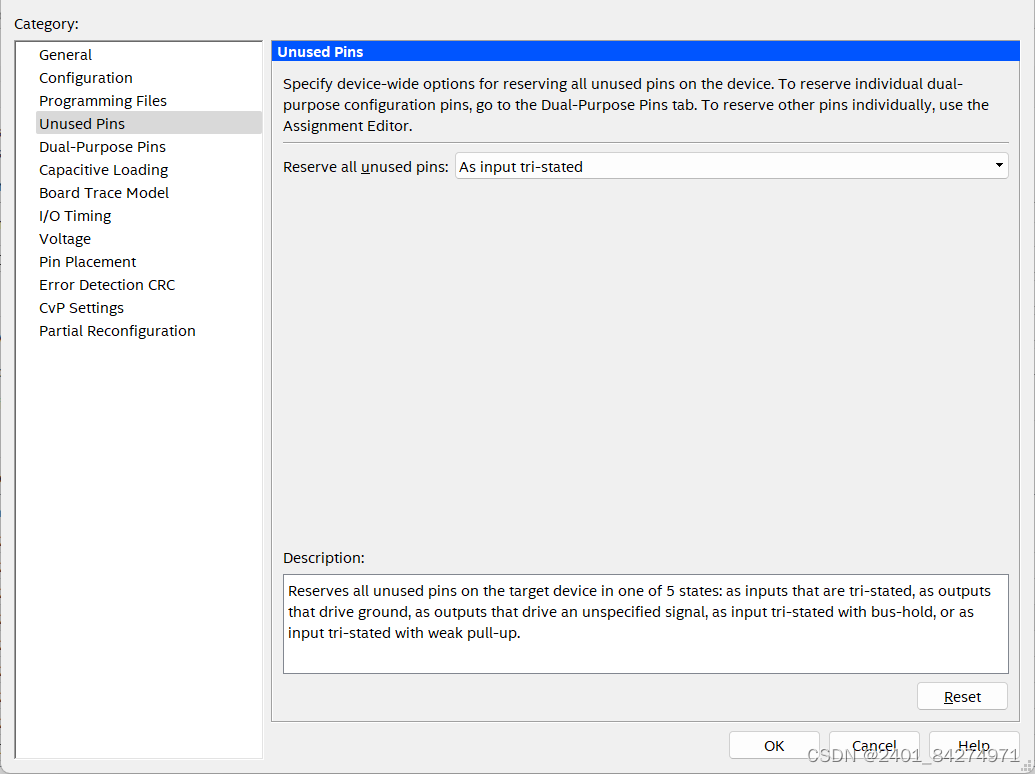

管脚分配的设置:未分配管脚设成三态

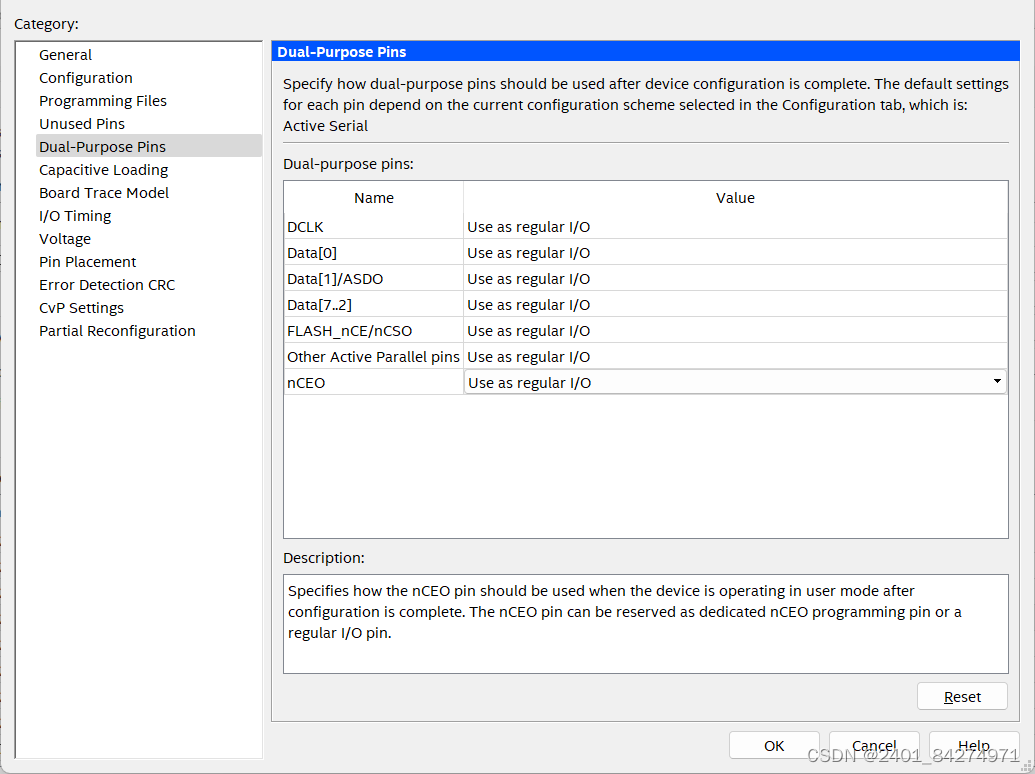

一个管脚通常多个用途,都设成i/o口;不设置有时管脚会冲突报错;

生成RTL视图

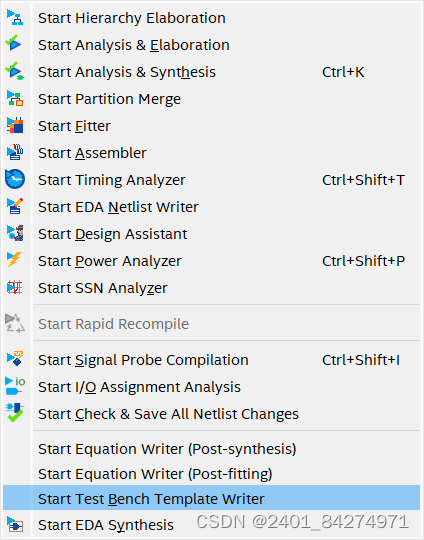

modelsim 仿真

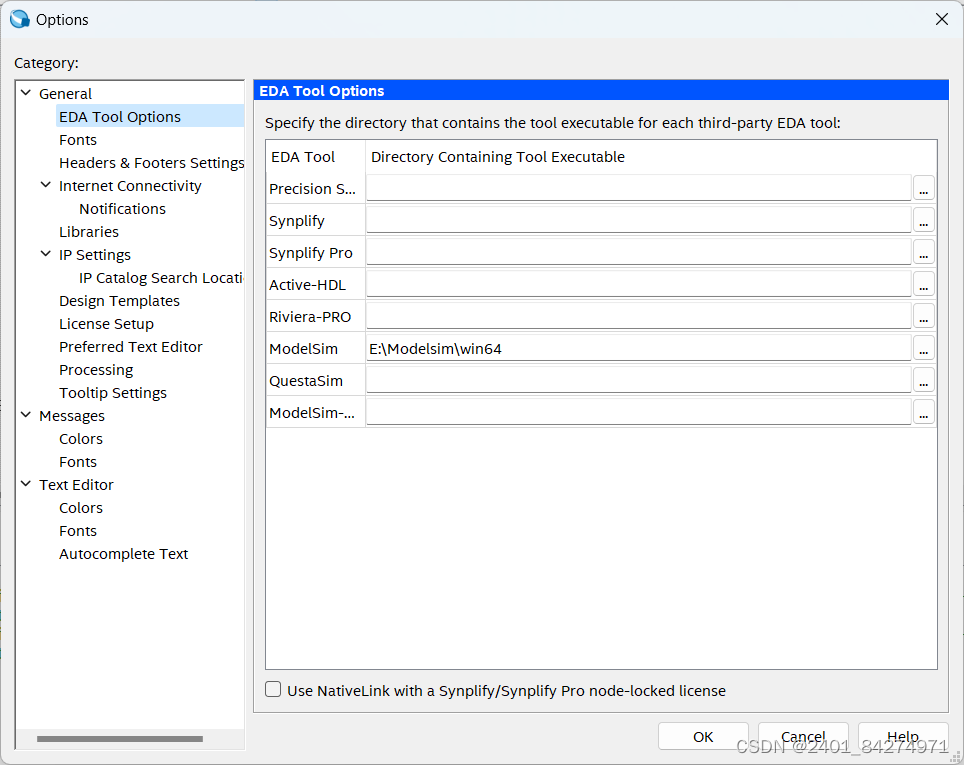

首先添加EDA工具;

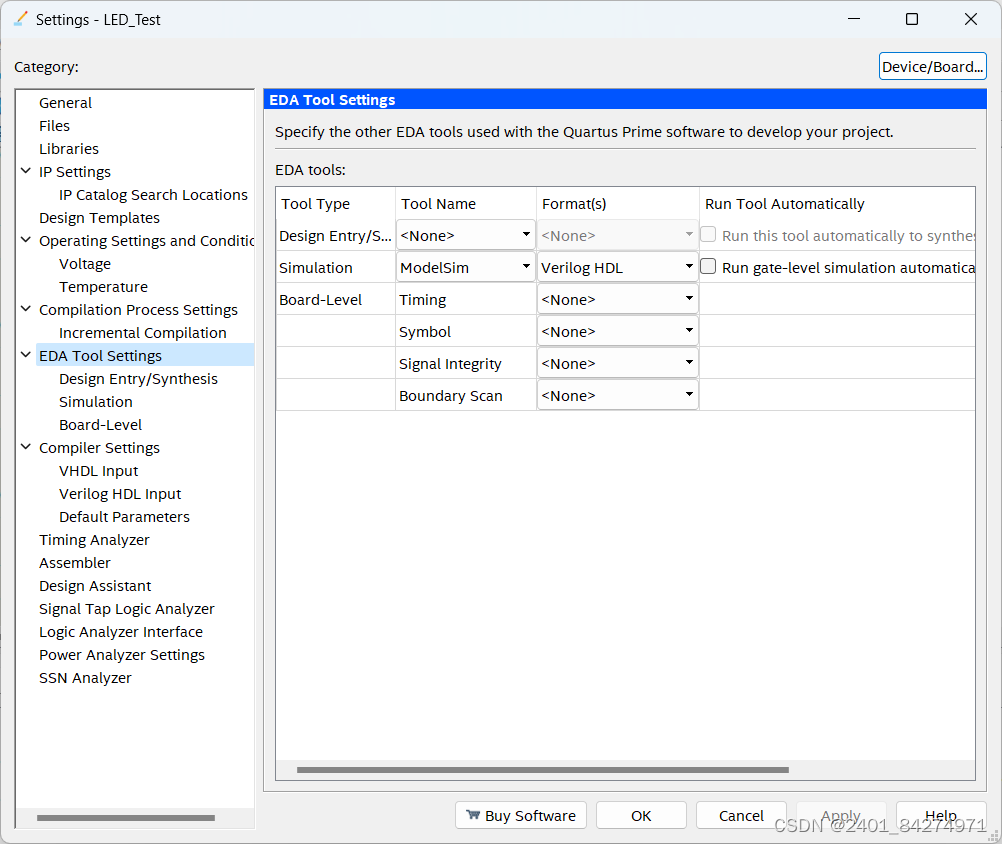

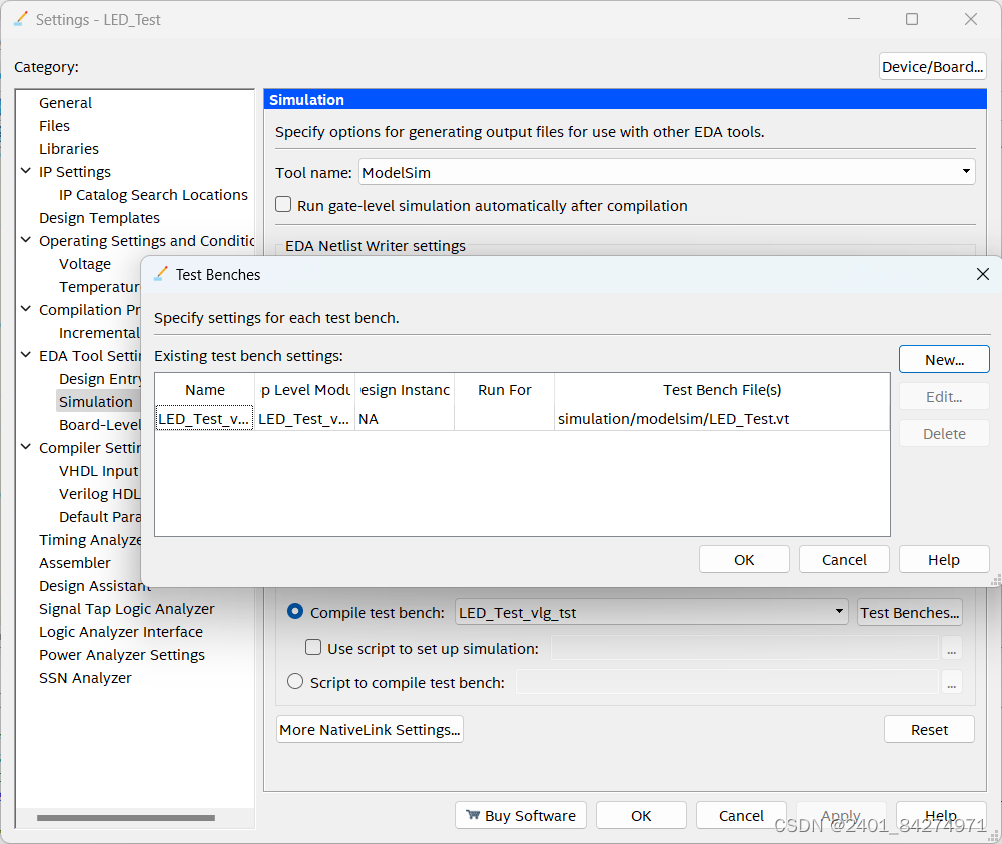

配置EDA;

编写testbench文件

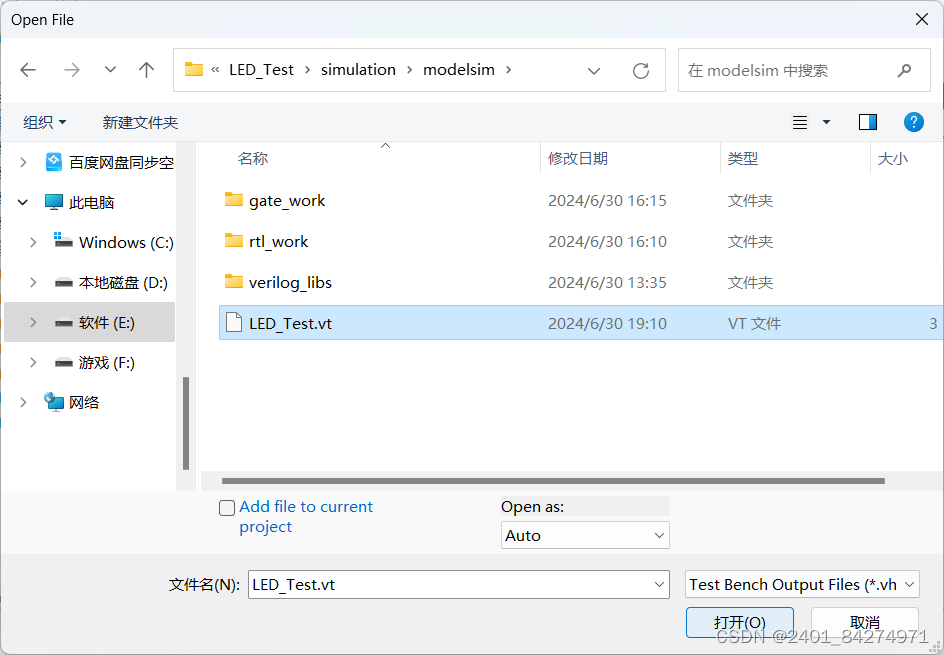

打开文件

编写激励;

单位和精度还是改成1ns好看仿真;

例化视图;

仿真功能配置;

功能仿真看逻辑;时序仿真看器件延时;

仿真的时候掉不出波形,将所有文件调到一起;出错代码Error: Error loading design ;还有就是用自带的wave进行仿真时掉不出库,解决办法是需要默认输出文件位置不能更改;生成wwf文件链接Quartus II 13.0波形仿真(解决无法产生仿真波形问题)_quartus ii波形仿真-CSDN博客

另外还是用自动仿真方便不用例化,WWF也行;

设置ip核:RAM;ROM;PLL;FIFO;DDR2

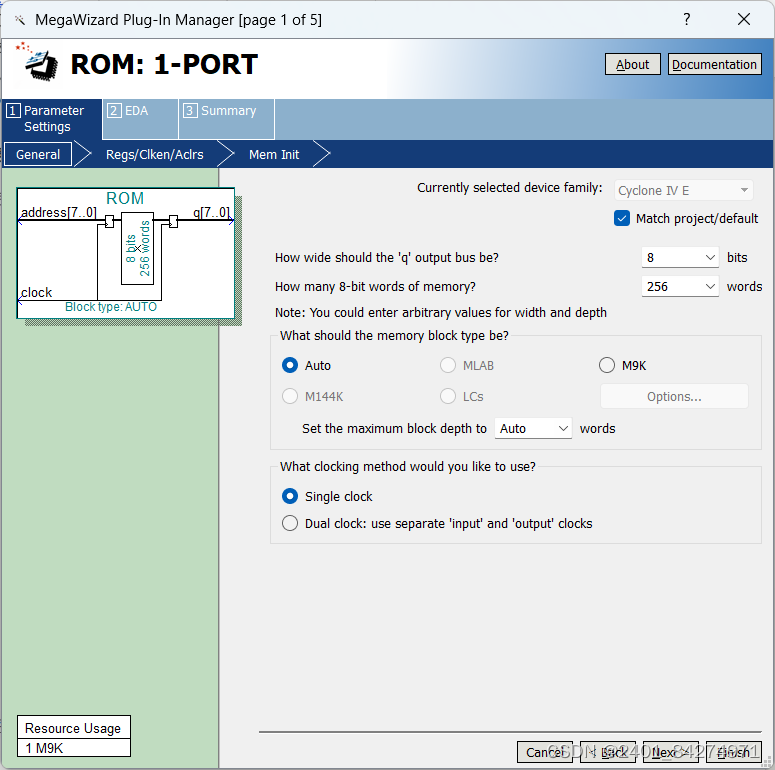

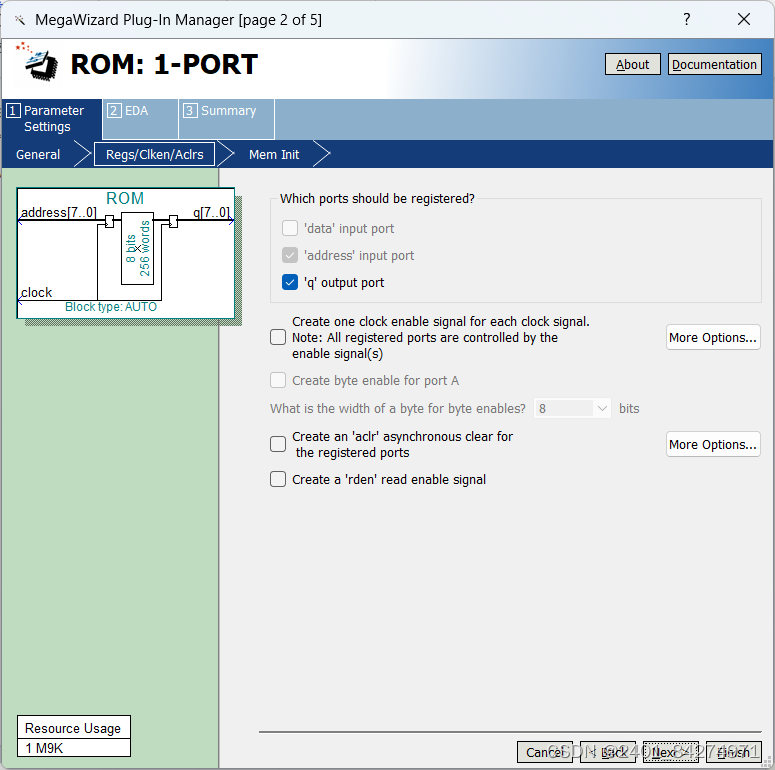

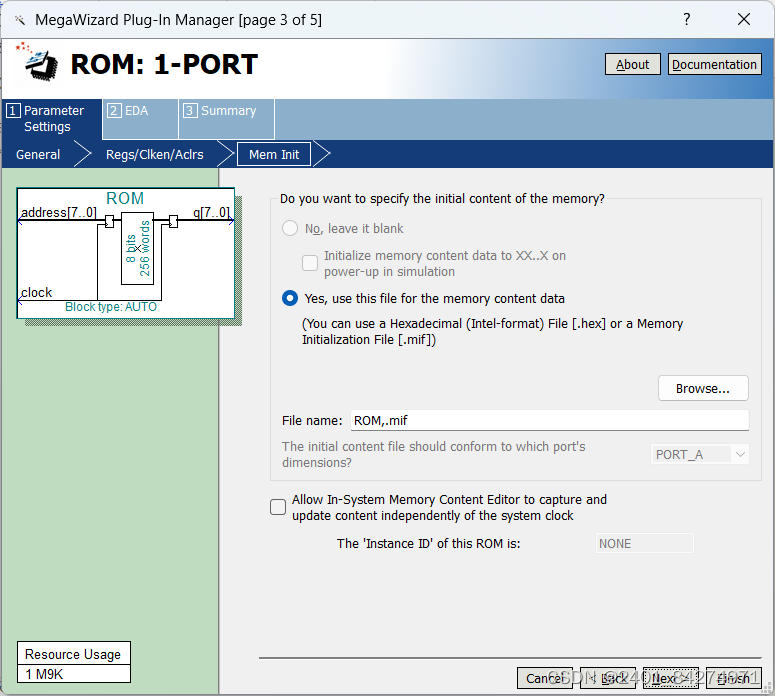

ROM(只读存贮器)

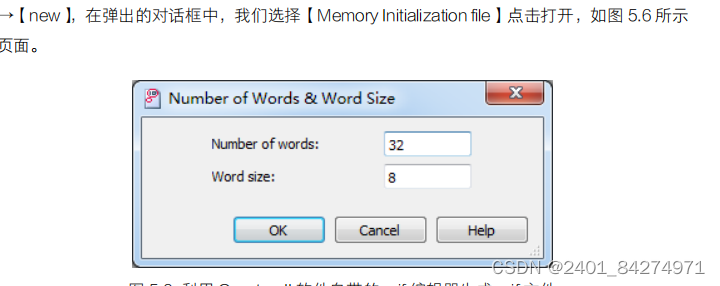

重点是生成mif文件;小容量的rom可以用自带的生成;

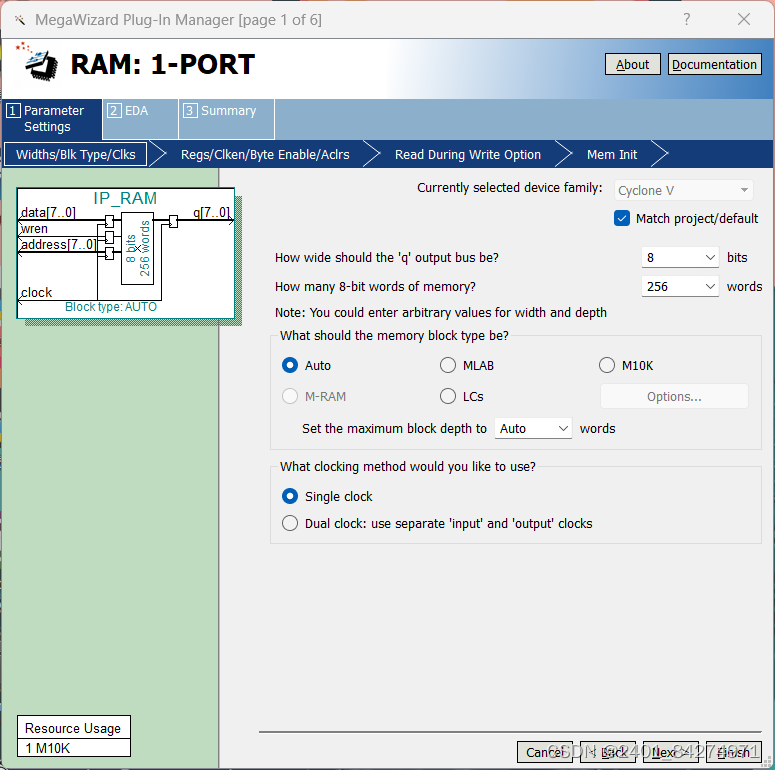

RAM(读写存储器;又能读又能写):

1.输出位宽;字节;存储块类型,一般选默认;存储深度默认;按需求选择单时钟双时钟;

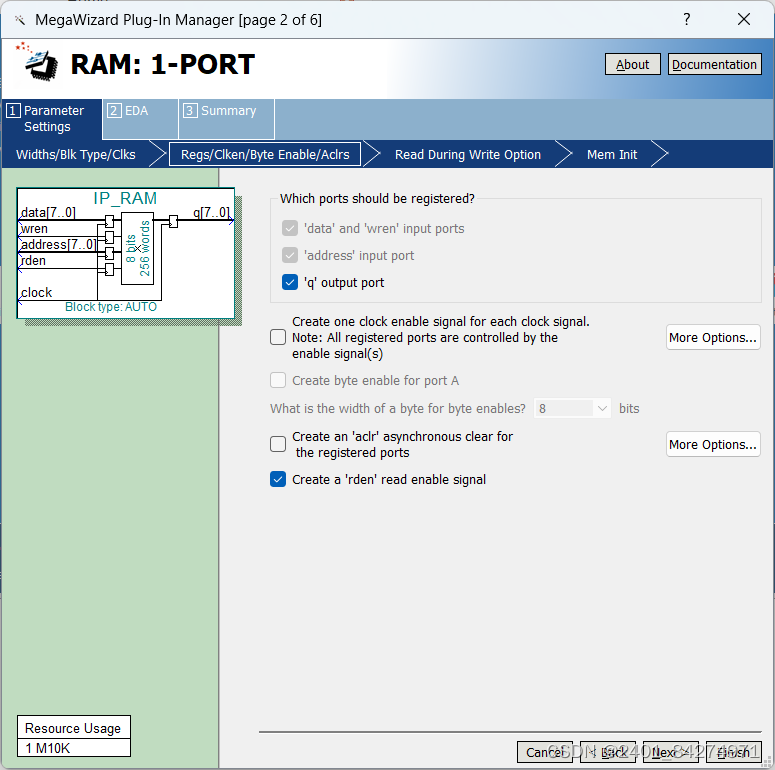

2.输出打一拍实现稳定性;时钟使能端clk_en,不选;addressstall地址使能控制不选;异步复位不选;输入输出使能端选择;

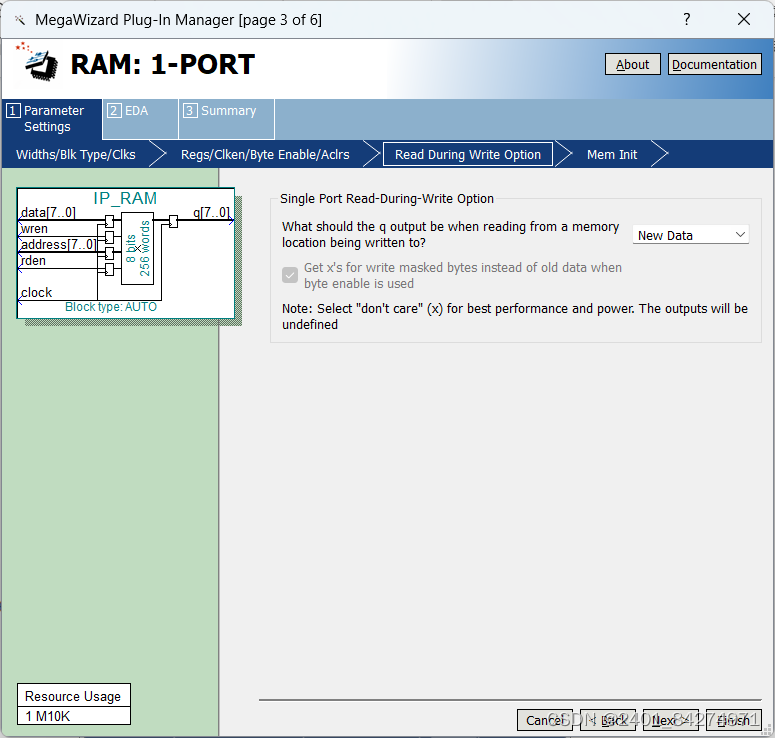

3.在写入的时候读取,读取选择新数据,don't care会导致数据不稳定;第二个默认;

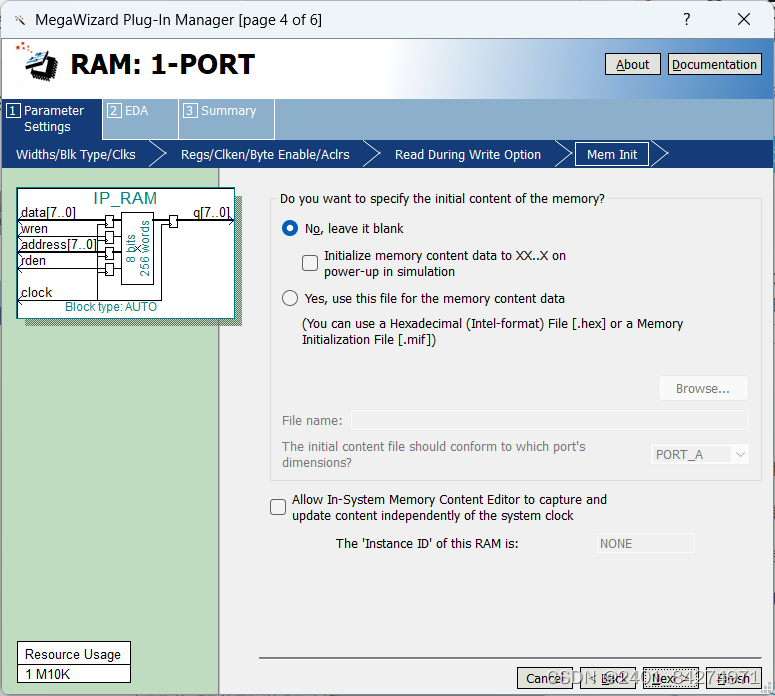

4.可以选择初始化跟ROM一样,选择yes可以往里添加初始化数据,mif文件使用matlab生成,第二个选择可以在线调试;

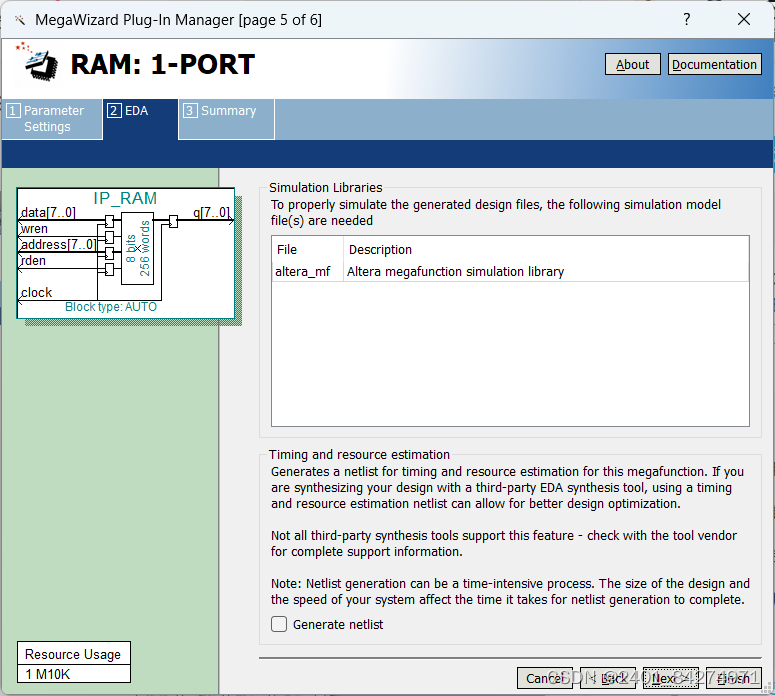

5.默认;

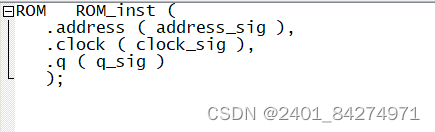

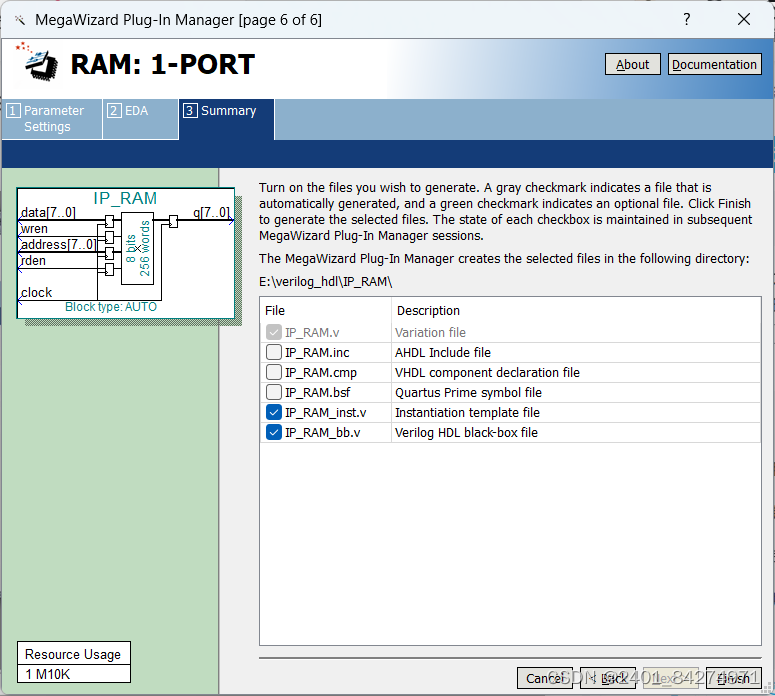

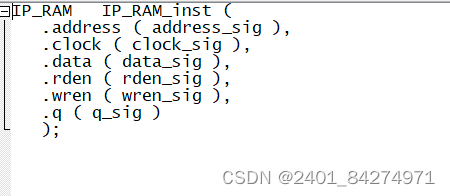

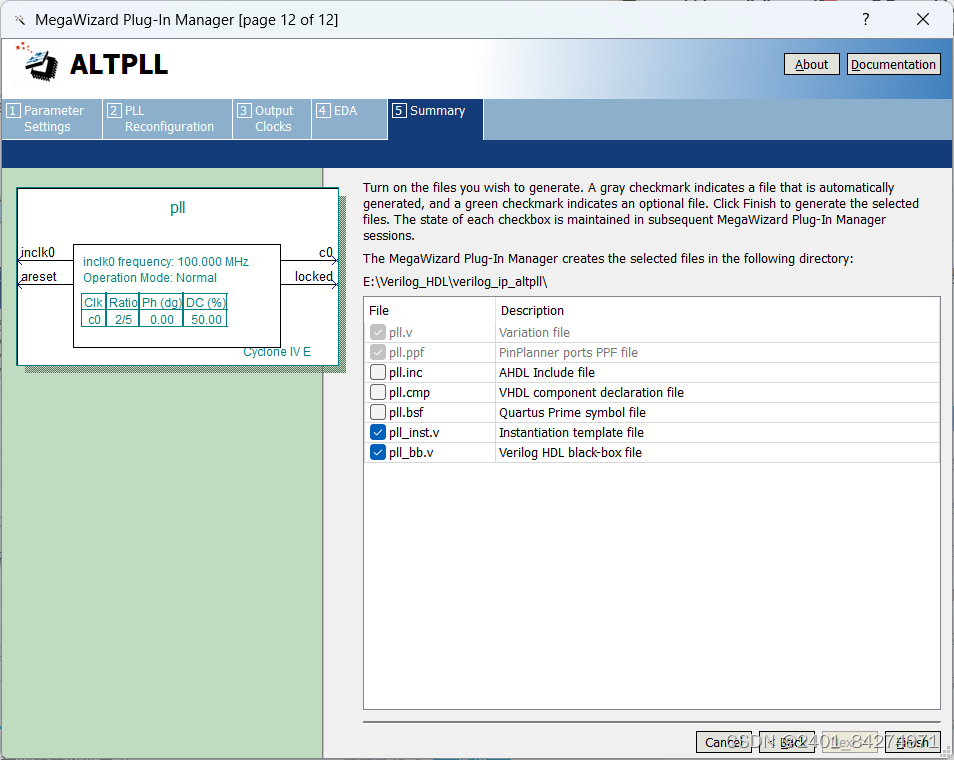

6.勾选inst文件,是例化模板;

7.生成inst模板复制即可;

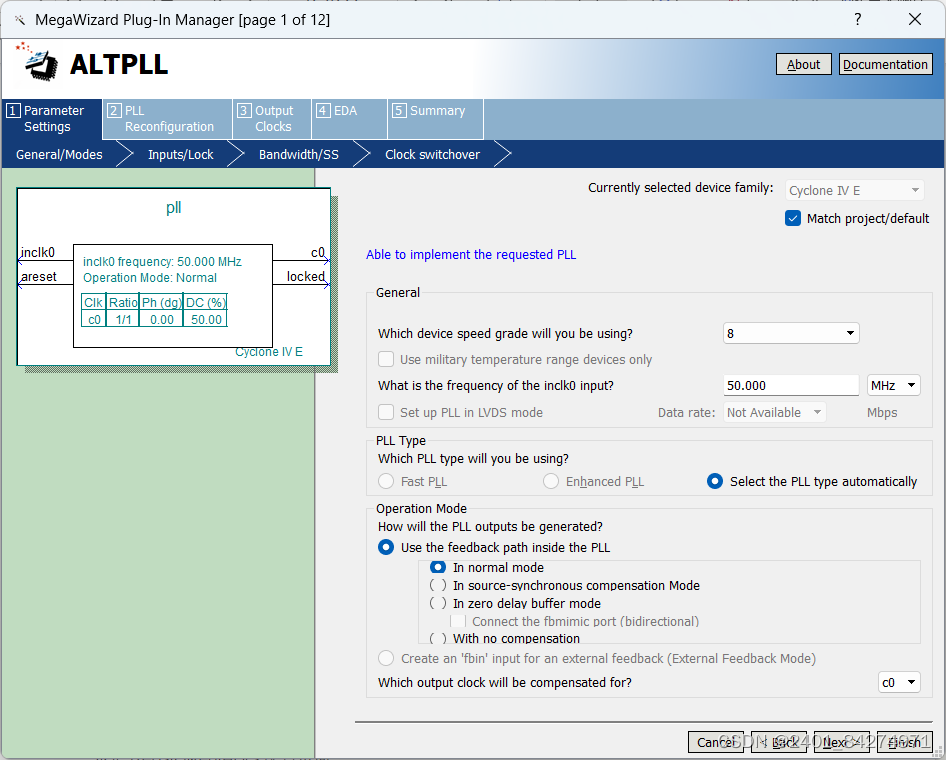

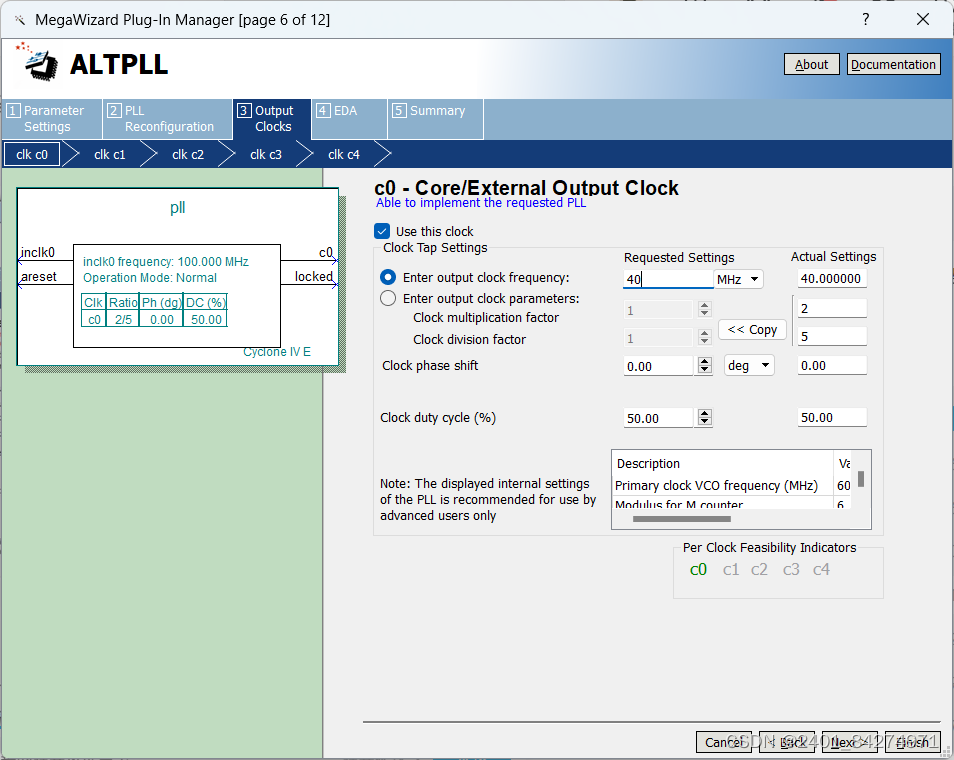

ALTPLL(分频)

1.速度等级,晶振匹配开发板;下面两个默认;

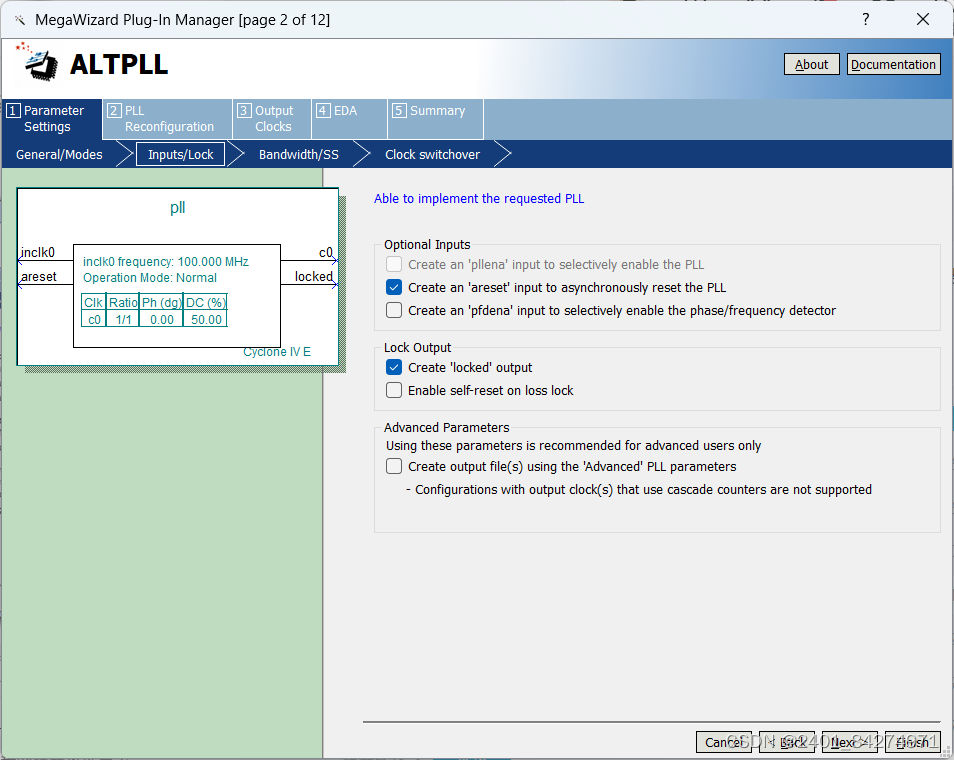

2.异步复位;locked选上更加稳定;

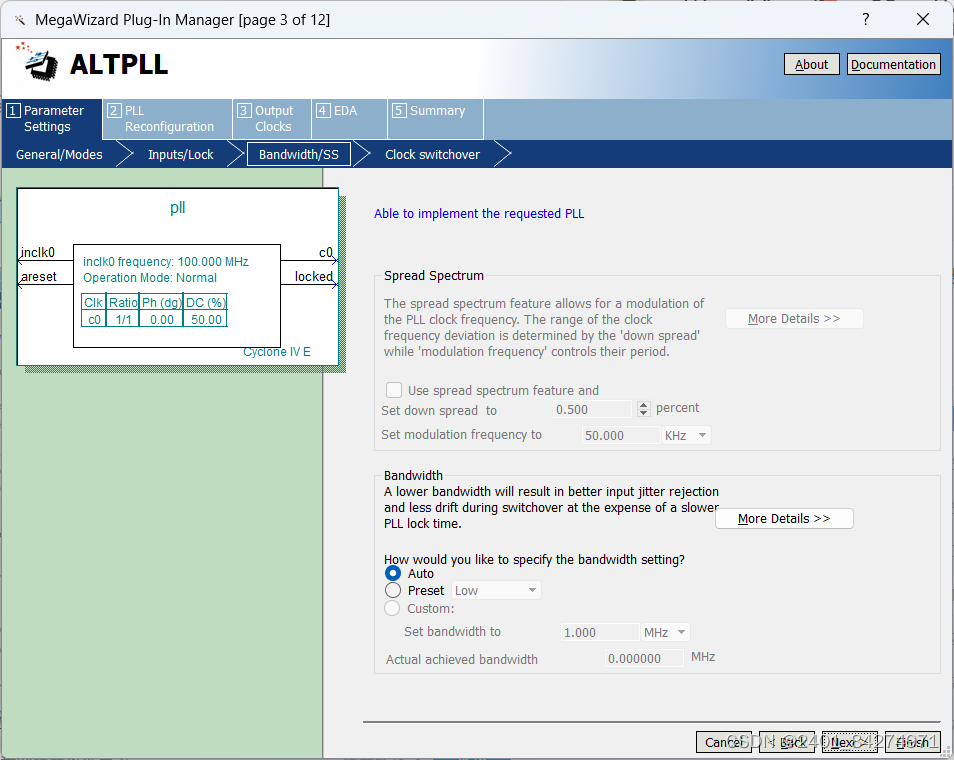

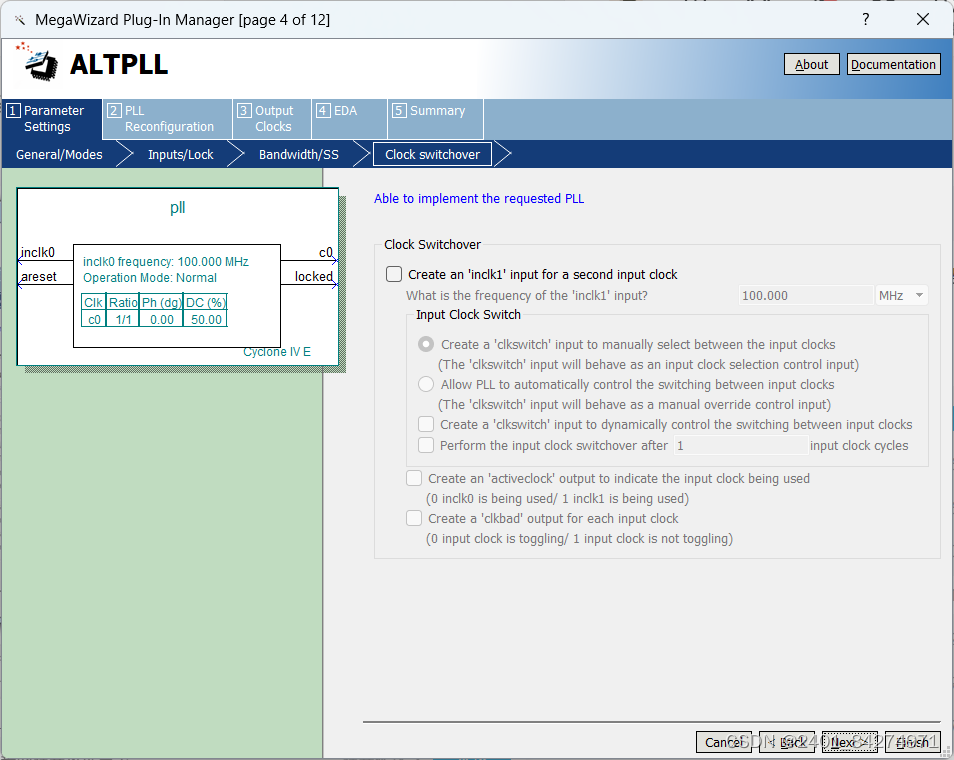

3.默认;

4.默认;

改变频率;

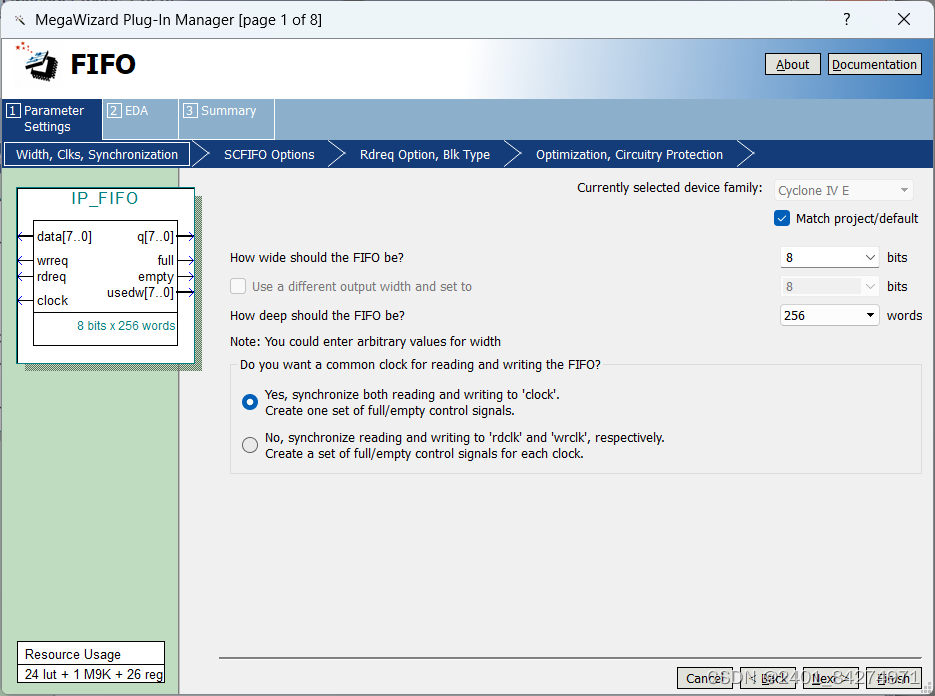

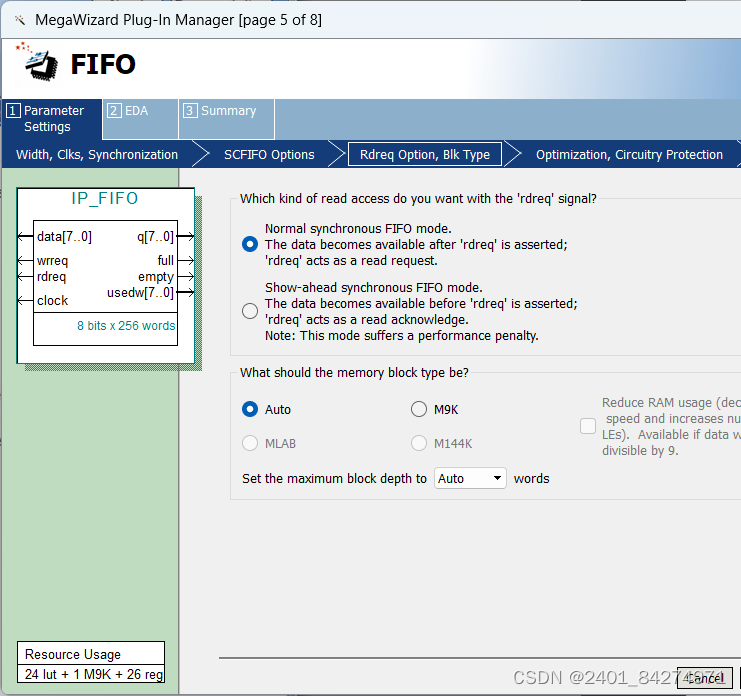

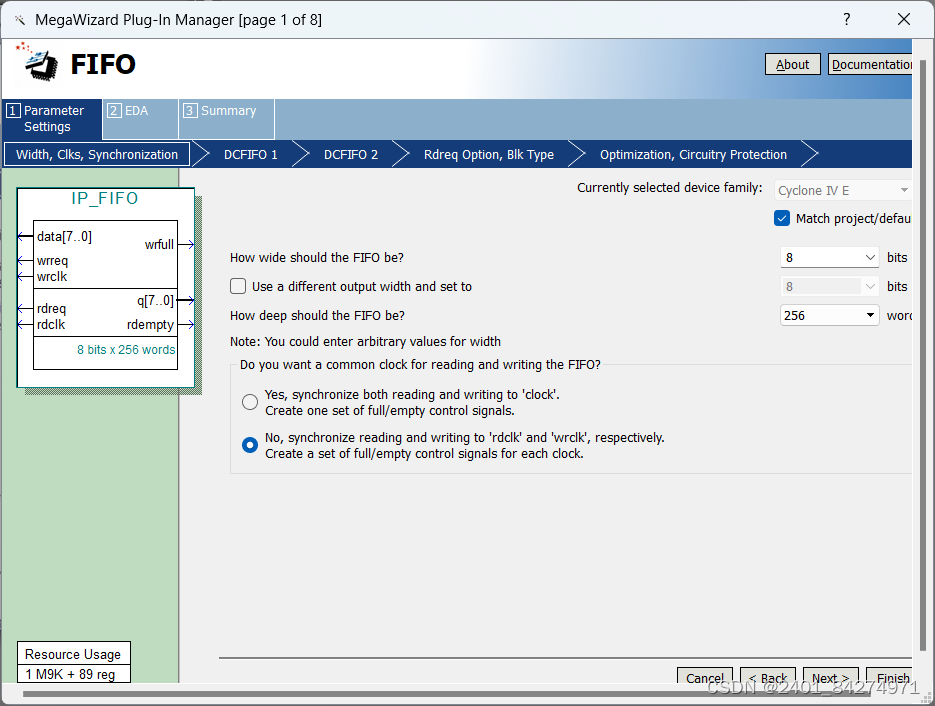

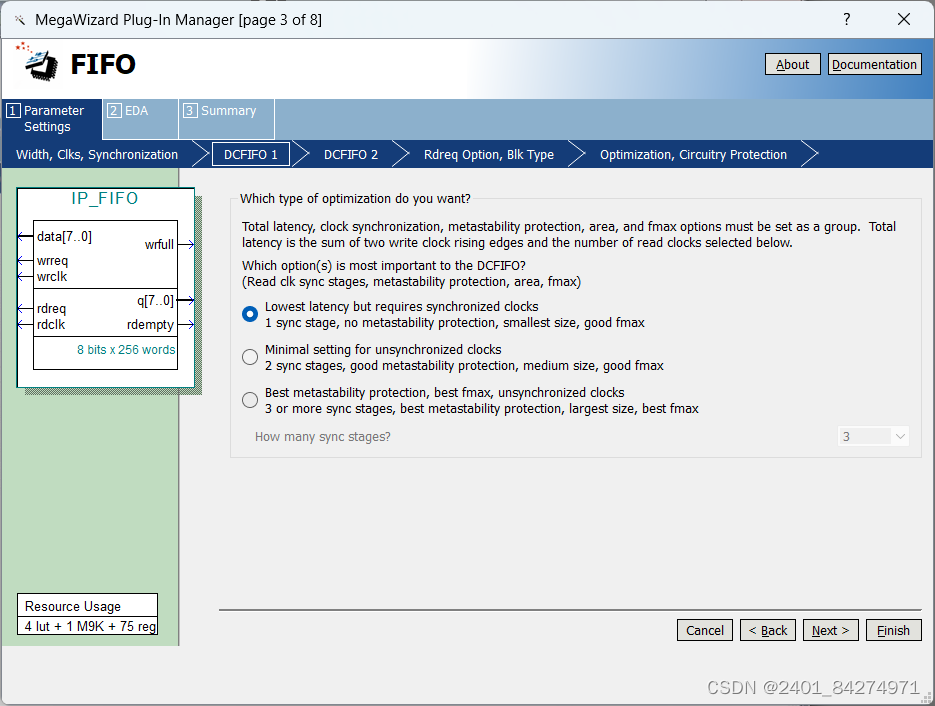

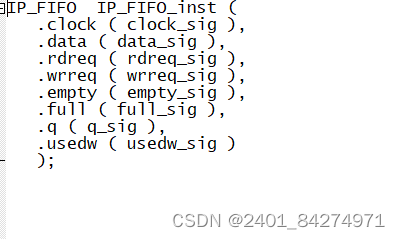

FIFO(不同时钟域数据桥梁,先进先出存储器,)设置

两种模式:

第一种同步读写:

第二种模式:不同时钟域:

DA FPGA 的输出端口更直观的接口;

955

955

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?