本实验报告涉及9个实验内容,均为包括电子电路仿真方法与门电路实验、门电路基础、组合逻辑电路设计、编码器及其应用、译码器及其应用、数据选择器、触发器、逻辑电路综合设计、计算器及其应用等。

部分实验截图未加载出来,完整版实验报告及实验过程等见附带资源

| 实验项目 | 实验一 电子电路仿真方法与门电路实验 | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 一、实验目的 1.熟悉电路仿真软件Multisim的安装与使用方法。 2.验证常用集成逻辑门电路的逻辑功能。 3.掌握各种门电路的逻辑符号。 4.了解集成电路的外引线排列及其使用方法。 5. 学会用Multisim设计子电路。 |

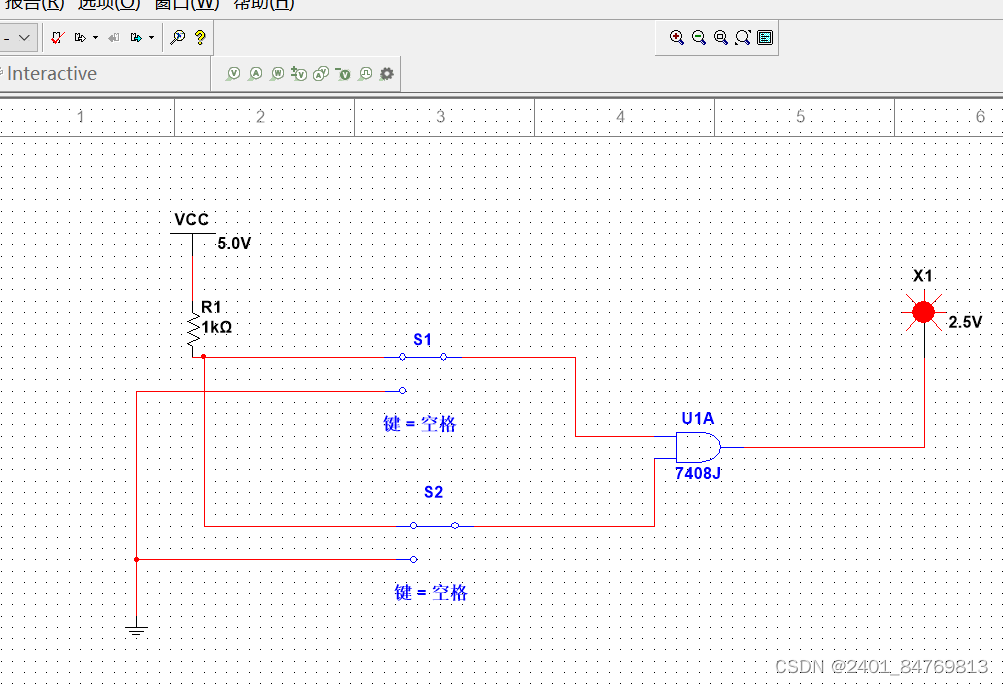

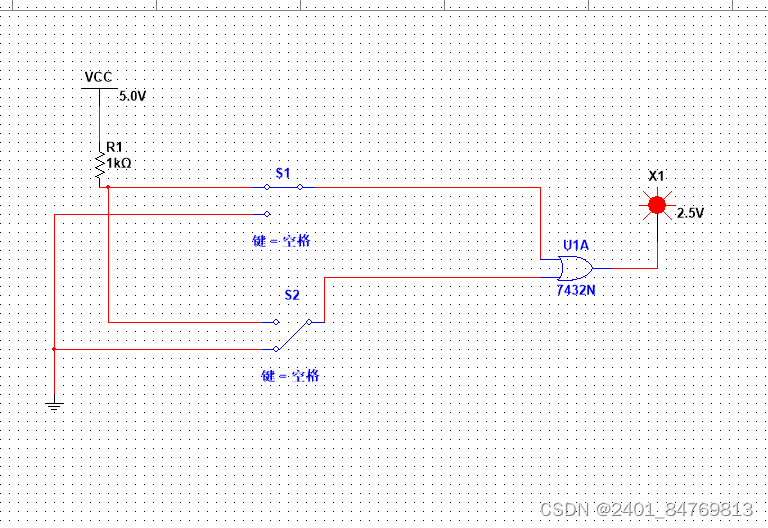

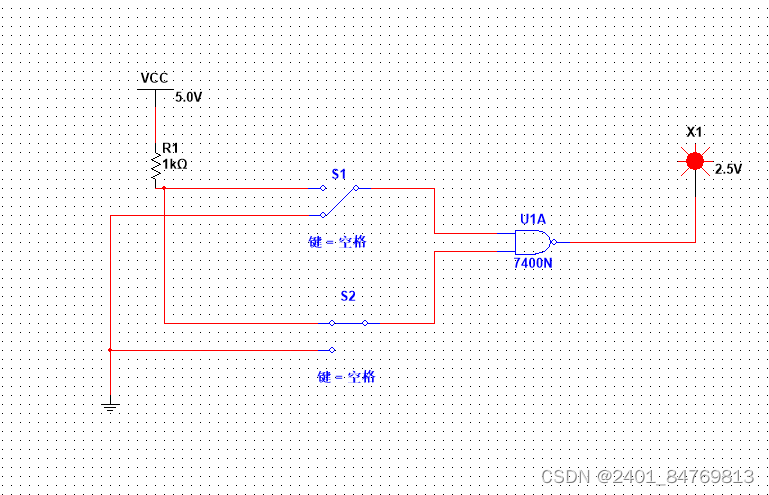

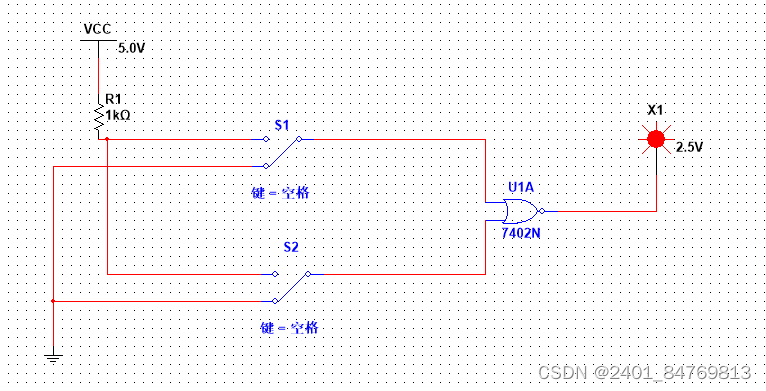

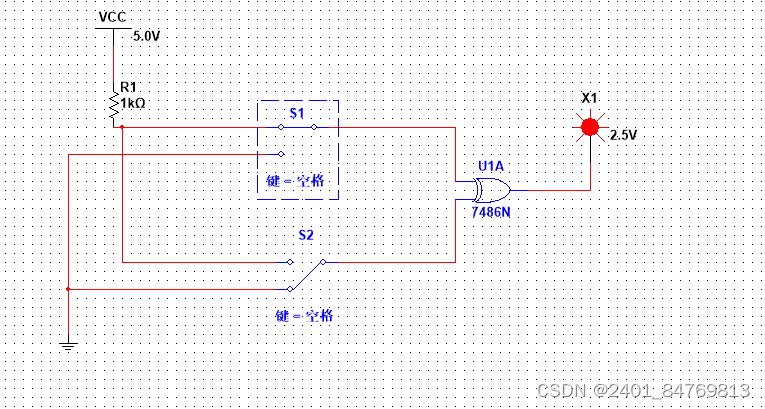

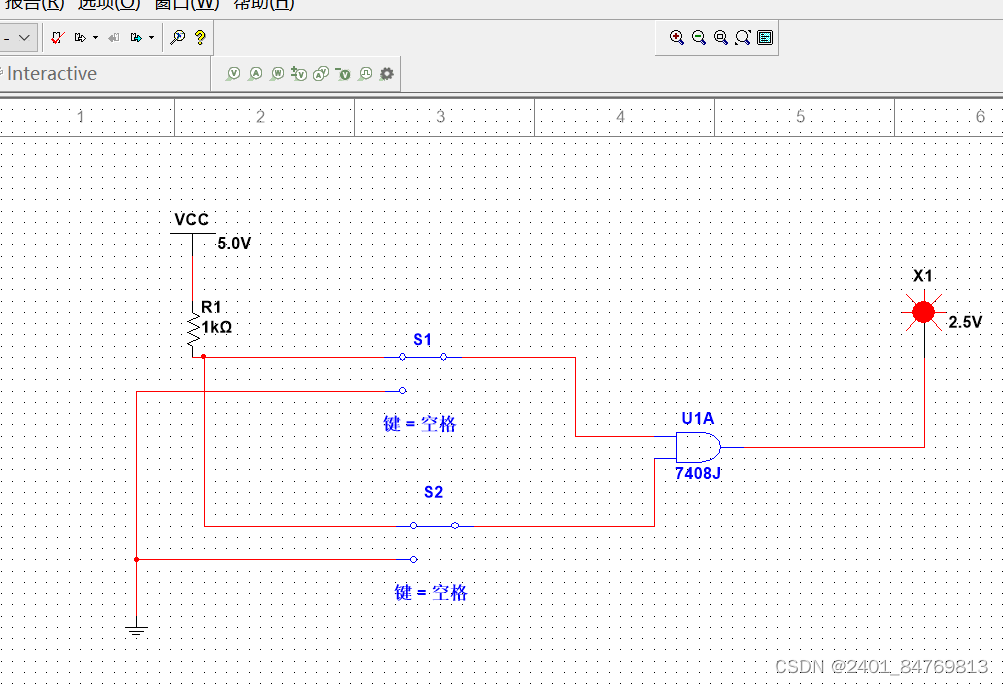

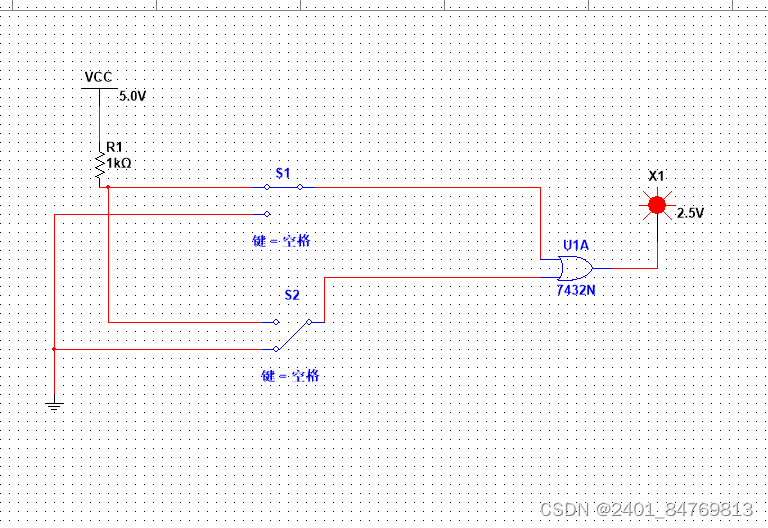

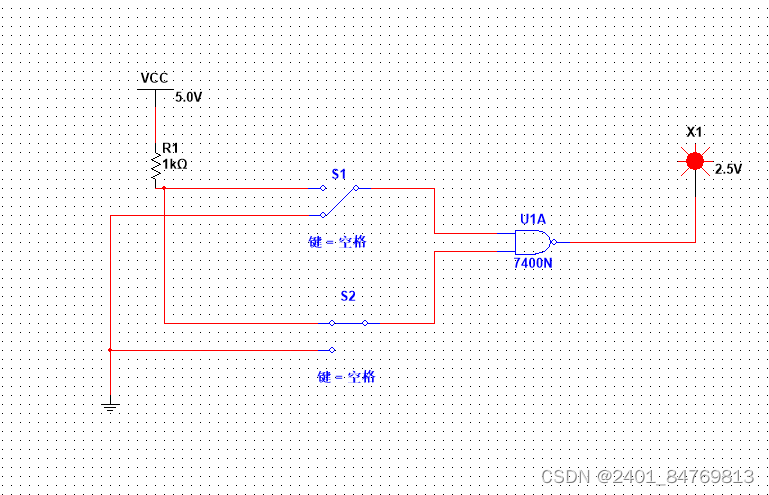

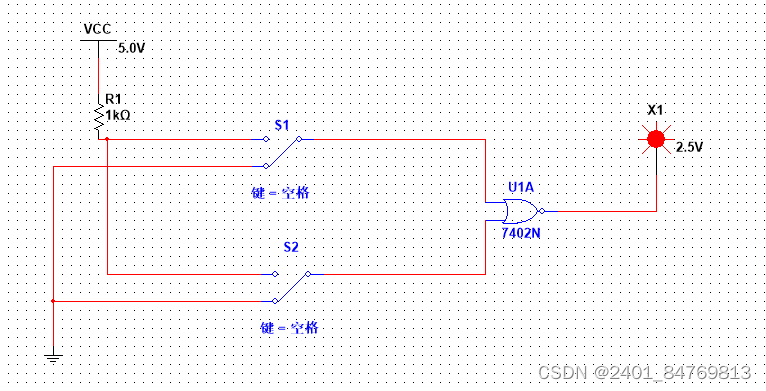

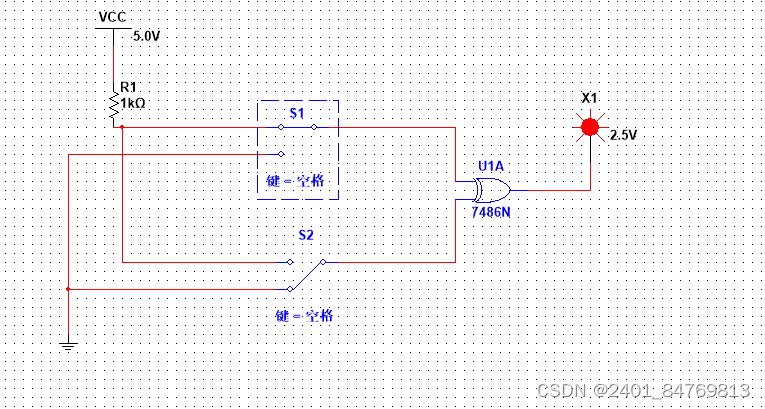

| 实验内容或结果 | 1.用逻辑门电路库中的集成逻辑门电路分别验证二输入与门、或非门、异或门和反相器的逻辑功能,将验证结果填入表1.1中。 注:与门型号7408,或门7432,与非门7400,或非门7402,异或门7486,反相器7404. 表1.1 门电路逻辑功能表

| 输 入 | 输 出 | | 与门 | 或门 | 与非门 | 或非门 | 异或门 | 反相器 | | B | A | L=AB | L=A+B |

|

|

|

| | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

|

| 实验内容或结果 | 2.用2输入与门7408和4输入与非门7420设计一个8输入与非门子电路,实现 表1.2 8输入与非门逻辑功能表

| 输 入 | 输 出L | | A | B | C | D | E | F | G | H | | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

|

| 思考或体会 |

- 寻找元器件速度慢,操作不熟练。

- 运行完电路需要及时按停止键停止运行。

- 连接电路过程中线路不够简洁美观。

|

| 备注 | |

| | 实验二 门电路基础 | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 1. 掌握CMOS反相器、与非门、或非门的构成与工作原理。 2. 熟悉CMOS传输门的使用方法。 3. 了解漏极开路的门电路使用方法。 |

| 实验内容或结果 | 1. 用一个NMOS和一个PMOS构成一个CMOS反相器,实现Y=A’。给出电路图,分析其工作原理,测试其逻辑功能填入表2-1。 表2-1 CMOS反相器逻辑功能表

2. 用2个NMOS和2个PMOS构成一个CMOS与非门,实现Y=(AB)’。给出电路图,分析其工作原理,测试其逻辑功能填入表2-2。 表2-2 CMOS与非门逻辑功能表

| 输 入 | 输 出 | | A | B | Y | | 0 | 0 | 1 | | 0 | 1 | 1 | | 1 | 0 | 1 | | 1 | 1 | 0 |

3. 用2个NMOS和2个PMOS构成一个CMOS或非门,实现Y=(A+B)’。给出电路图,分析其工作原理,测试其逻辑功能填入表2-3。 表2-3 CMOS或非门逻辑功能表

| 输 入 | 输 出 | | A | B | Y | | 0 | 0 | 1 | | 0 | 1 | 0 | | 1 | 0 | 0 | | 1 | 1 | 0 |

4. 用CMOS传输门和反相器构成异或门,实现 。给出电路图,测试其逻辑功能填入表2-4。 |

| 实验内容或结果 | 表2-4 异或门逻辑功能表

| 输 入 | 输 出 | | A | B | Y | | 0 | 0 | 0 | | 0 | 1 | 1 | | 1 | 0 | 1 | | 1 | 1 | 0 |

5. 用1片漏极开路的2输入端CMOS与非门电路74HC01D实现与或非门Y=(AB+CD+EF+GH)’,给出电路图,并测试其逻辑功能填入表2-5。

表2-5与或非门逻辑功能表

| 输 入 | 输 出Y | | A | B | C | D | E | F | G | H | | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

|

| 思考或体会 |

- 掌握CMOS的各种逻辑功能的实现。

- 认识并选择合适的、正确的元器件。

- 学会使用各种门电路。

|

| 备注 | |

| 实验项目 | 实验三 组合逻辑电路设计(一) | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 1. 掌握组合逻辑电路的设计方法 2. 掌握全加器的逻辑功能 3. 了解七段显示数码管的原理及显示译码器的设计方法。 |

| 实验内容或结果 | 1. 设计一个1位全加器电路,写出各输出端的逻辑表达式,给出电路图并验证其逻辑功能填入表2.1中。 S=A⊕B⊕Ci Co=(A⊕B)Ci+AB |

| 实验内容或结果 | 表2.1 全加器逻辑功能表

| 输 入 | 输 出 | | A | B | Ci-1 | S | Co | | 0 | 0 | 0 | 0 | 0 | | 0 | 1 | 0 | 1 | 0 | | 1 | 0 | 0 | 1 | 0 | | 1 | 1 | 0 | 0 | 1 | | 0 | 0 | 1 | 1 | 0 | | 0 | 1 | 1 | 0 | 1 | | 1 | 0 | 1 | 0 | 1 | | 1 | 1 | 1 | 1 | 1 |

|

| 思考或体会 |

- 电路设计要先对问题进行分析,列出真值表。

- 然后写出真值表对应的函数表达式并化简。

- 接着选择元器件的类型。

- 画出逻辑图最后进行模拟连接电路。

|

| 备注 | |

| 实验项目 | 实验四 编码器及其应用 | 日期 | | |

| 实验环境 | Multisim | 成绩评定 | | |

| 实验目的和要求 | 掌握优先编码器的逻辑功能,学会编码器的级联扩展应用。 | |

| 实验内容或结果 |

- 验证优先编码器74148的逻辑功能,给出接线电路图,并按表4.1输入编码信号,将各输出端测试结果填入表4.1中。

表4.1 优先编码器74148逻辑功能表

| 输 入 | 输 出 | | S’ | I’7 | I’6 | I’5 | I’4 | I’3 | I’2 | I’1 | I’0 | Y’2 | Y’1 | Y’0 | Y’S | Y’EX | | 1 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 1 | 1 | 1 | 1 | 1 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | | 0 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 0 | 0 | 0 | 1 | 0 | | 0 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 0 | 0 | 1 | 1 | 0 | | 0 | 1 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | 0 | 1 | 0 | 1 | 0 | | 0 | 1 | 1 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | 0 | 1 | 1 | 1 | 0 | | 0 | 1 | 1 | 1 | 1 | 0 | ╳ | ╳ | ╳ | 1 | 0 | 0 | 1 | 0 | | 0 | 1 | 1 | 1 | 1 | 1 | 0 | ╳ | ╳ | 1 | 0 | 1 | 1 | 0 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | ╳ | 1 | 1 | 0 | 1 | 0 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

- 用2片74148级联扩展实现16线-4线编码器的逻辑功能,画出逻辑电路图,给出Multisim接线电路图,并验证其逻辑功能填入表4.2。设编码输入信号为A’15~A’0,编码输出信号为高电平有效的Z3~Z0。

表4.2 16线-4线优先编码器逻辑功能表

| 输 入 | 输 出 | | S’ | A’15 | A’14 | A’13 | A’12 | A’11 | A’10 | A’9 | A’8 | A’7 | A’6 | A’5 | A’4 | A’3 | A’2 | A’1 | A’0 | Z3 | Z2 | Z1 | Z0 | | 1 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 0 | 0 | 0 | 0 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | | 0 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 1 | 1 | 1 | 1 | | 0 | 1 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 1 | 1 | 0 | 1 | | 0 | 1 | 1 | 1 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 1 | 0 | 1 | 1 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 1 | 0 | 0 | 1 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | ╳ | 0 | 1 | 1 | 1 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | ╳ | ╳ | ╳ | ╳ | ╳ | 0 | 1 | 0 | 1 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | ╳ | ╳ | ╳ | 0 | 0 | 1 | 1 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | ╳ | 0 | 0 | 0 | 1 | | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

- 用4片74148级联扩展实现32线-5线编码器的逻辑功能,画出逻辑电路图,给出Multisim接线电路图,并验证其逻辑功能填入表4.3。设编码输入信号为A’31~A’0,编码输出信号为高电平有效的Z4~Z0。

| |

| 实验内容或结果 |

| 输入最高优先级有效信号 | 输 出 | | Z4 | Z3 | Z2 | Z1 | Z0 | | A’31=0 | 1 | 1 | 1 | 1 | 1 | | A’30=0 | 1 | 1 | 1 | 1 | 0 | | A’29=0 | 1 | 1 | 1 | 0 | 1 | | A’28=0 | 1 | 1 | 1 | 0 | 0 | | A’27=0 | 1 | 1 | 0 | 1 | 1 | | A’26=0 | 1 | 1 | 0 | 1 | 0 | | A’25=0 | 1 | 1 | 0 | 0 | 1 | | A’24=0 | 1 | 1 | 0 | 0 | 0 | | A’23=0 | 1 | 0 | 1 | 1 | 1 | | A’22=0 | 1 | 0 | 1 | 1 | 0 | | A’21=0 | 1 | 0 | 1 | 0 | 1 | | A’20=0 | 1 | 0 | 1 | 0 | 0 | | A’19=0 | 1 | 0 | 0 | 1 | 1 | | A’18=0 | 1 | 0 | 0 | 1 | 0 | | A’17=0 | 1 | 0 | 0 | 0 | 1 | | A’16=0 | 1 | 0 | 0 | 0 | 0 | | A’15=0 | 0 | 1 | 1 | 1 | 1 | | A’14=0 | 0 | 1 | 1 | 1 | 0 | | A’13=0 | 0 | 1 | 1 | 0 | 1 | | A’12=0 | 0 | 1 | 1 | 0 | 0 | | A’11=0 | 0 | 1 | 0 | 1 | 1 | | A’10=0 | 0 | 1 | 0 | 1 | 0 | | A’9=0 | 0 | 1 | 0 | 0 | 1 | | A’8=0 | 0 | 1 | 0 | 0 | 0 | | A’7=0 | 0 | 0 | 1 | 1 | 1 | | A’6=0 | 0 | 0 | 1 | 1 | 0 | | A’5=0 | 0 | 0 | 1 | 0 | 1 | | A’4=0 | 0 | 0 | 1 | 0 | 0 | | A’3=0 | 0 | 0 | 0 | 1 | 1 | | A’2=0 | 0 | 0 | 0 | 1 | 0 | | A’1=0 | 0 | 0 | 0 | 0 | 1 | | A’0=0 | 0 | 0 | 0 | 0 | 0 |

| |

| 思考或体会 |

- 逻辑电路的原理容易掌握,画图过程中容易出现混乱。

- 线路过多且错综复杂,影响电路图的美观。

- 字发生器使用过程中出现错误。

| |

| 备注 | | |

| 实验项目 | 实验五 译码器及其应用 | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 掌握译码器的逻辑功能、级联扩展方法及实现逻辑函数的方法。 |

| 实验内容或结果 |

- 验证3-8译码器74138的逻辑功能,给出接线电路图,并按表5.1输入译码信号,将各输出端测试结果填入表5.1中。

表5.1 3-8译码器74138逻辑功能表

| 输 入 | 输 出 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

| | 0 | X | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | | 1 | 1 | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | | 1 | X | 1 | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

- 用2片74138级联扩展实现4线-16线译码器的逻辑功能,画出逻辑电路图,给出Multisim逻辑电路图,并验证其逻辑功能填入表5.2。设译编码输入信号为B3~B0,译码输出信号为

。

表5.2 4线-16线译码器逻辑功能表

| 输 入 | 输 出 | | B3 | B2 | B1 | B0 |

说明 |

|

| 实验内容或结果 |

| 0 | 0 | 0 | 0 | L’0输出0;其余输出1; | | 0 | 0 | 0 | 1 | L’1输出0;其余输出1; | | 0 | 0 | 1 | 0 | L’2输出0;其余输出1; | | 0 | 0 | 1 | 1 | L’3输出0;其余输出1; | | 0 | 1 | 0 | 0 | L’4输出0;其余输出1; | | 0 | 1 | 0 | 1 | L’5输出0;其余输出1; | | 0 | 1 | 1 | 0 | L’6输出0;其余输出1; | | 0 | 1 | 1 | 1 | L’7输出0;其余输出1; | | 1 | 0 | 0 | 0 | L’8输出0;其余输出1; | | 1 | 0 | 0 | 1 | L’9输出0;其余输出1; | | 1 | 0 | 1 | 0 | L’10输出0;其余输出1; | | 1 | 0 | 1 | 1 | L’11输出0;其余输出1; | | 1 | 1 | 0 | 0 | L’12输出0;其余输出1; | | 1 | 1 | 0 | 1 | L’13输出0;其余输出1; | | 1 | 1 | 1 | 0 | L’14输出0;其余输出1; | | 1 | 1 | 1 | 1 | L’15输出0;其余输出1; |

- 用74138译码器和适当的门电路实现逻辑函数

,给出逻辑电路图,并验证其逻辑功能填入表5.3。

表5.3 逻辑函数真值表

| 输 入 | 输出 | | A | B | C | F | | 0 | 0 | 0 | 1 | | 0 | 0 | 1 | 0 | | 0 | 1 | 0 | 1 | | 0 | 1 | 1 | 0 | | 1 | 0 | 0 | 1 | | 1 | 0 | 1 | 0 | | 1 | 1 | 0 | 0 | | 1 | 1 | 1 | 1 |

|

| 思考或体会 |

- 运行结束后,要及时关闭,以防影响其他电路运行。

- 实验器材的选定要准确。

- 知道芯片各个端口的作用。

|

| 备注 | |

| 实验项目 | 实验六 组合逻辑电路设计(二)与数据选择器 | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 实验目的 1.掌握数据选择器的逻辑功能及实现逻辑函数的方法 2.熟练掌握组合逻辑电路的设计方法 |

| 实验内容或结果 | 1. 验证4选1数据选择器74153的逻辑功能,给出接线电路图,并按表6.1输入数据和选择信号,将各输出端测试结果填入表6.1中。 表6.1 4选1数据选择器74153逻辑功能表

| 输 入 | 输出 | |

| A1 | A0 | D3 | D2 | D1 | D0 | Y | | 1 | X | X | X | X | X | X | 0 | | 0 | 0 | 0 | X | X | X | 0 | 0 | | 0 | 0 | 0 | X | X | X | 1 | 1 | | 0 | 0 | 1 | X | X | 0 | X | 0 | | 0 | 0 | 1 | X | X | 1 | X | 1 | | 0 | 1 | 0 | X | 0 | X | X | 0 | | 0 | 1 | 0 | X | 1 | X | X | 1 | | 0 | 1 | 1 | 0 | X | X | X | 0 | | 0 | 1 | 1 | 1 | X | X | X | 1 |

2. 用8选1数据选择器74151和适当的门电路实现逻辑函数

,给出逻辑电路图,并验证其逻辑功能填入表6.3。 表6.2 8选1数据选择器74151逻辑功能表

| 输 入 | 输 出 | |

| A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Y | W | | 1 | X | X | X | X | X | X | X | X | X | X | X | 0 | 1 | | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | 0 | 0 | 1 | | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | 1 | 1 | 0 | | 0 | 0 | 0 | 1 | X | X | X | X | X | X | 0 | X | 0 | 1 | | 0 | 0 | 0 | 1 | X | X | X | X | X | X | 1 | X | 1 | 0 | | 0 | 0 | 1 | 0 | X | X | X | X | X | 0 | X | X | 0 | 1 | | 0 | 0 | 1 | 0 | X | X | X | X | X | 1 | X | X | 1 | 0 | | 0 | 0 | 1 | 1 | X | X | X | X | 0 | X | X | X | 0 | 1 | | 0 | 0 | 1 | 1 | X | X | X | X | 1 | X | X | X | 1 | 0 | | 0 | 1 | 0 | 0 | X | X | X | 0 | X | X | X | X | 0 | 1 | | 0 | 1 | 0 | 0 | X | X | X | 1 | X | X | X | X | 1 | 0 | | 0 | 1 | 0 | 1 | X | X | 0 | X | X | X | X | X | 0 | 1 | | 0 | 1 | 0 | 1 | X | X | 1 | X | X | X | X | X | 1 | 0 | | 0 | 1 | 1 | 0 | X | 0 | X | X | X | X | X | X | 0 | 1 | | 0 | 1 | 1 | 0 | X | 1 | X | X | X | X | X | X | 1 | 0 | | 0 | 1 | 1 | 1 | 0 | X | X | X | X | X | X | X | 0 | 1 | | 0 | 1 | 1 | 1 | 1 | X | X | X | X | X | X | X | 1 | 0 |

表6.3 逻辑函数真值表

| 输 入 | 输出 | | A | B | C | F | | 0 | 0 | 0 | 1 | | 0 | 0 | 1 | 0 | | 0 | 1 | 0 | 1 | | 0 | 1 | 1 | 0 | | 1 | 0 | 0 | 1 | | 1 | 0 | 1 | 0 | | 1 | 1 | 0 | 0 | | 1 | 1 | 1 | 1 |

3.血型匹配电路设计:人的血型有A、B、AB、O四种,输血时必须满足图6.1中用箭头指示的授受关系。要求用8选1数据选择器74151和适当的门电路来实现。给出设计步骤,画出逻辑图,并在Multisim下验证其逻辑功能。

图6.1输血授受匹配关系 |

| 实验内容或结果 | 设计步骤

- 逻辑抽象,列出真值表

真值表如下:

| M | N | P | Q | Z | | 0 | 0 | 0 | 0 | 1 | | 0 | 1 | 0 | 1 | 1 | | 0 | 1 | 1 | 1 | 0 | | 1 | 0 | 0 | 0 | 0 | | 1 | 0 | 1 | 1 | 0 | | 1 | 1 | 0 | 1 | 1 | | 1 | 1 | 1 | 1 | 1 |

2.根据真值表写出逻辑表达式 Z=M'N'P'Q'+M'N'PQ'+M'NP'Q +M'NPQ'+MN'PQ'+MNP'Q' +MNP'Q+MNPQ'+MNPQ 取D0=D1=D3=D5=Q', 取D6=D7=Q+Q'=1 , 取D2=Q 取D4=0 3.画出电路图:

|

| 思考或体会 |

- 掌握基本的数据选择器的功能,和逻辑函数的实现。

- 设计电路的过程中要遵守电路设计的方法。

- 要从实际问题中分析出逻辑表达式。

|

| 备注 | |

| 实验项目 | 实验七 触发器 | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 1.熟练掌握基本SR锁存器的逻辑功能与电路构成。 2.掌握触发器的电路结构与工作原理及状态转换时序关系。 3.掌握不同逻辑功能触发器之间的相互转换。 |

| 实验内容或结果 |

- 用或非门构成基本SR锁存器,给出电路图,并用Multisim仿真验证其逻辑功能填入表7.1中。

表7.1 用或非门构成的基本SR锁存器功能表

| S | R |

|

| (

)' | 功能(锁存器状态) | | 0 | 0 | 0 | 0 | 1 | 保持 | | 0 | 0 | 1 | 1 | 0 | 保持 | | 0 | 1 | 0 | 0 | 1 | 置0 | | 0 | 1 | 1 | 0 | 1 | 置0 | | 1 | 0 | 0 | 1 | 0 | 置1 | | 1 | 0 | 1 | 1 | 0 | 置1 | | 1 | 1 | 0 | 0 | 1 | 状态不定 | | 1 | 1 | 1 | 0 | 1 | 状态不定 |

- 用与非门构成基本SR锁存器,给出电路图,并用Multisim仿真验证其逻辑功能填入表7.2中。

表7.2 用与非门构成的基本SR锁存器功能表

|

|

|

|

| (

)' | 功能(锁存器状态) | | 1 | 1 | 0 | 0 | 1 | 保持 | | 1 | 1 | 1 | 1 | 0 | 保持 | | 0 | 1 | 0 | 1 | 0 | 置1 | | 0 | 1 | 1 | 1 | 0 | 置1 | | 1 | 0 | 0 | 0 | 1 | 置0 | | 1 | 0 | 1 | 0 | 1 | 置0 | | 0 | 0 | 0 | 1 | 0 | 状态不定 | | 0 | 0 | 1 | 1 | 0 | 状态不定 |

- 验证D触发器74LS74的逻辑功能填入表7.3

表7.3 D触发器74HC74的功能

| 输 入 | 现态 | 次态 | 功能说明 | |

|

| CLK | D |

|

| | 0 | 1 | × | × | 0 | 1 | 置位 | | 0 | 1 | × | × | 1 | 1 | 置位 | | 1 | 0 | × | × | 0 | 0 | 复位 | | 1 | 0 | × | × | 1 | 0 | 复位 | | 1 | 1 | ↑ | 0 | 0 | 0 | 正常工作输出与D端相同 | | 1 | 1 | ↑ | 0 | 1 | 0 | 正常工作输出与D端相同 | | 1 | 1 | ↑ | 1 | 0 | 1 | 正常工作输出与D端相同 | | 1 | 1 | ↑ | 1 | 1 | 1 | 正常工作输出与D端相同 |

- 用D触发器加适当的门电路实现JK触发器的逻辑功能,写出激励信号逻辑表达式,给出逻辑电路图,并用Multisim仿真验证其逻辑功能填入表7.4中

D=JQ’+K’Q;

表7.4 用D触发器实现的JK触发器的逻辑功能

| 输入 | 现态 | 次态 | | J | K | CLK |

|

| | 0 | 0 | ↑ | 0 | 0 | | 0 | 0 | ↑ | 1 | 0 | | 0 | 1 | ↑ | 0 | 0 | | 0 | 1 | ↑ | 1 | 0 | | 1 | 0 | ↑ | 0 | 1 | | 1 | 0 | ↑ | 1 | 1 | | 1 | 1 | ↑ | 0 | 1 | | 1 | 1 | ↑ | 1 | 0 |

- 用下降沿JK触发器加适当的门电路实现D触发器的逻辑功能,写出激励信号逻辑表达式,给出电路图,并用Multisim仿真验证其逻辑功能填入表7.5中

J=D;K=D’;

表7.5 用JK触发器实现的D触发器的逻辑功能

| 输入 | 现态 | 次态 | | D | CLK |

|

| | 0 | ↓ | 0 | 0 | | 0 | ↓ | 1 | 0 | | 1 | ↓ | 0 | 1 | | 1 | ↓ | 1 | 1 |

6.用4个下降沿JK触发器构成4位异步二进制计数器,给出电路图,并用Multisim 仿真验证其逻辑功能填入表7.6中 |

| 实验内容或结果 |

表7.6 由4个下降沿JK触发器构成的4位异步二进制计数器

| 输入 | 现态 | 次态 | | CLK |

|

| | ↓ | 0000 | 0001 | | ↓ | 0001 | 0010 | | ↓ | 0010 | 0011 | | ↓ | 0011 | 0100 | | ↓ | 0100 | 0101 | | ↓ | 0101 | 0110 | | ↓ | 0110 | 0111 | | ↓ | 0111 | 1000 | | ↓ | 1000 | 1001 | | ↓ | 1001 | 1010 | | ↓ | 1010 | 1011 | | ↓ | 1011 | 1100 | | ↓ | 1100 | 1101 | | ↓ | 1101 | 1110 | | ↓ | 1110 | 1111 | | ↓ | 1111 | 0000 |

|

| 思考或体会 |

- 电路连接应看准不同节点,防止出现错误。

- 实验过程中注意CLK时钟信号的到达。

- 了解不同端口的作用和功能。

|

| 备注 | |

指导教师签名:

| 实验项目 | 实验八 逻辑电路综合设计(一) | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 1.熟练掌握触发器的应用 2.学会组合逻辑电路和时序逻辑电路的综合设计应用 |

| 实验内容或结果 | 1. 设计一个简易4人知识竞赛抢答电路,要求是:裁判掌握一个按钮,作用是给电路复位和发出抢答开始命令;4名竞赛者各掌握一个按钮,每人对应一个指示灯,在主持人发出开始抢答命令后,哪位参赛者先按钮其对应的指示灯亮。.

|

| 实验内容或结果 |

- 设计一个8人知识竞赛抢答电路,要求是:裁判掌握一个按钮,作用是给电路复位和发出抢答开始命令;8名竞赛者各掌握一个按钮,在主持人发出开始抢答命令后,哪位参赛者先按钮就在7段数码管上显示抢答者的编号。

|

| 思考或体会 |

- 从实际问题出发,抽象出其中的电路要求。

- 学会将问题与所学知识相联系。

- 正确使用各种元器件,了解各个部分的功能。

- 验证设计电路的正确性。

|

| 备注 | |

指导教师签名:

| 实验项目 | 实验九 计数器及其应用 | 日期 | |

| 实验环境 | Multisim | 成绩评定 | |

| 实验目的和要求 | 掌握集成同步二进制计数器的逻辑功能及实现其他进制的方法。 |

| 实验内容或结果 |

- 用Multisim仿真验证4位同步二进制计数器74161的逻辑功能,并填入表9-1中。

表9-1 4位同步二进制计数器74161的逻辑功能表

| 输 入 | 输 出 | | 清零 | 预置 | 使能 | 时钟 | 预置数据输入 | 计数输出 | 进位 | | R'D | LD' | EP | ET | CLK | D3 | D2 | D1 | D0 | Q3 | Q2 | Q1 | Q0 | TC | | 0 | x | x | x | x | x | x | x | x | 0 | 0 | 0 | 0 | 0 | | 1 | 0 | x | 0 | ↑ | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | | 1 | 0 | x | 1 | ↑ | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | | 1 | 0 | x | x | ↑ | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | | 1 | 1 | 0 | 0 | x | x | x | x | x | 保持 | 0 | | 1 | 1 | 0 | 1 | x | x | x | x | x | 保持 | * | | 1 | 1 | 1 | 0 | x | x | x | x | x | 保持 | 0 | | 1 | 1 | 1 | 1 | ↑ | x | x | x | x | 计数 | * |

- 用2片74161构成8位(模28)同步二进制计数器,给出电路接线图,并用Multisim仿真验证其逻辑功能。

- 分别采用反馈清零法和反馈置数法用74161和适当的逻辑门电路构成10进制同步计数器,给出电路接线图,并用Multisim仿真验证其逻辑功能。

反馈清零法

反馈置数法

- 用2片74161和适当的逻辑门电路构成129进制(模129)同步计数器,给出电路接线图,并用Multisim仿真验证其逻辑功能。

反馈清零法

反馈置数法 |

| 实验内容或结果 |

- 用2片同步十进制计数器74160和适当的逻辑门电路构成60进制计数器,给出电路接线图,并用Multisim仿真验证其逻辑功能。

反馈清零法

反馈置数法

|

| 思考或体会 |

- 注意各元器件的功能和各个端口的功能。

- 掌握同步二进制计数器的逻辑功能。

|

| 备注 | |

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?