既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

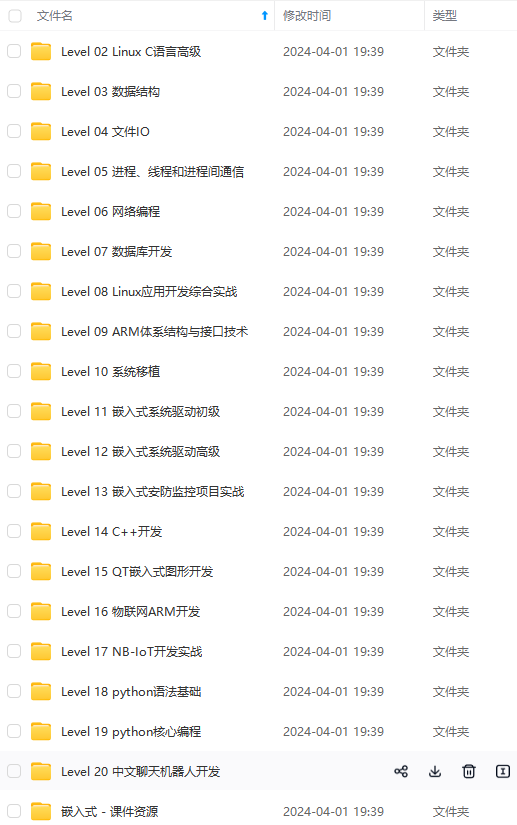

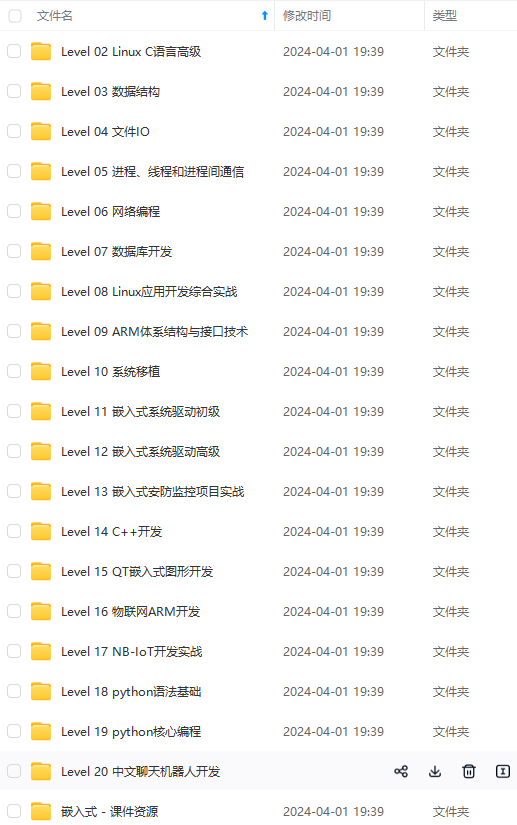

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

可以输出0%~100%占空比的PWM信号

使用固定TOP 值时最好使用ICR1 寄存器定义TOP。这样OCR1A 就可以用于在OC1A输出PWM 波。

但是,如果PWM 基频不断变化(通过改变TOP值), OCR1A的双缓冲特性使其更适合于这个应用。

计算公式:fPWM=fclk_IO/(2*N*TOP)

T/C 的时钟源

T/C 的时钟源可以有多种选择,由CS12:0控制,分别用于高速(低分频)/长时间(高分频)/外部计数场合

一个16位定时器,在8MHz系统时钟驱动下,可以实现uS级的高速定时和长达8秒的超长定时,这可是标准

51

的弱点

CS12 CS11 CS10 说明

0 0 0 无时钟源 (T/C 停止)

0 0 1 clkIO/1 ( 无预分频)

0 1 0 clkIO/8 ( 来自预分频器)

0 1 1 clkIO/64 ( 来自预分频器)

1 0 0 clkIO/256 ( 来自预分频器)

1 0 1 clkIO/1024 ( 来自预分频器)

1 1 0 外部T1 引脚,下降沿驱动

1 1 1 外部T1 引脚,上升沿驱动

分频器复位

在高预分频应用时, 通过复位预分频器来同步T/C 与程序运行,可以减少误差。

但是必须注意另一个T/C是否也在使用这一预分频器,因为预分频器复位将会影响所有与其连接的T/C。

外部时钟源

由于使用了引脚同步逻辑,建议外部时钟的最高频率不要大于fclk_IO/2.5。

外部时钟源不送入预分频器

选择使用外部时钟源后,即使T1引脚被定义为输出,其T1引脚上的逻辑信号电平变化仍然会驱动T/C1 计数,这个特性允许用户通过软件来控制计数。

输入捕捉单元

T/C 的输入捕捉单元可用来捕获外部事件,并为其赋予时间标记以说明此时间的发生时刻。

外部事件发生的触发信号由引脚ICP1 输入,也可通过模拟比较器单元来实现。

时间标记可用来计算频率、占空比及信号的其它特征,以及为事件创建日志。

输入捕捉单元可以工作在多种工作模式下

(使用ICR1定义TOP的(WGM1=12,14,10,8)波形产生模式时,ICP1与输入捕捉功能脱开,从而输入捕捉功能被禁用。)

在任何输入捕捉工作模式下都不推荐在操作过程中改变TOP值

当引脚ICP1 上的逻辑电平( 事件) 发生了变化,或模拟比较器输出ACO 电平发生了变化,并且这个电平变化为边沿检测器所证实,输入捕捉即被激发:

16位的TCNT1 数据被拷贝到输入捕捉寄存器ICR1,同时输入捕捉标志位ICF1 置位。

如果此时ICIE1 = 1,输入捕捉标志将产生输入捕捉中断。

中断执行时ICF1 自动清零,或者也可通过软件在其对应的I/O 位置写入逻辑"1” 清零。

注意,改变触发源有可能造成一次输入捕捉。因此在改变触发源后必须对输入捕捉标志执行一次清零操作以避免出现错误的结果

除去使用ICR1定义TOP的波形产生模式外, T/C中的噪声抑制器与边沿检测器总是使能的。

(其实就是永远使能??)

使能噪声抑制器后,在边沿检测器前会加入额外的逻辑电路并引入4个系统时钟周期的延迟.

噪声抑制器使用的是系统时钟,因而不受预分频器的影响

使用输入捕捉中断时,中断程序应尽可能早的读取ICR1 寄存器

如果处理器在下一次事件出现之前没有读取ICR1 的数据, ICR1 就会被新值覆盖,从而无法得到正确的捕捉结果。

测量外部信号的占空比时要求每次捕捉后都要改变触发沿。

因此读取ICR1 后必须尽快改变敏感的信号边沿。改变边沿后,ICF1 必须由软件清零( 在对应的I/O 位置写"1”)。

若仅需测量频率,且使用了中断发生,则不需对ICF1 进行软件清零。

输出比较单元

16位比较器持续比较TCNT1与OCR1x的内容,一旦发现它们相等,比较器立即产生一个匹配信号。

然后OCF1x 在下一个定时器时钟置位。

如果此时OCIE1x = 1, OCF1x 置位将引发输出比较中断。

(就是说输出比较可以工作在所有工作模式下,但PWM模式下更好用,功能更强)

输出比较单元A(OCR1A) 的一个特质是定义T/C 的TOP 值( 即计数器的分辨率)。

TOP 值还用来定义通过波形发生器产生的波形的周期。

由于在任意模式下写TCNT1 都将在下一个定时器时钟周期里阻止比较匹配,在使用输出比较时改变TCNT1就会有风险,不管T/C是否在运行

这个特性可以用来将OCR1x初始化为与TCNT1 相同的数值而不触发中断。

强制输出比较(FOC)

工作于非PWM 模式时,可以通过对强制输出比较位FOC1x 写”1” 的方式来产生比较匹配。

强制比较匹配不会置位 OCF1x 标志,也不会重载/ 清零定时器,

但是OC1x 引脚将被更新,好象真的发生了比较匹配一样(COMx1:0 决定OC1x 是置位、清零,还是交替变化)。

比较匹配输出单元

比较匹配模式控制位COM1x1:0 具有双重功能。

1 波形发生器利用COM1x1:0 来确定下一次比较匹配发生时的输出比较OC1x 状态;

2 COM1x1:0 还控制OC1x 引脚输出的来源。

只要COM1x1:0 不全为零,波形发生器的输出比较功能就会重载OC1x 的通用I/O 口功能。

但是OC1x 引脚的方向仍旧受控于数据方向寄存器 (DDR)。

从OC1x 引脚输出有效信号之前必须通过数据方向寄存器的DDR_OC1x 将此引脚设置为输出。

波形发生器利用COM1x1:0 的方法在普通模式、CTC 模式和PWM 模式下有所区别。

对于所有的模式,设置COM1x1:0=0 表明比较匹配发生时波形发生器不会操作OC1x寄存器

访问16位寄存器

写16 位寄存器时,应先写入该寄存器的高位字节.

usigned int k;

k=0x1234;

TCNT1H=(unsigned char)(k>>8);

TCNT1L=(unsigned char) k;

而读16 位寄存器时应先读取该寄存器的低位字节.

usigned int k;

k=TCNT1L;

k+=(unsigned int)(TCNT1H<<8);

使用“C” 语言时,编译器会自动处理16位操作.

usigned int k;

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

链图片转存中…(img-uvdS4wdX-1715844847624)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

4573

4573

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?