收集整理了一份《2024年最新物联网嵌入式全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升的朋友。

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

(VTREF)——接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)

可选择的引脚:

Test Reset Input (TRST) 这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。

Return Test Clock ( RTCK) 可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。

ystem Reset ( nSRST) 可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。

USER IN

用户自定义输入。可以接到一个IO上,用来接受上位机的控制。

USER OUT

用户自定义输出。可以接到一个IO上,用来向上位机的反馈一个状态

由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线,偶数针脚都是地信号。对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

二、20、14、10pin JTAG的引脚名称与序号对应关系

值得注意的是,不同的IC公司会自己定义自家产品专属的Jtag头,来下载或调试程序。目前JTAG接口的连接有三种标准,20、14、10pin JTAG的信号分别排列如下:

需要说明的是,上述Jtag头的管脚名称是对IC而言的。例如TDI脚,表示该脚应该与IC上的TDI脚相连,而不是表示数据从该脚进入download cable。

实际上10针的只需要接4根线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接。

三.让我们看看JTAG的最初用途,边界测试/边界扫描。

边界扫描技术的基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片和外围的输入输出隔离开来。通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。

对于芯片的输入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该管脚中去;

对于芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”该管脚上的输出信号。在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一个便捷的方式用以观测和控制所需要调试的芯片。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。一般的芯片都会提供几条独立的边界扫描链,用来实现完整的测试功能。边界扫描链可以串行的输入和输出,通过相应的时钟信号和控制信号,就可以方便的观察和控制处在调试状态下的芯片。

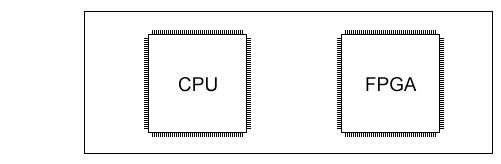

这是一个简单的电子板(也称为“印刷电路板”的“ PCB”),带有两个IC(“集成电路”),一个CPU和一个FPGA。典型的电路板可能具有更多的IC。

IC可以有很多引脚。因此,当然,IC通过大量连接(PCB traces)连接在一起。这里只显示四个。但是可以轻松地在PCB上放置几千个。

现在,如果您构建一千个板,每个板具有数千个连接,则不可避免地会有一些不良板。如何测试所有这些板?必须确保所有这些连接都正确。不能只手动测试所有这些连接。这样就创建了JTAG。

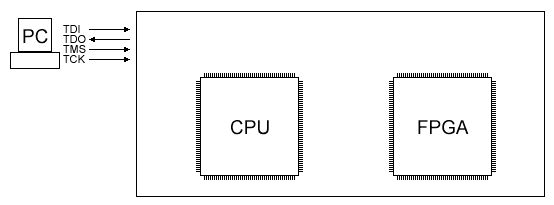

TAG可以控制所有IC的引脚。在图片上,也许JTAG将使所有CPU引脚输出,以及所有FPGA引脚输入。然后,通过从CPU引脚发送一些数据,并从FPGA引脚读取值,JTAG可以确保电路板连接良好。

现在,JTAG实际上包含四个逻辑信号,分别为TDI,TDO,TMS和TCK。从PC的角度来看,这是三个输出和一个输入。

这四个信号需要以特定方式进行布线。首先,TMS和TCK与所有JTAG IC并联。

然后将TDI和TDO并连接起来,形成一条链。用JTAG术语,您经常会听到“ JTAG-chain”一词的来历。

如您所见,每个符合JTAG的IC都有四个用于JTAG的引脚(三个输入和一个输出)。名为TRST的第五个引脚是可选的(JTAG复位)。JTAG引脚通常是专用的(不共享用于其他目的)。

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

目、大纲路线、电子书籍、讲解视频,并且后续会持续更新**

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?