- 锁相环的定义与作用

锁相环 (phase locked loop)是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。根据自动控制原理,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和锁相环 IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与锁相环 IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则锁相环 IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁相的目的。能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

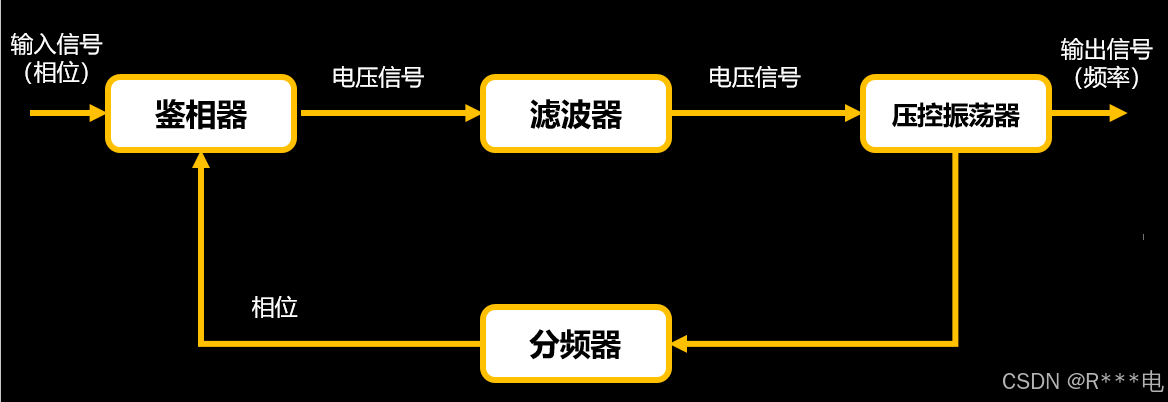

锁相环通常由鉴相器(PD,Phase Detector)、滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)3部分组成前向通路,由分频器组成频率相位的反馈通路,如图所示。

锁相环的工作原理是检测输入信号和输出信号的相位差,并将检测出的相位差信号通过鉴相器转换成电压信号输出,经低通滤波器滤波后形成压控振荡器的控制电压,对振荡器输出信号的频率实施控制,再通过反馈通路把振荡器输出信号的频率、相位反馈到鉴相器。

锁相环在工作过程中,当输出信号的频率成比例地反映输入信号的频率时,输出电压与输入电压保持固定的相位差值,这样输出电压与输入电压的相位就被锁住了。

上图所展示的是一阶的锁相环结构框图,而一阶锁相环具有以下特点

结构简单:包含基本组件,因此设计和实现都非常直观。

动态性能有限:由于没有积分或导数成分,一阶锁相环在处理快速变化的相位误差时可能表现不佳。

稳定性容易保证:由于第一阶系统较为简单,通常容易稳定,但其响应速度和稳态精度有限。

二阶锁相环在一阶的基础上加入了积分器,使其能够更好地处理快速变化的相位误差。另外,积分器消除了系统的稳态误差,使得二阶锁相环在锁相时具有较高的精度。但是由于增加了额外的滤波和控制元素,设计和实现会更加复杂,需要对系统参数进行合理调节以确保稳定性。

因此总结下来,一阶与二阶锁相环有以下几点区别:

控制组件复杂性:一阶锁相环简单,二阶锁相环则引入了更多控制措施,如积分器。

动态响应:二阶锁相环的动态响应通常优于一阶锁相环,能更快锁定且有更小的相位误差。

稳态误差:二阶锁相环能够有效消除稳态误差,而一阶锁相环可能仍存在残余误差。

应用场景:一阶锁相环适合简单应用,二阶锁相环适用于需要更高精度和更快响应时间的复杂场景。

- 锁相环在眼图恢复的应用

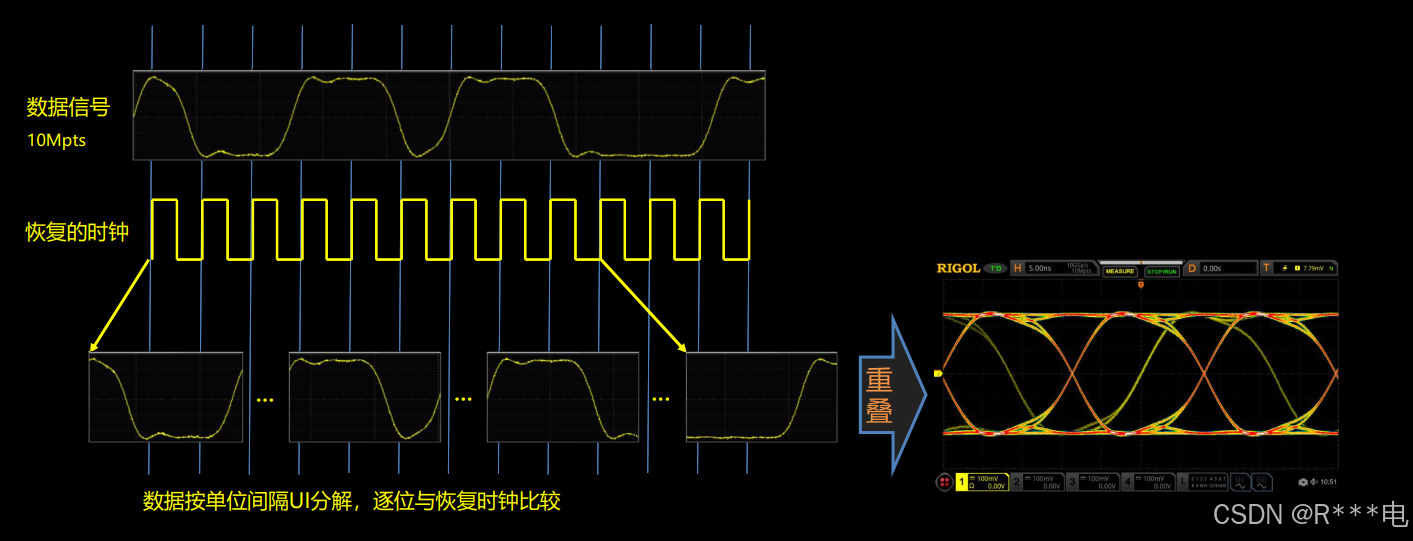

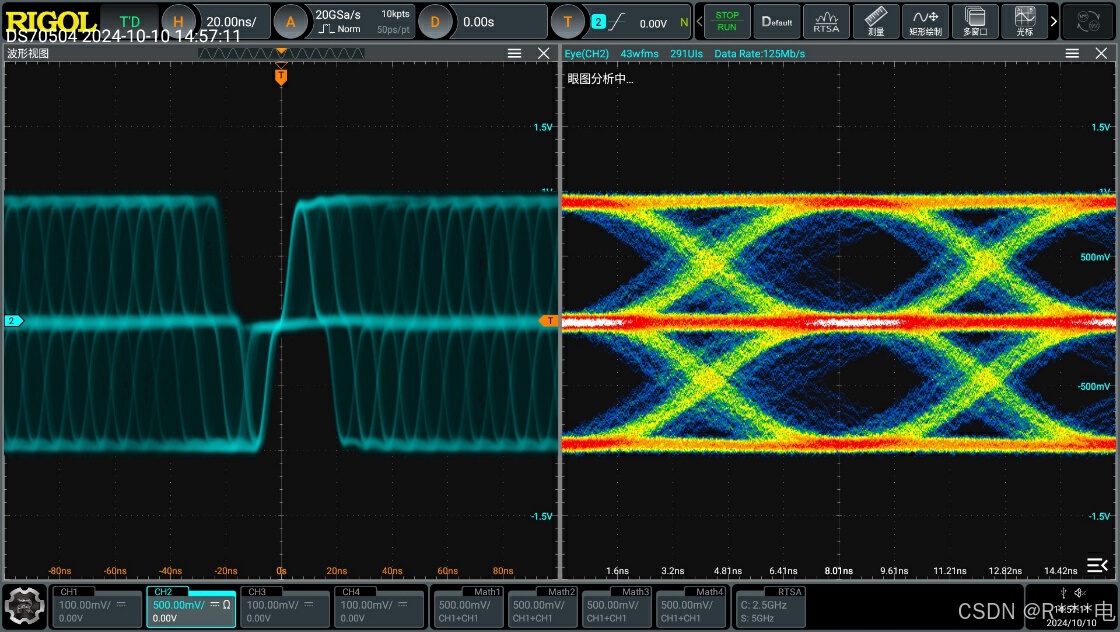

锁相环在高速串行信号中有着广泛的应用。在接收到的数字数据流中,没有明确的时钟信号。而在许多通信协议中,例如以太网、USB和光纤通信等,时钟信息是嵌入在数据流中的。PLL则用于从这些数据流中提取出稳定的时钟信号。通过比较传输过来的数据边缘与自身产生的时钟信号边缘,PLL调整其内部压控振荡器(VCO)的频率和相位,使得本地生成的时钟信号与输入信号同步。

在眼图的测量中,时钟恢复是决定眼图质量的一个关键因素。

常见眼图的时钟恢复方式一般分为常数时钟和锁相环两种,两种方式各有其优缺点。

常数时钟电路设计相对简单,特别适合一些低速、低成本的应用场景。此外,常数时钟不会受到输入信号抖动或频率漂移的影响,从而提供稳定的基准时钟信号。而且在环境、电源等外部条件变化较大的情况下,常数时钟仍然可以保持一致的时钟频率。常数时钟无需锁定过程,因此系统能够迅速启动并开始工作,这对于需要快速响应的系统非常重要。

但是常数时钟也有不适应频率偏差、抗抖动性能差、灵活性不足等缺点。如果输入信号的频率发生变化(例如由于发送方和接收方之间的时钟偏移),常数时钟可能无法提供精确的采样时间,导致误码率增高。这种问题在高速数据传输中尤为显著,因为频率偏离会导致更严重的采样错误。因此常数时钟常用于低速、低成本应用,或是已知固定频率的系统。

锁相环通过不断调整时钟相位,可以动态补偿由于噪声或其他干扰引起的抖动。这样可以在一定程度上平滑信号沿的不规则性,提高数据的完整性。在长时间或远距离传输中,信号可能会有小幅度的频率漂移。PLL能够跟踪并调整其输出信号频率以适应输入信号的微小变化,确保持续同步。但是相对于常数时钟的恢复,锁相环存在反馈调节的过程,响应时间相对较长。而且锁相环系统更加复杂,在使用过程中需要对带宽、阻尼系数等参数进行合适的设置。,否则可能导致眼图质量不能达到预期。

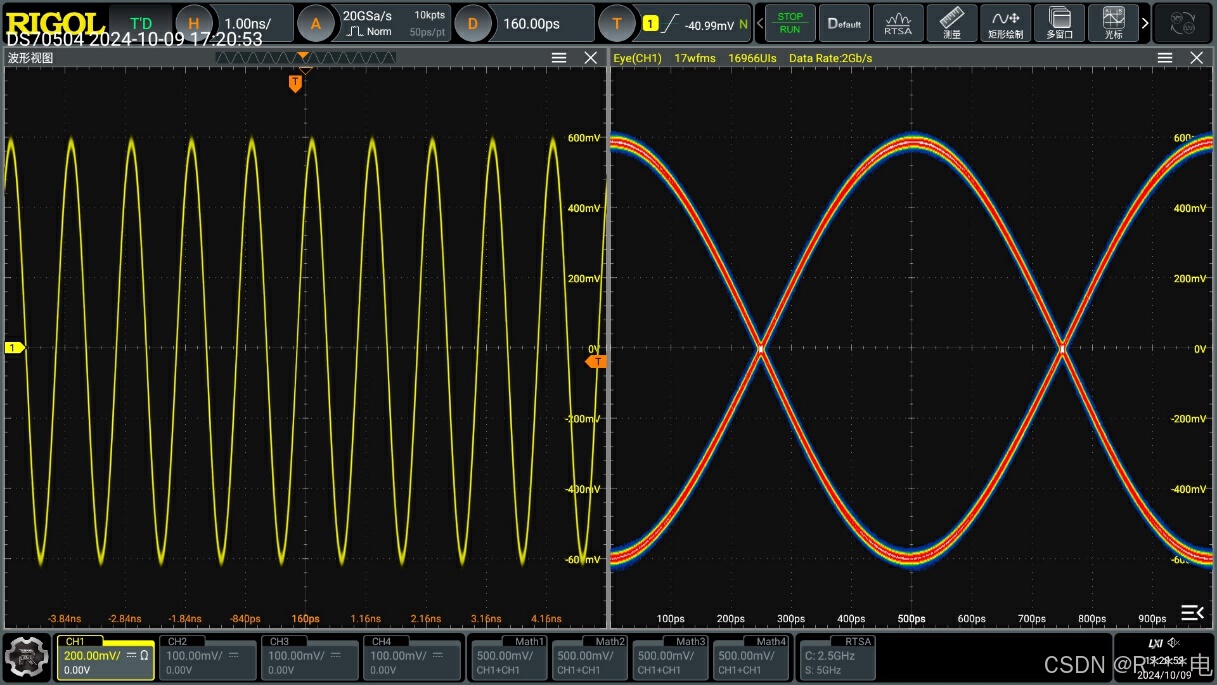

带宽50KHz,阻尼0.707

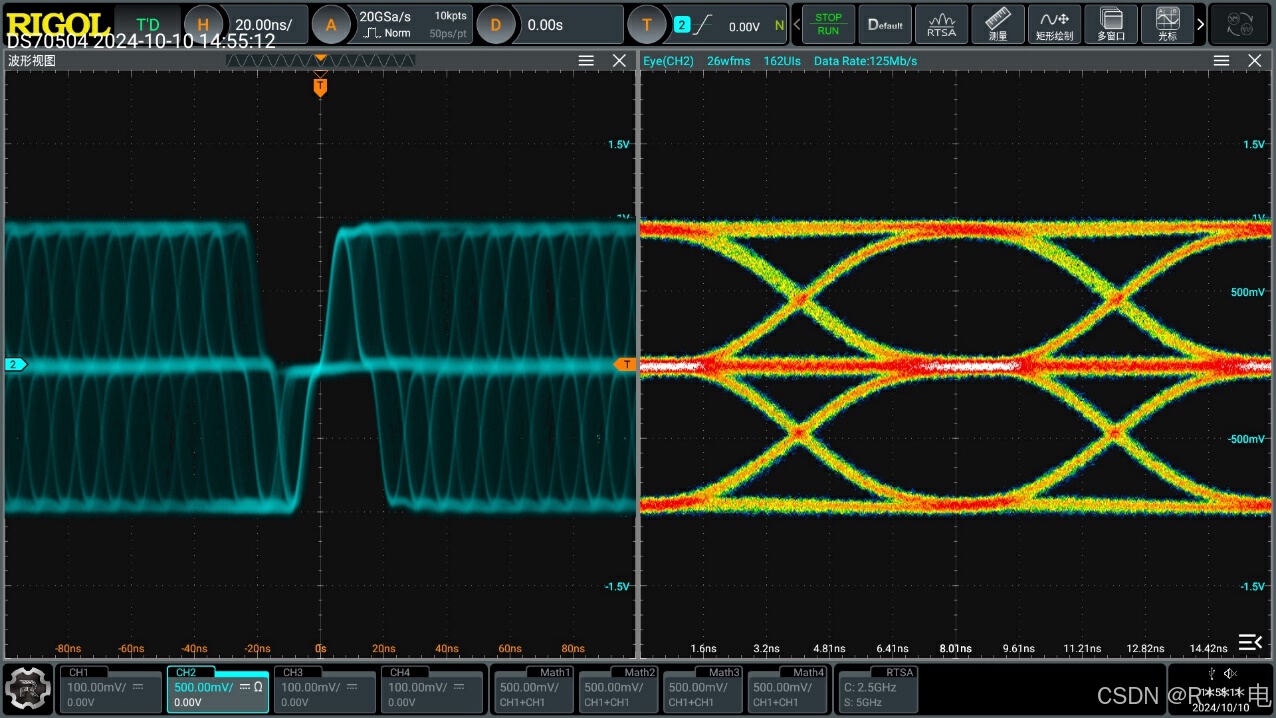

带宽1MHz,阻尼0.707

锁相环的带宽通常定义为它的闭环系统的带宽,即从输入相位到输出相位的传递函数的带宽.带宽的大小直接影响PLL对输入信号频率或相位变化的响应速度,也影响系统的噪声性能和稳定性。

带宽决定了PLL能否有效地抑制输入信号或自身产生的相位噪声。带宽较宽时PLL能跟随输入信号的快速变化,但对高频噪声也比较敏感;带宽较窄时,PLL对低频噪声具有较好的抑制效果,但响应速度较慢。带宽越宽,系统响应越快,但系统的稳定性可能会下降,可能会导致过冲或震荡现象,通常在设计中需要平衡响应速度与系统稳定性。

总结

锁相环是一种输出电压与输入电压保持固定的相位差值的负反馈电路,广泛应用于高速串行总线的时钟恢复中。锁相环带宽越宽,系统响应越快,但系统的稳定性可能会下降,可能会导致过冲或震荡现象,通常在设计中需要平衡响应速度与系统稳定性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?