前言

基于海思BS21系列芯片,核心处理器芯片是一款高集成2.4GHz SOC BLE&SLE芯片,支持BLE5.4/SLE1.0,集成RF电路,RF包含功率放大器PA、低噪声放大器、TX/RXSwitch、集成电源管理等模块,支持1M/2M/4M 3种带宽,最大支持12Mbit/s速率。具有体积小、功耗低传输距离远、传输速度快、抗干扰能力强、低延时等特点,最大射频发射功率为6dBm。

BS21芯片集成高性能32bit微处理器(MCU),硬件安全引擎以及丰富的外设接口,外设接口包含SPI、UART、2C、PMW、GPIO、USB2.0、NFCTa9、PDM、I2S/PCM、QDEC、KEYSCAN 键盘扫描电路,支持8路13bit分辨率ADC,ADC支持对接音频AMIC内置SRAM和合封Flash,并支持在Flash上运行程序。

可广泛应用于智能穿戴、家庭自动化、家庭安防、个人保健、智能家电、配饰与遥控器、汽车、照明、工业互联网、智能数据采集、智能控制等领域。

一,总体设计

主要规格

SLE:

- 支持无线帧类型 1 (GFSK帧)

- 支持最大4Mbps 空口速率

- 支持 定位功能

- 支持PTA共存

- BLE:

支持 BLE4.0/4.1/4.2/5.0/5.1/5.2/5.3规范

支持数据速率BLE 1Mbps,2Mbps,500kbps和125kbps口。

MCU:

支持RISC-V 32bit CPU,带浮点单元

支持最大主频 64MHz

支持1MB Flash 128KB RAM

支持 1024bit eFuse

支持增强安全特性AES128/SM4,TRNG

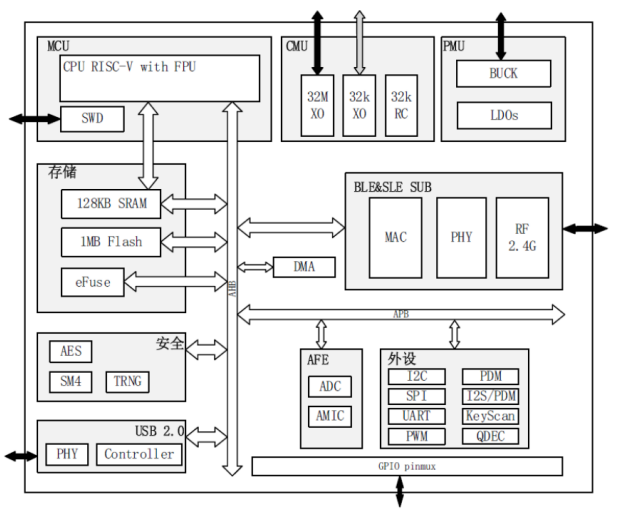

芯片功能图

BS21芯片集成了高性能32bit微处理器(MCU),拥有丰富的外设接口,外设接口包括SPI、UART、I2C、PWM、GPIO、USB2.0、NFC Tag、PDM、I2S/PCM,支持8路ADC、可以复用为音频AMIC,内置SRAM,支持在Flash上运行程序。

芯片功能图

硬件设计

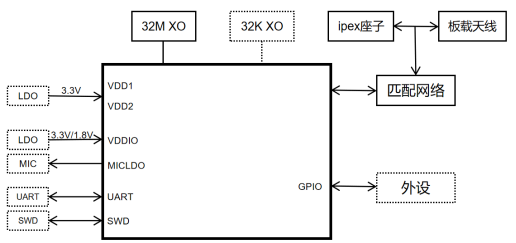

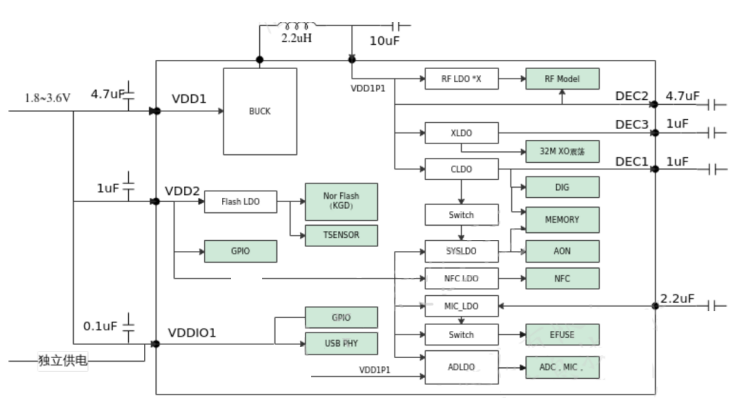

系统框图及原理图

框图

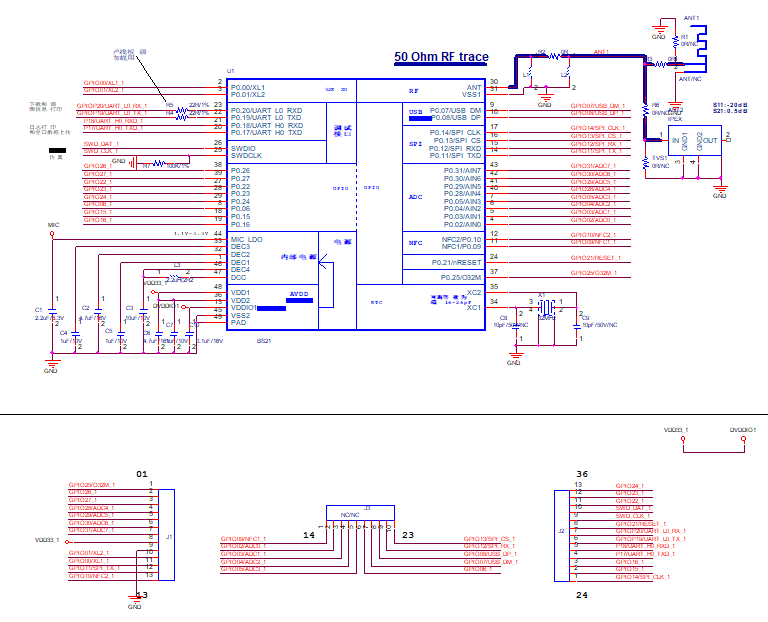

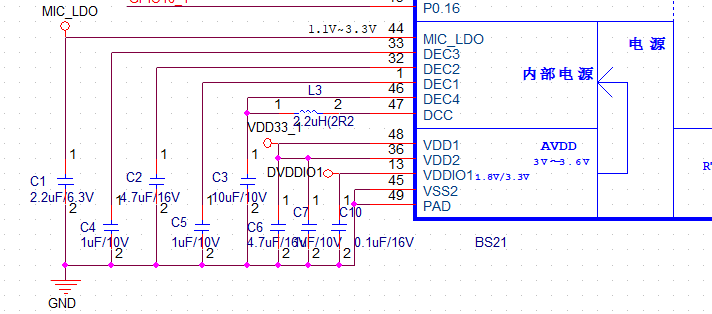

原理图

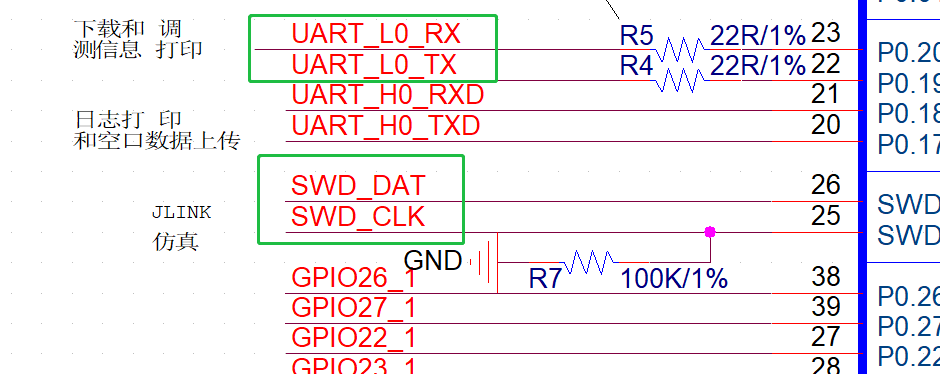

调试接口

芯片25、26脚SWD和22、23脚UART_L0作为平台调试接口,UART_L0用于空片下载、LOG打印和辅助调试。SWD脚信号用于仿真调试,芯片烧录。使用调试口时需注意调试口的电压域在13脚VDDIO作用逻辑电平参考。UART_L0有预留出测试点,做产线板级加载用。同时预留串接电阻用于电路保护。

调试接口

UART接口

2组 UART。默认状态下22、23脚为UART_L0用于空片下载和调测信息打印,为2线UART接口,速率为9600bps~4Mbps;模组的20、21脚为UART_H0用于BT日志打印和空口数据上传,速率为9600bps~4Mbps。

I2C接口

I2C接口任意IO可配,无特殊设计。I2C设计需外部增加上拉电阻。

PDM接口设计

PDM接口用于将DMIC通路的数据进行预处理,PDM接口支持外接DMIC进行音频采样,包含一个输出到DMIC的采样时钟CLK端口,一个接收DMIC采样信号的DIN端口,任意IO可配。输出采样时钟支持3.072MHz/1.536MHz/768kHz,支持左右声道切换,左右声道同时采样、单声道采样。可以使用44脚MIC_LDO输出为DMIC供电,供电范围在1.1V-3.3V之间可调。

I2S接口

提供1组I2S,支持Master模式和Slave模式,任意IO可配。

USB接口

芯片9、10脚为USB接口,支持USB Device 2.0 接口。USB DP/DM为通信管脚,模组内部没有预留出共模电感及ESD器件,主板应用时预留共模电感、ESD器件,以抑制长线、PC端可能带来的ESD破坏。在使用USB功能的时候VDDIO1的电压必须是3.3V。

USB接口

USB设计需控制差分阻抗如下:

| 序号 | 参数 |

PIN |

差分阻抗控制 |

| 1 | USB_DM |

9 |

90Ω±15% |

| 2 | USB_DP |

10 |

90Ω±15% |

电源设计

芯片支持BUCK和LDO两种电源模式。本设计采用BUCK工作模式供电,BUCK的DCC管脚输出采用2.2uH+10uF电容。

芯片电源拓扑结构

供电分为VDD和VDDIO,外部供电通过VDD(3.3V)管脚供电,模组内部芯片生成各模块电源,DEC1、DEC2、DEC3以及给麦克风供电的MIC_LDO等。VDDIO给内部GPIO做参考电压,同时用作USB的供电。

电源设计

射频电路

射频电路芯片端设计了一组π型电路,主要针对低频和谐波杂散。中间预留了用于生产测试的测试点,以及后级的两颗切换电阻,切换内置PCB天线和IPEX座子,座子和天线旁的器件主要用于天线匹配。

| 参数 |

芯片PIN |

|

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?