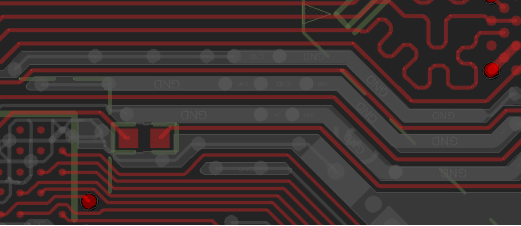

一,eMMC信号阻抗及走线

- CLK和STRB信号建议做包地处理,包地线每隔≦500mil打一个GND过孔。

- 整体布局时,eMMC尽量靠近SOC放置,尽量缩短走线。

- eMMC 所有信号的参考层需要为完整的地平面,避免出现连续的过孔阻断信号的回流路径的情况。

- CLK的22ohm串联匹配电阻靠近CPU端(源端),CPU管脚和电阻之间走线必须控制在300mil以内。

- STRB的0ohm串联匹配电阻靠近eMMC颗粒端,eMMC管脚和电阻之间走线必须控制在300mil以内。

- VDD管脚外接电容必须靠近对应的管脚放置,走线尽量短粗。

| 序号 | 走线参数 | 走线要求 |

| 1 | 走线阻抗 | 单端50ohm±10% |

| 2 | 时钟(CLK、STRB)与数据之间等长 | <120mil |

| 3 | 走线长度 | <3 inches |

| 4 | eMMC信号线之间间距 | 2倍eMMC线宽 |

| 5 | eMMC与其它信号间距 | 3倍线宽,至少2倍eMMC线宽 |

| 6 | 各信号所允许过孔数量 | 一般不超过2个 |

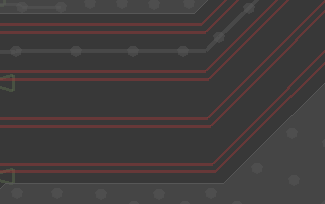

二,USB2.0接口电路走线

- 整体布局时,USB座尽量靠近SOC放置,尽量缩短走线。

- USB差分对尽可能参考层为完整的地平面且需全程包地处理,包地的走线间隔300mil以内必须有地过孔。

- 当USB差分信号走线需要换层时,确保走线上的过孔数量少于4个,不得超过6个,并靠近信号过孔放置对称的缝合地孔,缝合地孔和信号过孔中心距不得超过30mil。

| 序号 | 走线参数 | 走线要求 |

| 1 | 走线阻抗 | 差分90ohm ±10% |

| 2 | 差分对内等长 | <20mil |

| 3 | 走线长度 | <6 inches |

| 4 | 各信号所允许过孔数量 | 建议不超过4个,不得超过6个 |

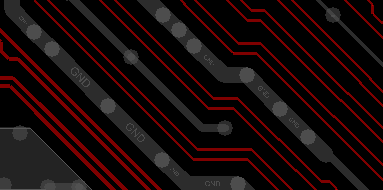

三,USB3.0接口电路走线

- 整体布局时,USB座尽量靠近SOC放置,尽量缩短走线。

- 电源的去耦电容务必靠近对应的电源管脚。

- SSTXP/N和SSRXP/N尽量走在TOP层,必须要换层时,不得超过2个过孔,并靠近信号过孔放置对称的缝合地孔,缝合地孔和信号过孔中心距不得超过30mil,走线拐角尽量用弧线或者钝角,不能为直角或锐角。

- STXP/N,SSRXP/N信号的参考层需要为完整的地平面,避免出现连续的过孔阻断信号的回流路径的情况。

- USB3.0接口信号整组做包地处理,包地线每隔≦300mil打一个GND过孔。USB3.0信号需要参考完整的GND平面。

| 序号 | 走线参数 | 走线要求 |

| 1 | 走线阻抗 | 差分90ohm ±10% |

| 2 | 差分对内等长要求 | <6mil |

| 3 | 走线长度 | Host设备<6 inches,Device和OTG设备<5 inches |

| 4 | 电容要求 | 100nF ±20%, 建议用0201封装 |

| 5 | 差分对,对间间距 | 大于等于4倍USB线宽 |

| 6 | USB与其它信号间距 | 大于等于4倍USB线宽 |

| 7 | 各信号所允许过孔数量 | 建议不超过2个 |

| 8 | ESD要求 | I/O对地电容不超过0.2pF |

四,MIPI CSI/DSI接口电路走线

- 整体布局时,USB座尽量靠近SOC放置,尽量缩短走线。

- 电源的去耦电容务必靠近对应的电源管脚。

- 尽量减少换层过孔,必须要换层时,不建议超过4个过孔,且靠近信号过孔放置对称的缝合地孔,缝合地孔和信号过孔中心距不得超过30mil。

- 建议MIPI信号整组做包地处理,包地线每隔≦500mil打一个GND过孔。MIPI信号需要参考完整的GND平面。

- MIPI CSI差分对的参考层需要为完整的地平面,避免出现连续的过孔阻断信号的回流路径的情况。

| 序号 | 走线参数 | 走线要求 |

| 1 | 走线阻抗 | 差分100ohm ±10% |

| 2 | 差分对内等长要求 | <12mil |

| 3 | 数据和时钟差分对之间的等长要求 | <36mil |

| 4 | 差分对对间间距 | 大于等于3倍线宽 |

| 5 | MIPI与其它信号间距 | 大于等于3倍线宽 |

| 6 | 各信号所允许过孔数量 | 建议不超过4个 |

| 7 | 走线长度 | <6inches |

五,LVDS TX接口电路走线

- 整体布局时,USB座尽量靠近SOC放置,尽量缩短走线。

- 电源的去耦电容务必靠近对应的电源管脚。

- LVDS差分对尽量减少换层过孔,必须要换层时,推荐少于4个过孔,不得超过6个,并靠近信号过孔放置对称的缝合地孔,缝合地孔和信号过孔中心距不得超过30mil。

- 建议LVDS信号整组做包地处理,包地线每隔≦600mil打一个GND过孔。LVDS信号需要参考完整的GND平面。

- LVDS差分对的参考层需要为完整的地平面,避免出现连续的过孔阻断信号的回流路径的情况。

| 序号 | 走线参数 | 走线要求 |

| 1 | 走线阻抗 | 差分100ohm ±10% |

| 2 | 差分对内等长要求 | <12mil |

| 3 | 数据和时钟差分对,对间等长要求 | <60mil |

| 4 | 走线长度 | <6 inches |

| 5 | 差分对间间距 | 大于等于3倍LVDS线宽 |

| 6 | LVDS与其它信号间距 | 大于等于3倍LVDS线宽 |

| 7 | 各信号所允许过孔数量 | 不超过4个 |

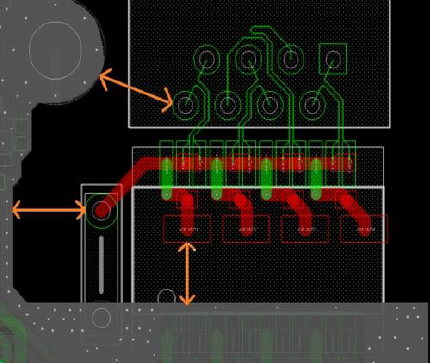

六,RGMII接口电路走线

- CLK信号建议做包地处理,包地线每隔≦500mil打一个GND过孔。

- 整体布局时,USB座尽量靠近SOC放置,尽量缩短走线。

- 电源的去耦电容务必靠近对应的电源管脚。

- ETH_CLK_25M的22ohm串联匹配电阻靠近CPU端(源端),CPU管脚和电阻之间走线必须控制在400mil以内。

- ETH_CLK_25M必须全程包地处理,包地的走线间隔300mil以内必须有地过孔。

- MII模式MCLKINOUT输入模式:22ohm串联匹配电阻靠近PHY端,PHY管脚和电阻之间走线必须控制在400mil以内。

- RGMII/RMII所有信号的参考层需要为完整的地平面,避免出现连续的过孔阻断信号的回流路径的情况

- 网络变压器尽可能靠近RJ45座子,MDI走线不得超过4.5inch。

- PHY到网络变压器的MDI差分信号差分阻抗为100Ω ±10%。

- PHY到网络变压器的差分信号MDI0+、MDI0-、MDI1+、MDI1-、MDI2+、MDI2-、MDI3+、MDI3-差分对内长度偏差控制在±5mil以内,MDI差分对应严格遵循差分规则走线。

- MDI差分对间线长延迟控制在800mil以内。

- MDI0/1/2/3之间空隙:≥3倍线宽。

- MDI0/1/2/3和其它信号之间空隙:≥4倍线宽。

- MDI尽量减少换层过孔,必须要换层时,最多只能打2次过孔,并靠近信号过孔放置对称的地缝合孔。

- 网络变压器高压侧的MDI差分对,走线线宽建议尽量走粗,建议8mil。

- 网络变压器中心抽头滤波电容必须靠近网络变压器对应的管脚。

- HY芯片电源的去耦电容,都需要尽量靠近PHY芯片各管脚放置,走线时尽量先经过电容焊盘,再到芯片管脚,管脚和电容之间走线长度不得超过100mil。

- 网络变压器高压侧的相关器件必须远离PCB板的主地。

- RJ45接口和网络变压器高压侧属于高压区,禁止覆铜,建议和低压区间隔至少4mm以上。

- 建议在网络变压器下方开1mm以上的爬电槽,加强抗浪涌能力。

| 序号 | 走线参数 | 走线要求 |

| 1 | 走线阻抗 | 单端50ohm ±10% |

| 2 | (TXD{0-3},TXEN) to TXCLK等长 | <120mil |

| 3 | (RXD{0-3},RXDV) to RXCLK等长 | <120mil |

| 4 | 走线长度 | <6 inches |

| 5 | RGMII信号线之间间距 | ≥2倍RGMII线宽 |

| 6 | RGMII与其它信号间距 | 3倍RGMII线宽,至少2倍倍RGMII线宽 |

| 7 | 各信号所允许过孔数量 | 建议不超过2个 |

七,WIFI/BT电路走线

- 整体布局时,WIFI模组适当放置,模组远离DDR、HDMI、USB、LCD电路以及喇叭等易干扰模块或连接座。

- 模组下方TOP层不允许走线,需保证参考面为完整的地平面,SDIO/PCIe/UART/PCM信号线建议绕过模组投影区域后连接到模组管脚。

- 晶体电路布局需要优先考虑,布局时应与芯片在同一层并尽量靠近放置以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量天线区域。

- 晶体以及时钟信号需要全程包地处理,包地线每隔100mil至少添加一个GND过孔,并且必须保证邻层的地参考面完整。

- 模组的电感布局时,请注意走线经电感出来后,先经过电容,再进入模组电源管脚。

6356

6356

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?