PS2实验

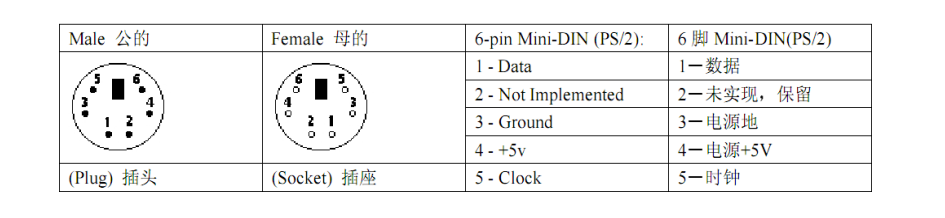

PS2接口示意图:

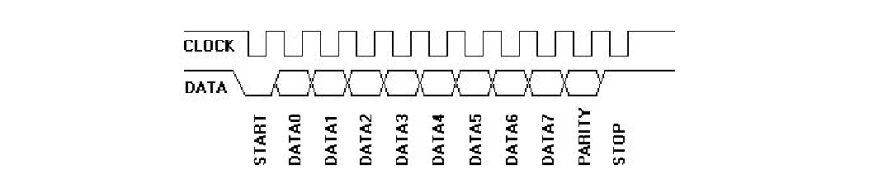

PS2时序图

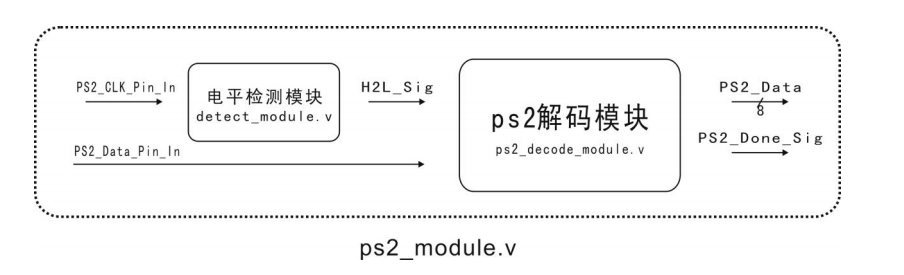

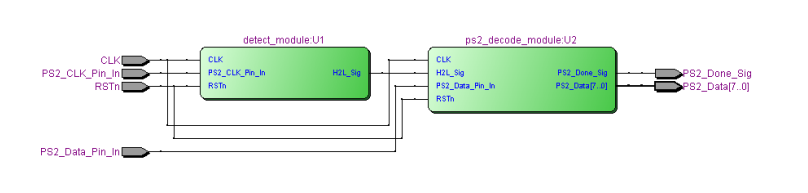

实验功能分解图

detect_module

PS2_CLK_Pin_In由高变低时触发

module detect_module

(

CLK, RSTn,

PS2_CLK_Pin_In,

H2L_Sig

);

input CLK;

input RSTn;

input PS2_CLK_Pin_In;

output H2L_Sig;

/**************************/

reg H2L_F1;

reg H2L_F2;

always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

begin

H2L_F1 <= 1'b1;

H2L_F2 <= 1'b1;

end

else

begin

H2L_F1 <= PS2_CLK_Pin_In;//低电平有效

H2L_F2 <= H2L_F1;

end

/****************************/

assign H2L_Sig = H2L_F2 & !H2L_F1;

/****************************/

endmodule

ps2_decode_module

按位读出按键信号

module ps2_decode_module

(

CLK, RSTn,

H2L_Sig, PS2_Data_Pin_In,

PS2_Data, PS2_Done_Sig

);

input CLK;

input RSTn;

input H2L_Sig;

input PS2_Data_Pin_In;

output [7:0]PS2_Data;

output PS2_Done_Sig;

/*******************************/

reg [7:0]rData;

reg [4:0]i;

reg isShift;

reg isDone;

always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

begin

rData <= 8'd0;

i <= 5'd0;

isDone <= 1'b0;

end

else

case( i )

5'd0:

if( H2L_Sig ) i <= i + 1'b1;

4'd1, 4'd2, 4'd3, 4'd4, 4'd5, 4'd6, 4'd7, 4'd8:

if( H2L_Sig ) begin i <= i + 1'b1; rData[ i-1 ] <= PS2_Data_Pin_In; end//先传输低位,在传高位 记录通码

5'd9, 5'd10:

if( H2L_Sig ) i <= i + 1'b1;

5'd11:

if( rData == 8'hf0 ) i <= 5'd12; //如果是0xf0则后8位为断码

else i <= 5'd23;

5'd12, 5'd13, 5'd14, 5'd15, 5'd16, 5'd17, 5'd18, 5'd19, 5'd20, 5'd21, 5'd22:

if( H2L_Sig ) i <= i + 1'b1;

5'd23:

begin i <= i + 1'b1; isDone <= 1'b1; end

5'd24:

begin i <= 5'd0; isDone <= 1'b0; end

endcase

/************************************/

assign PS2_Data = rData;

assign PS2_Done_Sig = isDone;

/*************************************/

endmodule

组合PS2模块

module ps2_module

(

CLK, RSTn,

PS2_CLK_Pin_In, PS2_Data_Pin_In,

PS2_Data, PS2_Done_Sig

);

input CLK;

input RSTn;

input PS2_CLK_Pin_In;

input PS2_Data_Pin_In;

output [7:0]PS2_Data;

output PS2_Done_Sig;

/********************************/

wire H2L_Sig;

detect_module U1

(

.CLK( CLK ),

.RSTn( RSTn ),

.PS2_CLK_Pin_In( PS2_CLK_Pin_In ), // input - from top

.H2L_Sig( H2L_Sig ) // output - to U2

);

/*********************************/

ps2_decode_module U2

(

.CLK( CLK ),

.RSTn( RSTn ),

.H2L_Sig( H2L_Sig ), // input - from U1

.PS2_Data_Pin_In( PS2_Data_Pin_In ), // input - from top

.PS2_Data( PS2_Data ), // output - to top

.PS2_Done_Sig( PS2_Done_Sig ) // output - to top

);

/**********************************/

endmodule

感谢VerilogHDL那些事儿_建模篇

264

264

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?