前言

最近真是忙忙的咧,数一数真是九门功课同步学,而且五门硬课(考前突击致挂率很高的那种)。再加上老前辈的肺腑之言——基础才是本科生该关注的。所以看完基础编程的《Unix网络编程》也将告一段落辣,待我打好基础再与你一战!

言归正传,接下来将讨论的Vertibi编码依然来自通信编码老师的课后作业。现在时间不早了咱就省掉前戏了。

原理

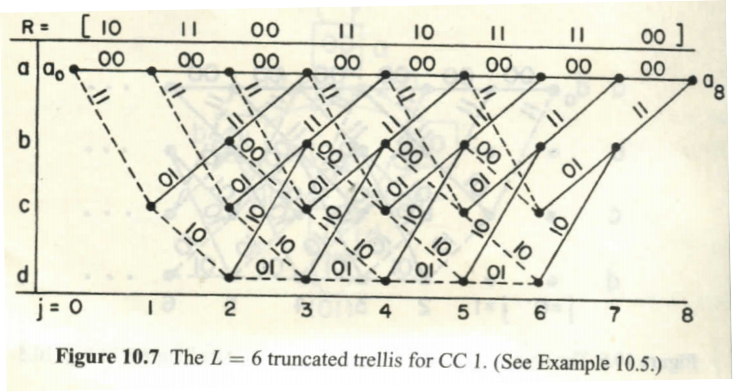

关于Vertibi算法的原理,网上相关的资料很多,况且来看这篇文章的同学对原理应该不陌生,在这里只是简单提提。我们以(2,1)卷积编码器为例,其核心可用下面几幅图表示

- 每个卷积编码器可用状态转移来表示,因此图中a,b,c,d代表编码器所处的4个状态,而j表示时刻,实线表示输入为1,虚线表示输入为0,而线上的数字表示输入对应的输入;打个比方,图中(a,0)点到(c,1)点的连接表示:当输入为0时,寄存器的状态从0时刻的a(我们设为两个寄存器的状态全为0,记为00)到1时刻的c(记为10),且伴随着输出为11

而Vertibi译码则是从上图中找出一条路,使这条路径对应的输出序列与输入序列的汉明距离最小(既“最像”)

面对这种问题,我们首先想到的便是树的深度遍历,既找出所有路径然后看看谁“最像”。然而。Vertibi就是靠这个成为南加州大学知名校友,创立高通公司,并且成功让系主任花半节课将他的生平,自然有其妙♂处。

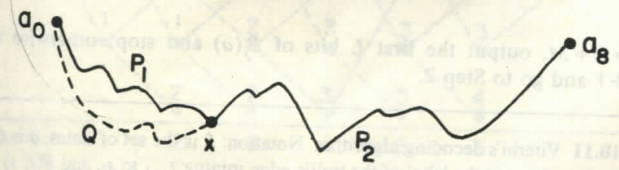

请看下图

它阐述了一个定理:如果P是最短路径,对于P上任意一点x,P1一定是最短路径。

这个定理可以很轻松的用反证法证明

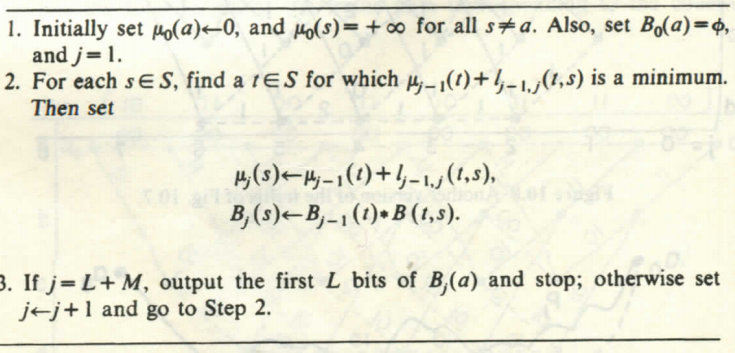

之后的东西好难用语言描述所以我们直接看伪代码吧

在这里做些解释

首先定义路径长度为两个状态转移时的输出序列与相应的输入序列的汉明距离

- u[j][s]代表J时刻到达s状态的累计路径长度

- l[t][s]代表从t状态转到l状态的的路径长度

- B[s]代表s状态的对应解码序列

由于最后路径会回到a状态(既寄存器为00状态),因此按照以上方法执行后,B(a)即为结果

C代码

int v

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7788

7788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?