自己动手画CPU: 自己动手画CPU实验框架 https://gitee.com/totalcontrol/hustzc

https://gitee.com/totalcontrol/hustzc

下载Logisim

一小时玩转

![]()

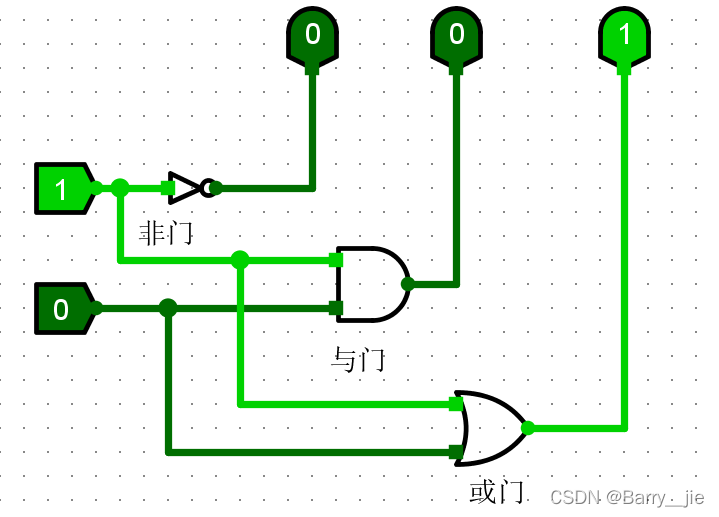

改变值 选中 文本 输入 输出 非门 与门 或门

![]()

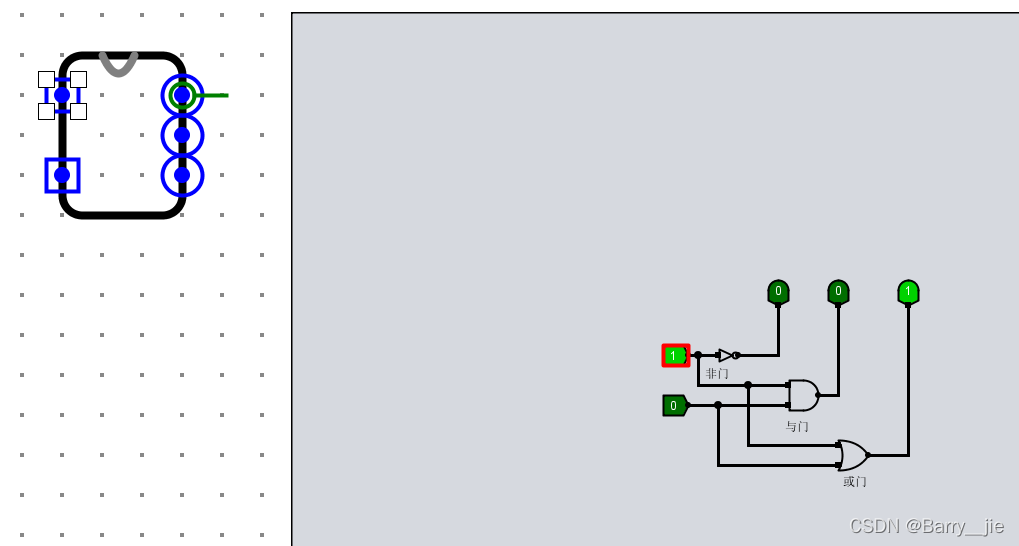

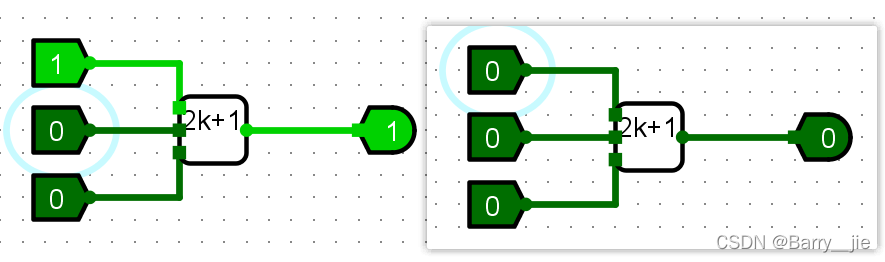

分立 封装

将刚才的电路封装成芯片 (独立成一个模块)

可在其他电路中调用

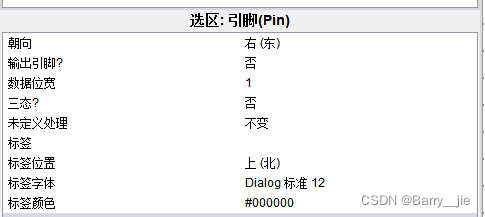

引脚的属性介绍

数据位宽:alt+数字键 快捷 三态:0,1,x高阻态

标签 :用于定于该引脚

高阻态

在某一时刻根据任务需求,这个接口既不接受数据,也不输出数据,那么就需要设置为高阻状态,任凭外部,内部信号数据怎么样变化,这个接口相当于失效,也叫做浮置状态。

ctrl+d 复制 快捷

与门、或门 数字键可快捷设置输入引脚数

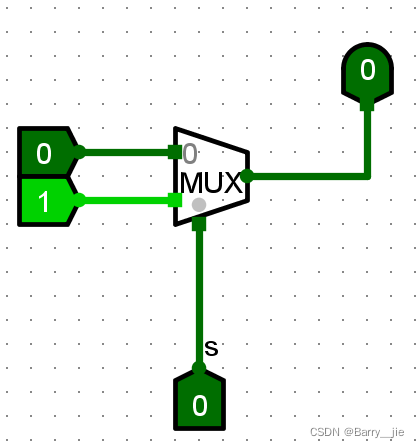

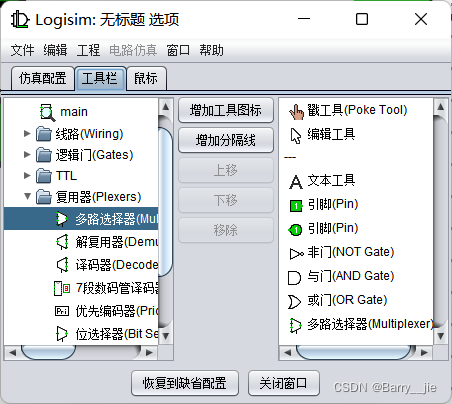

复用器

![]()

s选择端,可再加使能端

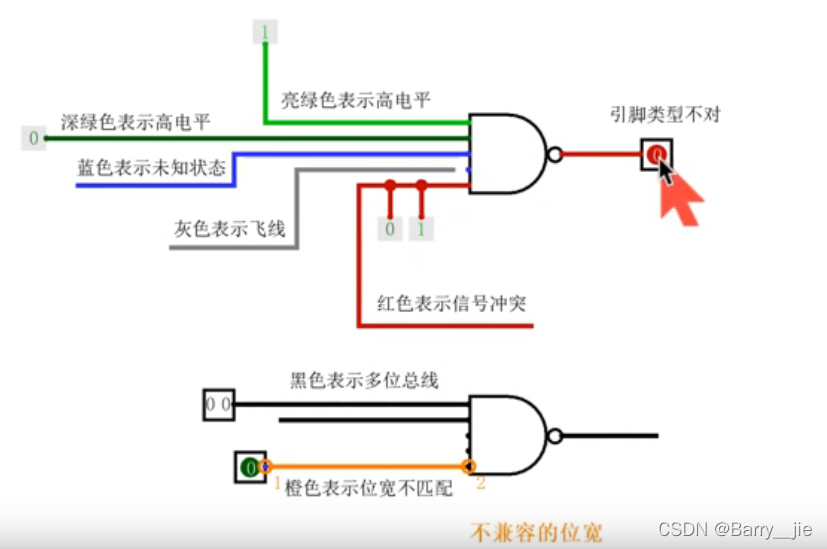

颜色提示

菜单

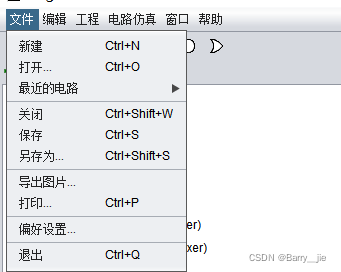

文件

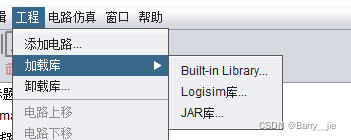

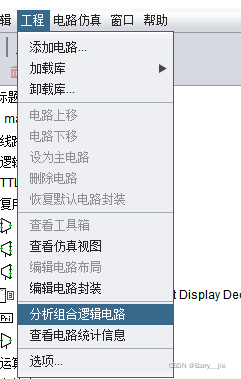

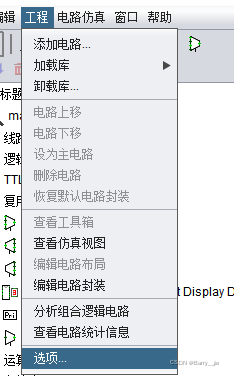

工程

1、加载之前的电路

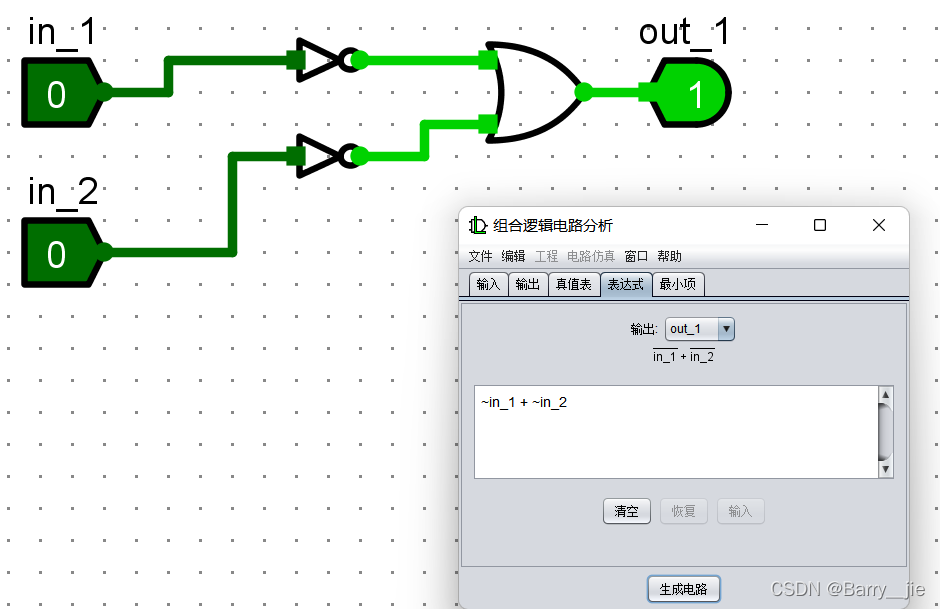

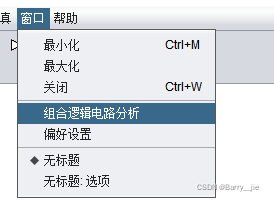

2、分析组合逻辑电路

可以生成真值表、表达式,甚至可以根据输入的表达式生成电路

3、选项

添加快捷图标

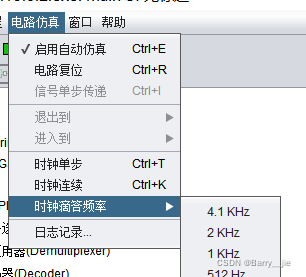

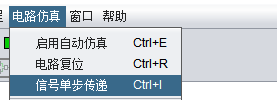

电路仿真

1、电路复位

清除存储器

2、时钟单步

单步仿真ctrl+T、多步仿真ctrl+K

3、信号单步传递(关闭自动仿真时)

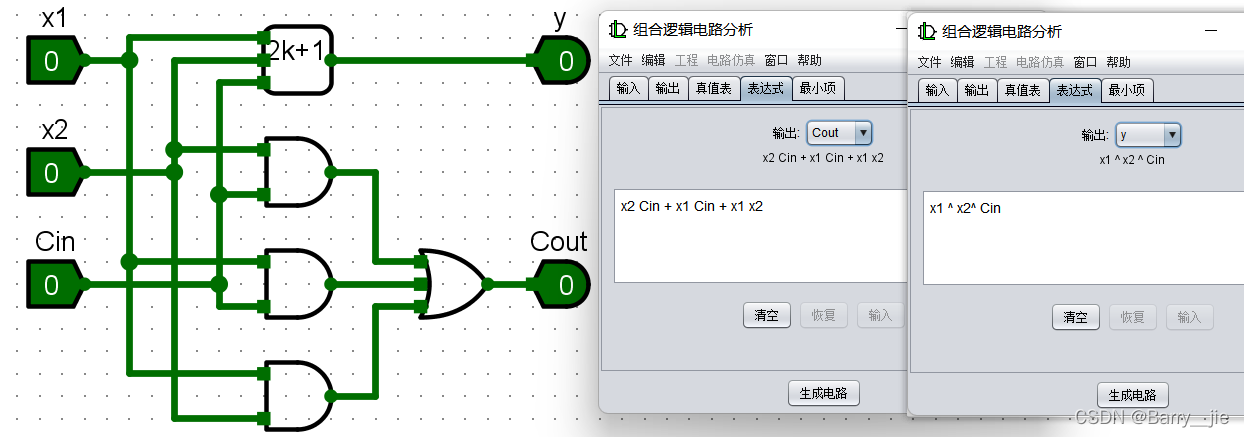

信号单步传递ctrl+I 信号一步一步传递,可看见过程

是将一刻的信号传递过程拆解

自动生成电路

限制:组合逻辑电路,输入只能是一位,输入引脚上限8个,输出引脚上限12个

以一位全加器为例

输入表达时(或者输入真值表),即可生成电路

奇偶校验器

奇数个1输出1,偶数个1输出0,可在输入端加非门反转性质

未完待续……

9万+

9万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?