一.原理与设计

组合逻辑电路的设计比较简单,根据加法原理可以知道:

将乘法分解为1位*3位二进制的乘法,进一步分解为1*1位的二进制乘法。得到1*3位的组合电路之后,作为3*3位乘法器的一个子模块。设计三个子模块的运算,最后将三个子模块输出结果按权相加即可得到3*3位组合逻辑乘法器。

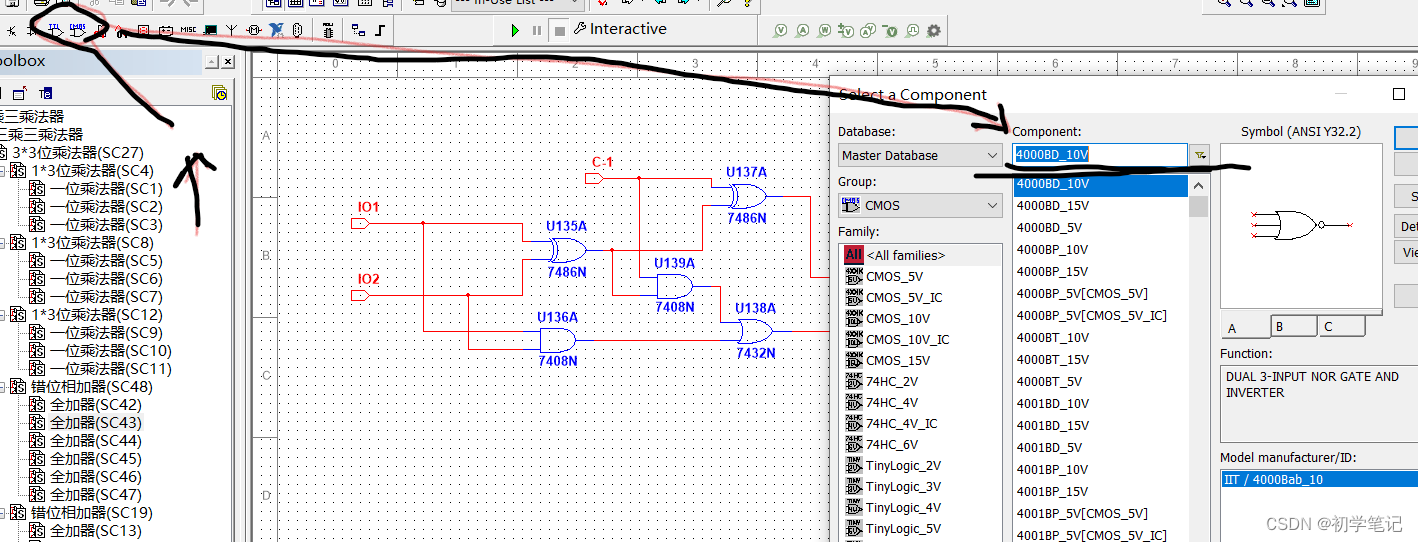

如果不懂子电路图,可以搜索“Multisim如何设计子电路图”得到答案。

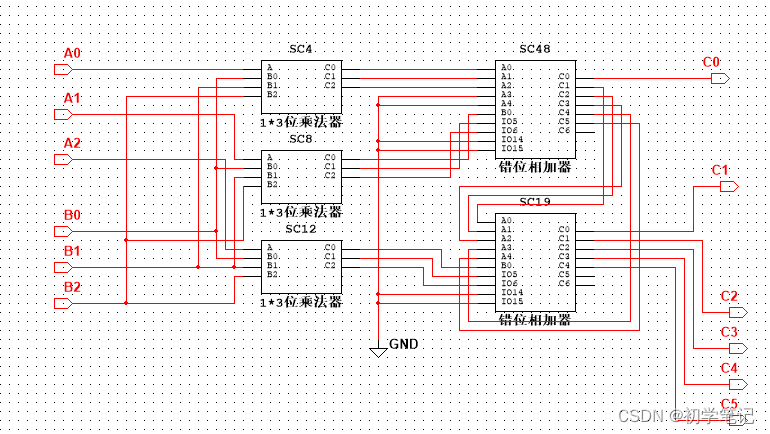

整体设计如下图:

分解为乘法模块 和 加法模块;

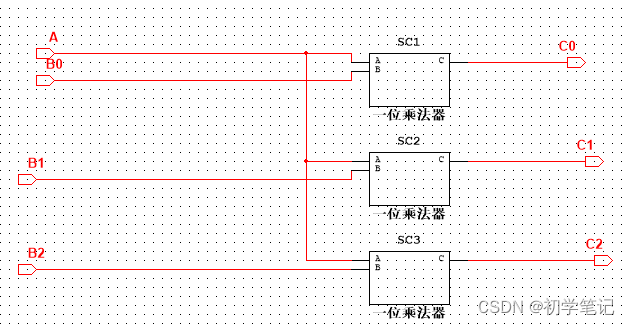

其中的乘法模块很简单:用三个一位乘法模块构成;

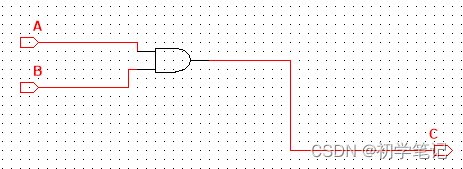

一位乘法模块:

加法模块也很简单:

需要把得到的三个乘数结果相加,不过相加的时候要错位相加;

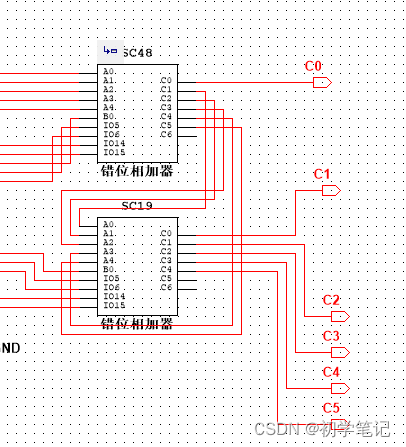

要解决这个错位相加的问题,可以设计六位加法器,位数可以用0来填充;

也可以直接2错位相加;如何选择并不重要,实现功能即可。

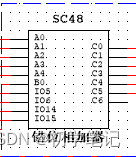

这里我选项的是设计错位相加器:

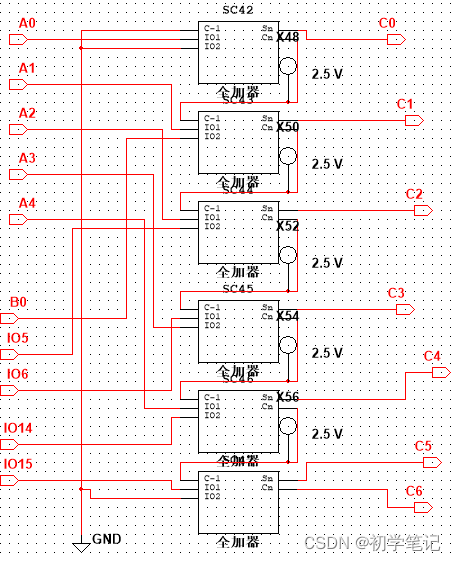

展开电路如下:

使用6位错位相加器的时候,会自动将B输入即B0以下的输入向高位移动一位。

得到的最后一位C0可直接作为乘法的最后结果输出:

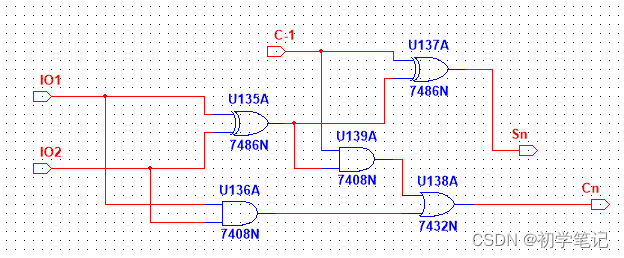

如果不知道如何设计全加器可以参考我的设计:

用到的元器件直接在搜索框里面搜索。

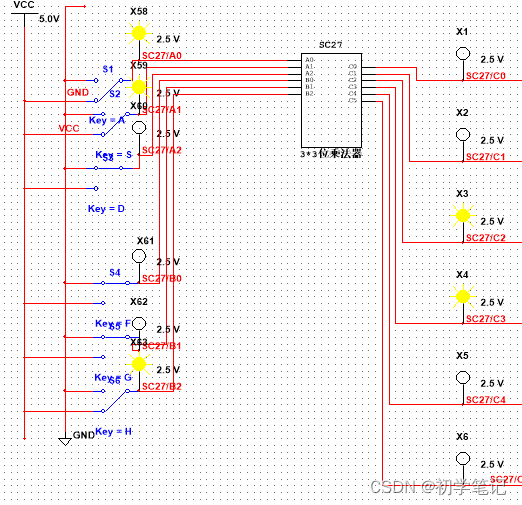

二、 最后一步,电路的检验

可以使用开关对输入信号进行控制,也可使用信号模拟器对输入信号进行模拟;

技巧:用信号灯泡检测信号可以更直观的看到效果。

检验:011*100=001100

本文详细介绍了如何通过分解和组合逻辑电路来设计3*3位的乘法器。首先,将乘法转换为一系列1位乘法,然后利用多位加法器实现错位相加。乘法模块由3个一位乘法模块组成,加法模块则通过6位错位相加器完成。最后,通过电路的检验确保设计正确性,使用信号灯泡检测和信号模拟器验证了011*100=001100的计算结果。

本文详细介绍了如何通过分解和组合逻辑电路来设计3*3位的乘法器。首先,将乘法转换为一系列1位乘法,然后利用多位加法器实现错位相加。乘法模块由3个一位乘法模块组成,加法模块则通过6位错位相加器完成。最后,通过电路的检验确保设计正确性,使用信号灯泡检测和信号模拟器验证了011*100=001100的计算结果。

1714

1714

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?