文章目录

CPU概述:

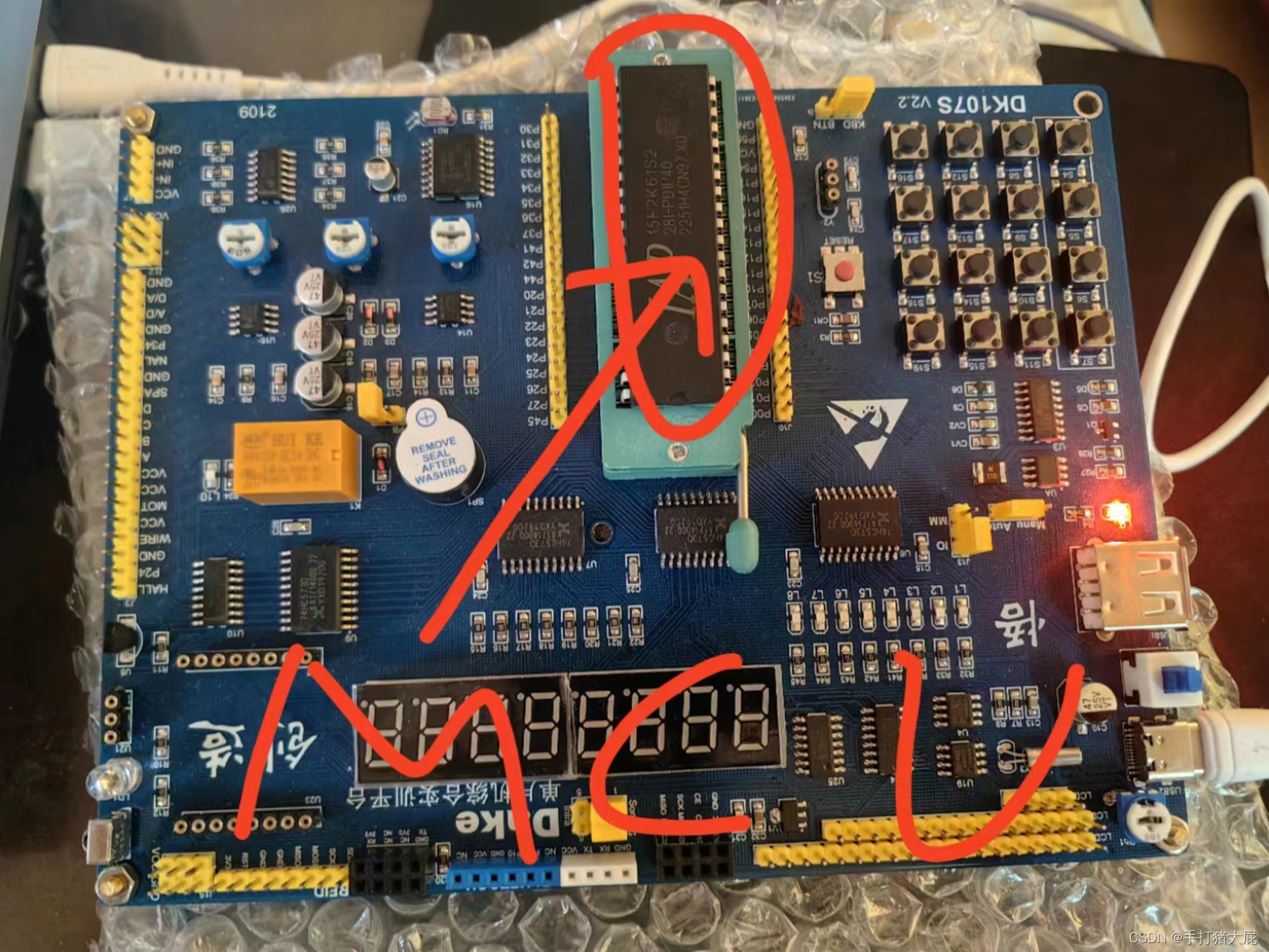

CPU是计算机的核心部件,一个基础的CPU由运算器、控制器、寄存器等器件相连,这些器件靠内部总线相连,CPU通过内部总线与内部各个器件进行联系,例如读取内存中的程序;CPU通过外部总线实现与主板上的其他器件的联系,例如我们使用的蓝桥杯单片机开发板上就存在着矩阵按键、LED灯、蜂鸣器等外设。

CPU(中央处理器)和MCU(微处理器 = 单片机)的区别:

- CPU: 即中央处理器,是计算机系统的核心部件,负责执行程序中的指令,处理数据和进行逻辑运算。它通常与内存、I/O设备等通过总线相连,但并不包含这些组件。CPU需要外部存储器和外设接口电路的支持才能正常工作。

- MCU: 即微控制器,是一种将CPU、内存(如RAM、ROM等)、I/O接口等外围电路集成在单个芯片上的计算机系统。它不需要外部存储器和外设接口电路的支持就能独立工作。MCU的内部资源相对有限,但其高度集成和低成本的特点使其在许多嵌入式应用中得到广泛应用。

就拿我们手上的单片机开发板来说,单纯一个板子叫做开发板,而真正的单片机是上面的芯片,也就是MCU,而单片机里面就封装了CPU和内存、I/O接口等一些器件

CPU是如何工作的:

首先,CPU需要从内存中获取指令和数据,于是才能够知道要对哪些数据做什么事,但是对于:

机器码:

1000 1001 1101 1000

数据信息:89D8H

控制信息:mov AX,BX

这段机器码既可以表示数据信息:89D8H(这里的H是hex也就是十六进制的意思,1个16进制数对应4位2进制数所以89D8分别对应上面16个二进制数。也可以表示控制信息:将BX寄存器中的数据移动到寄存器AX中 = 汇编语言:mov AX,BX(汇编不区分大小写)

那么CPU是如何区分这段机器指令是表示数据信息还是控制信息的呢,这就要说到我们的总线。

CPU是如何区分内存中的指令和数据的:

CPU进行数据的读、写操作时,先通过总线或串口与器件的芯片进行交互,通常为总线,逻辑上有三类总线:

- 地址总线

- 数据总线

- 控制总线

也就是说1000 1001 1101 1000如果是从数据总线传给CPU那CPU就把他当作数据,如果是从控制总线传过来就把它当作控制指令但是从物理上,也就是我们能看到的层面上来说他们就是一根根导线的集合没什么区别

演示视频——出自哔哩哔哩小甲鱼 :

读和写:

CPU_read_write

地址总线:

- CPU是通过地址总线来指定存储单元的,地址总线上能传送多少不同的信息 = CPU可以对多少个存储单元进行寻址,大部分操作第一步都是先分配内存,分配的时候肯定需要知道内存的地址,一个CPU有N根地址总线,则可以说这个CPU的地址总线宽度为N,这样的CPU最多可以寻找2的N次方个内存单元

(例如:8根地址总线能够对0000 0000~1111 1111范围内包括两点的地址进行寻址 = 2 的 8次方)

数据总线:

- CPU通过数据总线实现与内存或其他器件之间的数据传送,数据总线的宽度决定了CPU与外界传输数据的速度

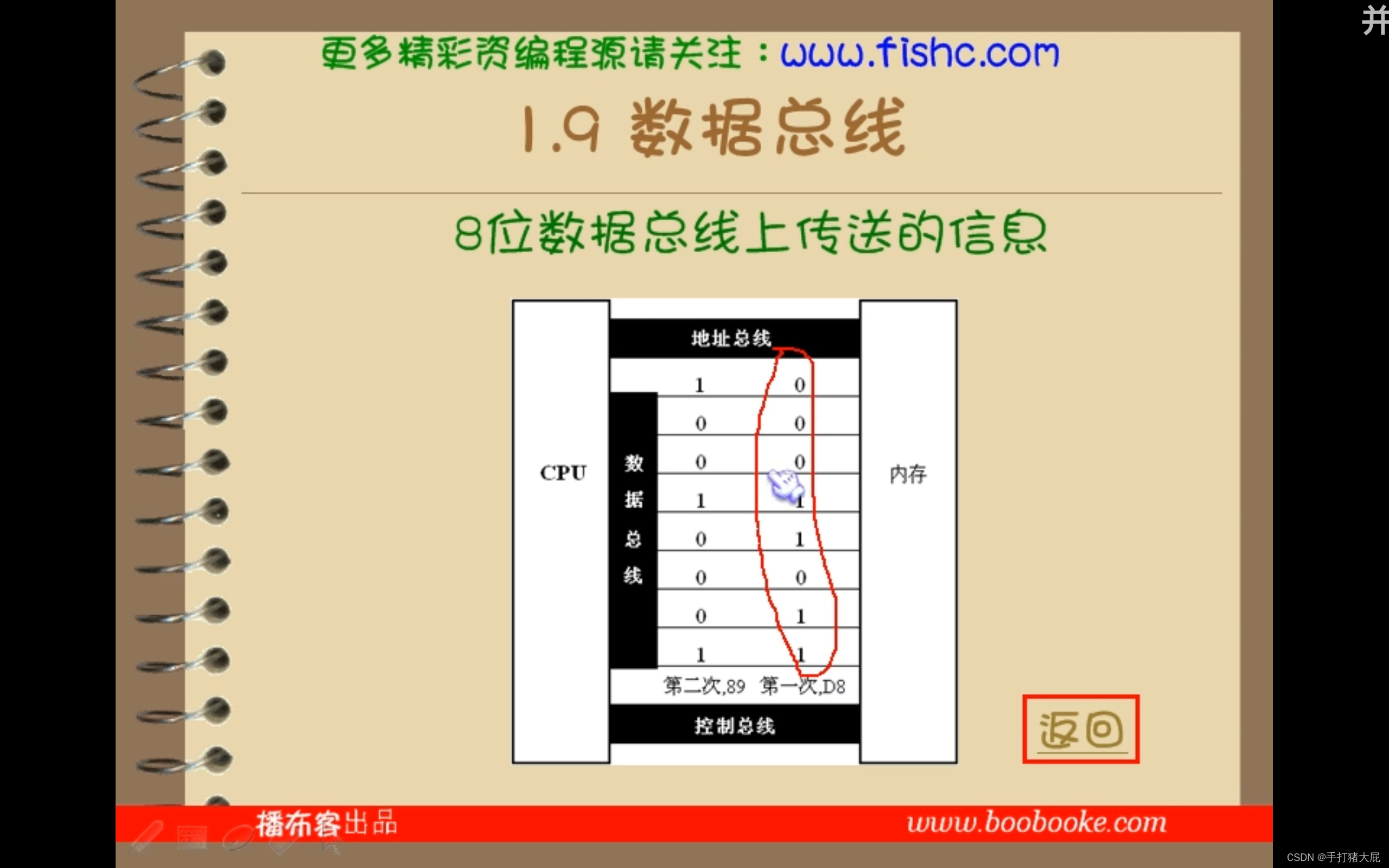

图示:

例如:数据 89D8(十六进制)

对于一个八位CPU,而一个十六进制数代表4个二进制数,所以8位的CPU第一次会先将低八位传输过去也就是**D8**,第二次为89(从低位到高位进行寻址),所以一个16位CPU传输数据的速度是8位的两倍。

控制总线:

- CPU想要实现对外部器件的控制就必须由控制总线向对象发送指令,控制总线是一些不同控制线的集合,**

有多少根控制总线就意味着CPU提供对外部器件的多少种控制和所能控制的器件数量,**CPU一次只发送一条控制指令,一条线从二进制上来说就是1和0两个数字代表着低电平和高电平,所以一条线就能控制一个器件,对其发送读写或开关等简单操作,同时也存在复杂的控制指令,控制总线数量多的在发送复杂的控制指令时就具有更快的速度,控制指令的位数取决于CPU的指令集架构和数据总线宽度。不同的CPU和指令集可能有不同的指令长度。例如,x86指令集中有多种不同长度的指令,包括8位、16位、32位和64位的指令。而ARM指令集也有32位和64位的指令。

视频演示:

存储器:

- **从读写属性上看分为两类(也就是哪些可以存储器可以进行读取和写入操作):

随机存储器(RAM):

特点:数据可以被反复读取和修改,但断电后数据会丢失。

用途:用于临时存储正在处理的数据和程序,如操作系统、应用程序以及用户数据等。

性能:读写速度较快,但数据易失。

只读存储器(ROM):

特点:数据只能被反复读取,但不能被修改或删除。

用途:通常用于存储固定不变的程序或数据,如启动引导程序、硬件的固件等。

性能:读取速度较快,数据不易失,但写入困难。

总的来说RAM用于临时存储可变数据,而ROM用于存储固定不变的程序或数据。 我们手机所说的运行内存也就是随机存储器,运行一个应用时这个应用的程序就会被读取到运存中并被CPU运行,于是应用打开,然后在我们关闭这个应用的时候这个应用的数据就会从我们的运存中删去,所以下一次打开需要重新进入。而我们手机中保存着我们手机系统文件的内存就是只读存储器,不可修改。

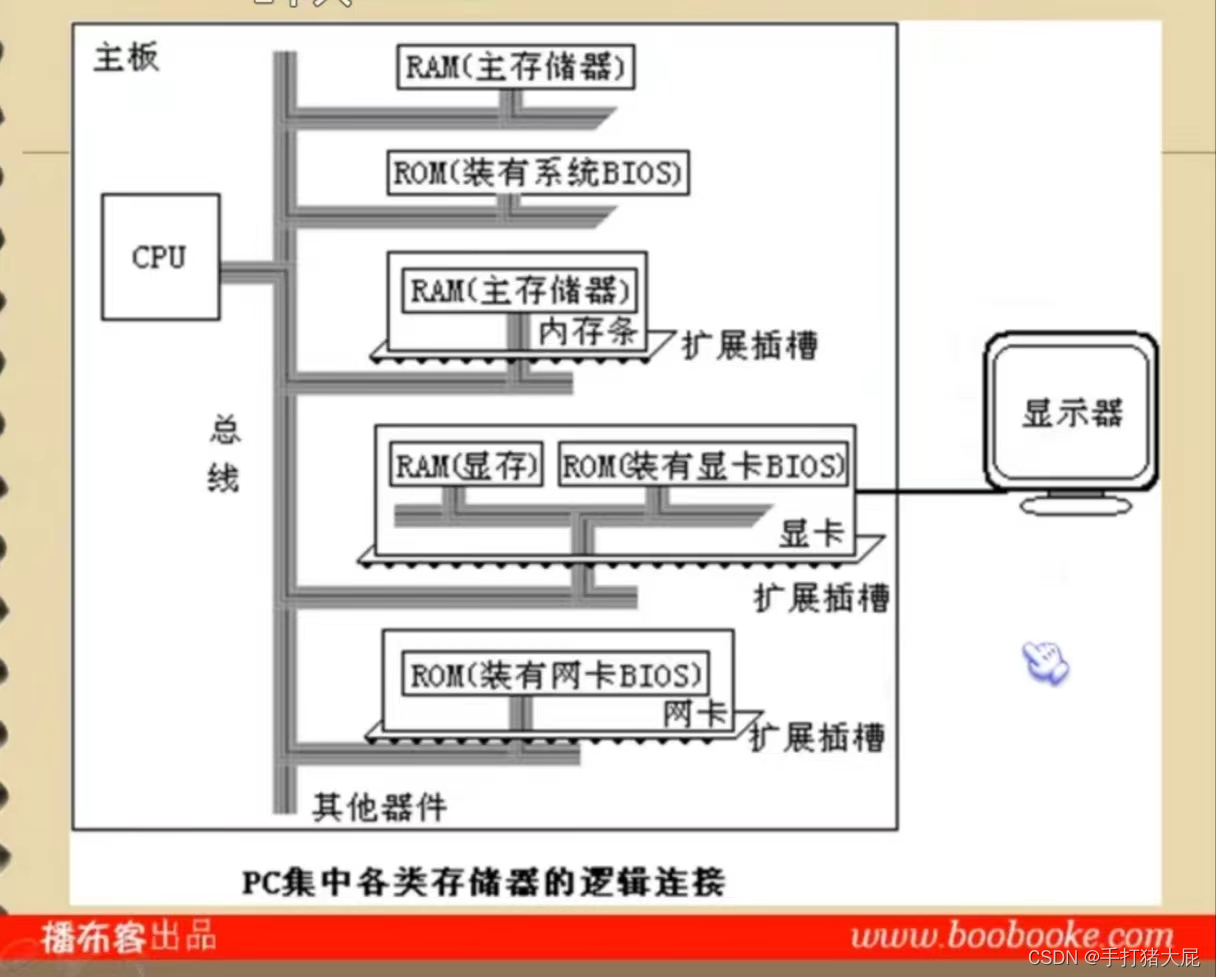

- 各类存储器:显存、主存

CPU的角度看内存:

对于CPU和GPU来说内存并不会分为主存和显存,在它们眼里内存就是一块没有差别的地,他不会区分哪一块是显存哪一块是主存,只是CPU负责执行程序指令、处理数据和进行逻辑判断等核心任务。而GPU则是专门为图像和视频处理设计的电子电路,其核心功能是进行大规模的并行计算,专门处理图像和视频数据,以提高图形渲染和计算性能。因此将内存分类可以提高计算机运行的效率,将视频图像等等放在一块特定的区域,则GPU进行寻址时就不需要对整个区域进行寻址,CPU运行时也同理,就例如需要找西瓜,就直接去划分好的水果区去找,而不是将整个农场都找一遍。所以这些所谓的地址分类是我们人自己划分的,并不是存储器本身就划分好的。

- 由图片看出存储器在物理上也就是我们能感觉到能看到的层面上是独立的器件,但它们都和总线相连,CPU对它们进行读写时都是通过控制线发出内存读写命令。

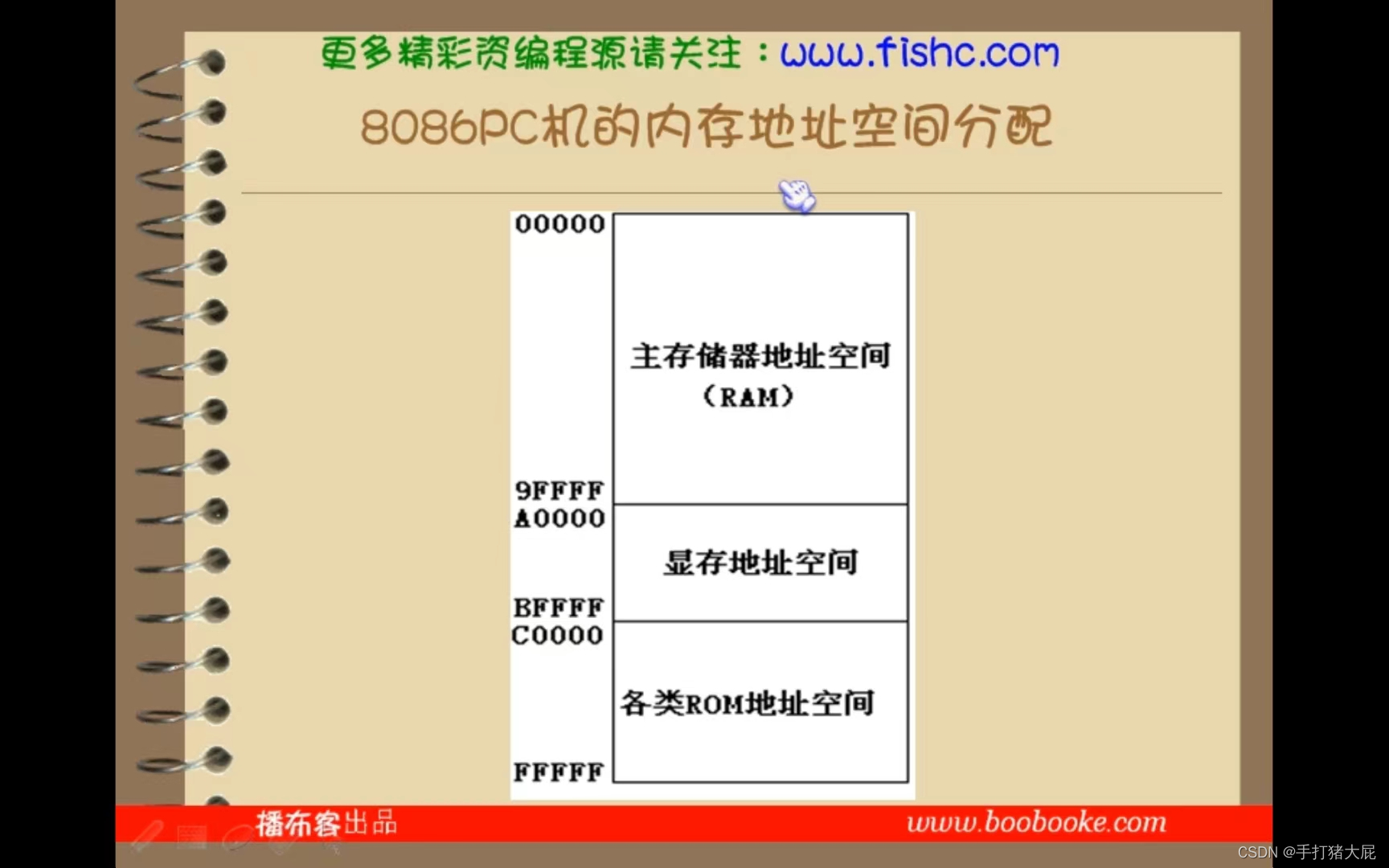

CPU访问内存:

- C0PU访问内存时要给出所要访问的内存单元的地址,所有的内存单元构成的存储空间都是一个一维的线性空间,也就是它们的地址就是从0~64按照顺序就像整数的数轴那样连续,其中一个存储单元的地址叫做物理地址。

一个16位架构的CPU具备的特点:

注意: 无论是16位还是32、64位的CPU,数字指的是它们的数据总线的宽度,也就是该CPU一次性能够处理数据的位数,而不是地址总线的宽度。

1.运算器一次最多可以处理16位数据

2.寄存器最大宽度位16位

3.寄存器与运算器之间的通路是16位的

不同架构的CPU特点是相同的,64位架构的CPU特点与上述的16位相比,其特点只是将16改为64

示例:16位架构的8086CPU给出20位物理地址的方法:

-

8086CPU内部是16位架构,但是它外部却有20位地址总线,可以传送20位的地址。

-

问:那么8086CPU是如何将内部的16位地址转换成20位地址传送给外部的呢

-

答:8086CPU采用一种在内部用两个16位地址合成的方法来形成一个20位的物理地址

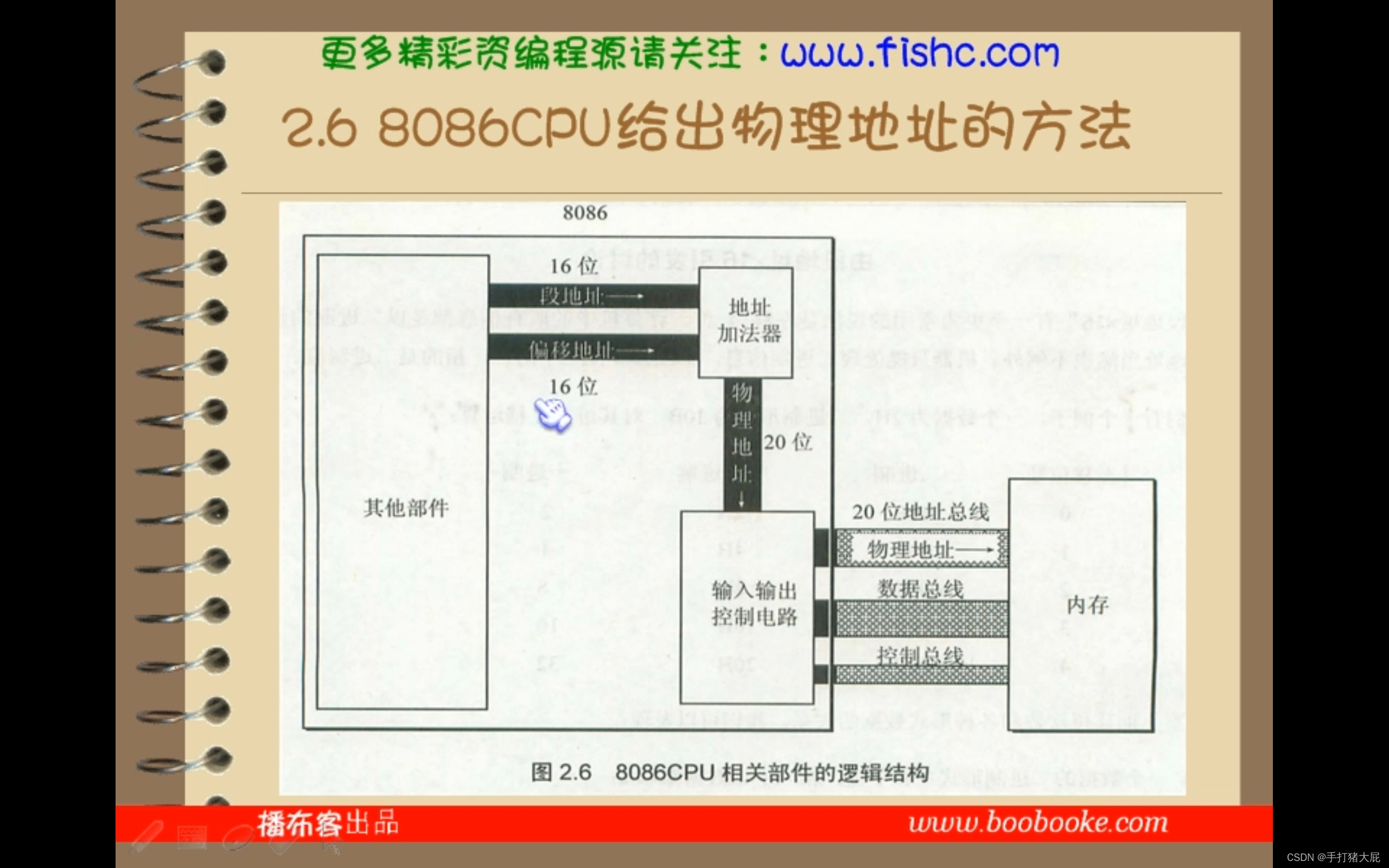

图示为8086CPU的内部逻辑结构图,但不是实际结构体,但也是根据这个逻辑图进行设计的:

在这里插入图片描述

-

在8086 CPU中,尽管它是16位架构,并且大部分内部寄存器确实是16位的,但它确实能够生成并处理20位的物理地址。这是通过特定的地址生成逻辑和内部总线来实现的,而不是通过单个的20位寄存器。

具体来说:

当CPU需要访问内存时,它会进行以下步骤:

1.段寄存器左移: -

CPU首先会取一个段寄存器(如CS、DS、ES、SS)中的16位值,并将其左移4位(实际上是乘以16),从而形成一个20位的中间地址。

-

这个中间地址的高16位包含了段基址(实际上使用了高12位,因为低4位是0),而低4位则是0。

2.加上偏移量:

然后,CPU会加上一个16位的偏移量(通常来自IP寄存器或指令中的操作数)到这个20位的中间地址上。由于偏移量是16位的,它只会影响到中间地址的低16位。

3.地址加法器: -

地址加法器是CPU内部的一个逻辑单元,它负责将段寄存器左移后的值与偏移量相加,生成最终的20位物理地址。

-

这个地址加法器并不是一个显式的20位寄存器,而是一个能够处理20位数值的逻辑电路。

4.内部总线: -

生成的20位物理地址随后被放置在CPU的内部总线上,这个总线能够传输20位的数据。(刚开始我疑惑的地方就是这个由段地址左移四位后产生的20位中间地址用什么存放,因为8086内部是16位的架构,原来是其内部的地址加法器连有20位的地址总线,但是注意 : 这个20位的地址总线与CPU外部的地址总线不是同一条,这个内部总线是专门用于在CPU内部传输地址的,这个20位地址会被传输到CPU的外部接口电路,并通过外部的地址总线发送到外部的内存或其他设备。)

-

这个地址随后被送到内存接口电路,用于选择相应的内存位置。

5.访问内存:

最后,使用这个20位的物理地址,CPU可以访问外部内存中的相应位置。

总结: -

尽管8086 CPU内部能够生成和处理20位的地址,但它的寄存器确实是16位的。这意味着在任何时候,一个单独的寄存器只能保存16位的信息。然而,通过组合多个寄存器和偏移量,并使用地址加法器,8086能够访问1MB的寻址空间,这需要20位的地址。

段地址:

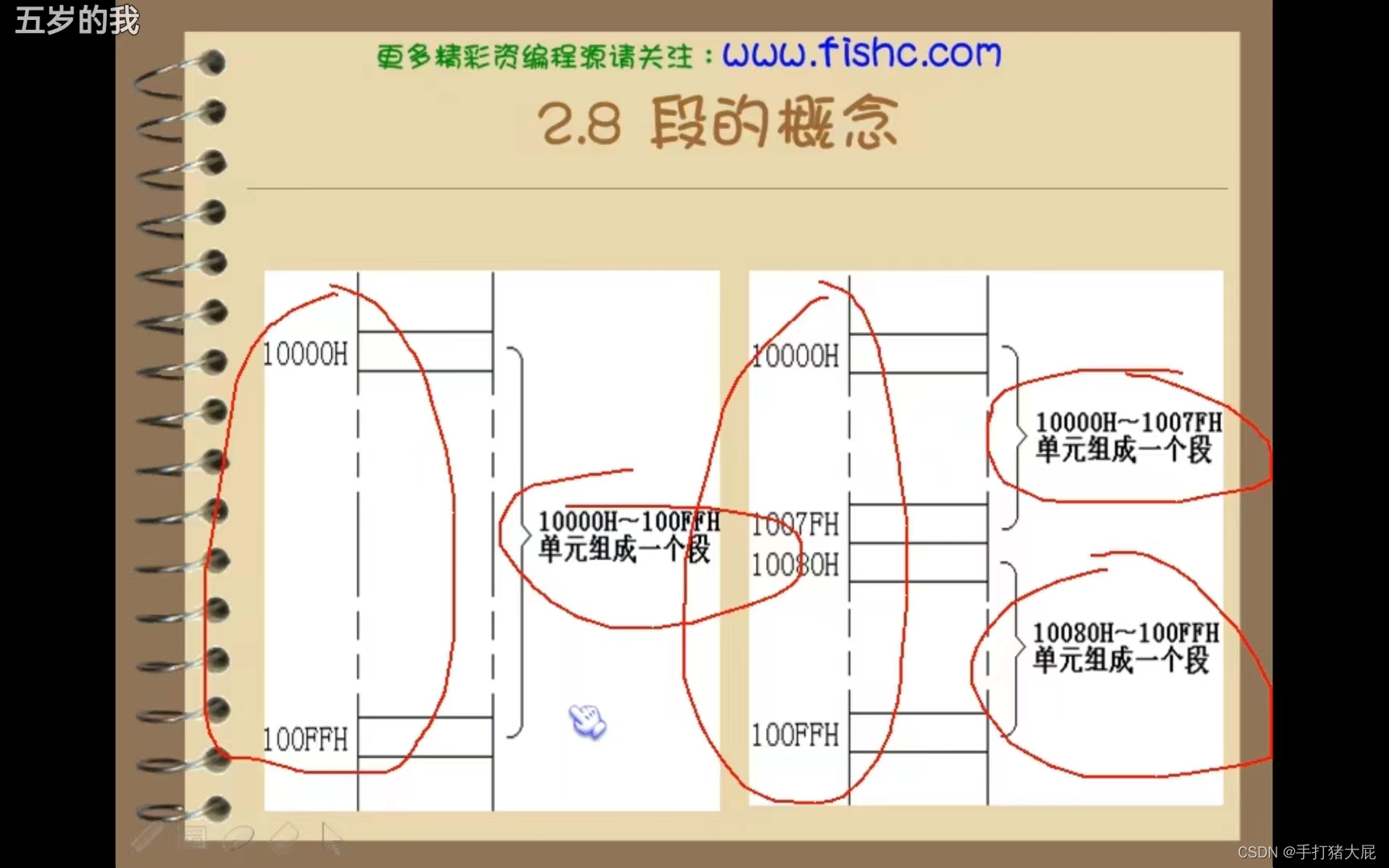

- 错误的认识: 内存被划分为不同的段,每一段有一个段地址。

- 正确的认识: 内存没有被分段,它就是像一条包括0的正整数轴一样,完整的一条,段的概念来自于CPU,因为16位的8086CPU是用 段地址(默认第一个传入CPU的地址就是段地址)×16 + 偏移地址(第二个传入的) = 物理地址(20位),所以我们才会用分段的方式来管理内存,是主观的,我们可以根据自己的需要将连续的地址分为不同的段。但是这是16位8086CPU采取的一种称为“段寻址”的技术来扩展其寻址能力,使其能够访问20位的物理地址,而32位、64位的CPU是不需要这种技术的 所以不是意味着32位的CPU就需要采用这种方法来达到36位寻址,一个标准的32位CPU不能直接传送36位的地址。如果需要使用超过32位的地址空间,通常需要使用其他技术或升级到支持更大地址空间的CPU架构。

小甲鱼习题:

小甲鱼习题检测2.2答案:

(1): 00010到0001F

解析: 偏移地址为16位,变化范围位0~FFFFH,所以偏移地址的范围 + 段地址×16 = 可寻址地址范围

(2): 最小为1001H 最大为1FFFH

解析: 要想寻址到这个范围的地址,那就说明段地址×16 + 偏移地址 的范围要包含这个地址,然后找最大最小

最小:

1 0 0 1 0(段地址)

F F F x(偏移地址,x任意)

2 0 0 0 x

最大:

1 F F F 0(段地址×16)

0 0 1 x(偏移地址,x任意)

2 0 0 0 x

思考: 题目的意思就是 段地址×16 + 偏移地址 的范围不能包含20000H

1752

1752

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?