1 基本逻辑符号

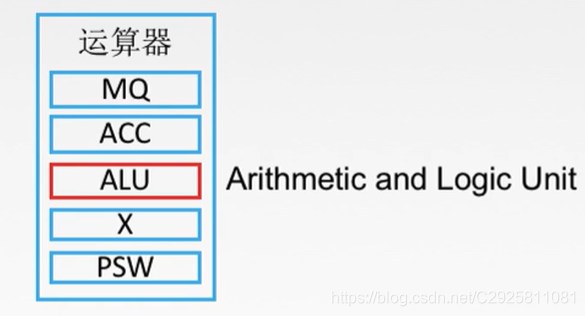

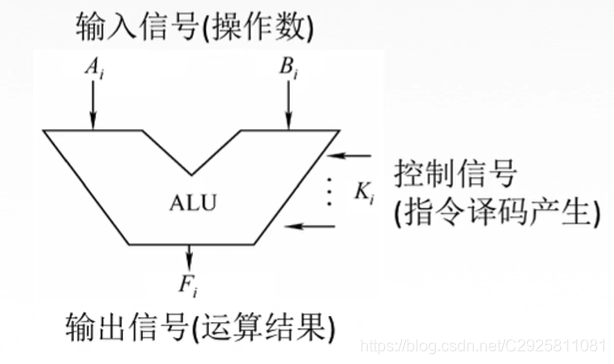

1.1 ALU

ALU功能:算术运算:加、减、乘、除等

逻辑运算:与、或、非、异或等

辅助功能:移位、求补等

逻辑上的ALU:

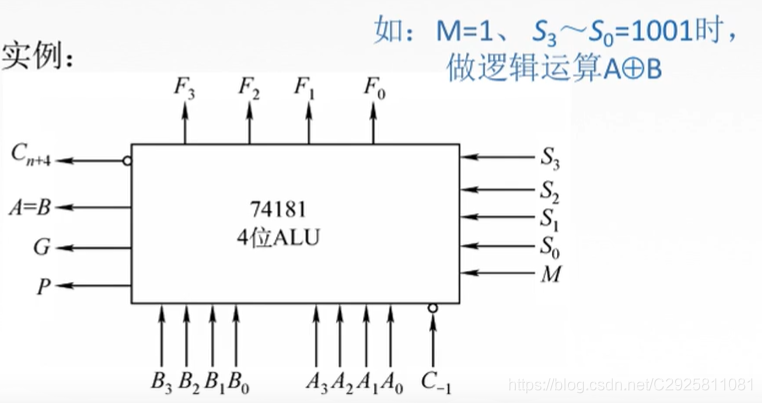

实际上ALU结构:

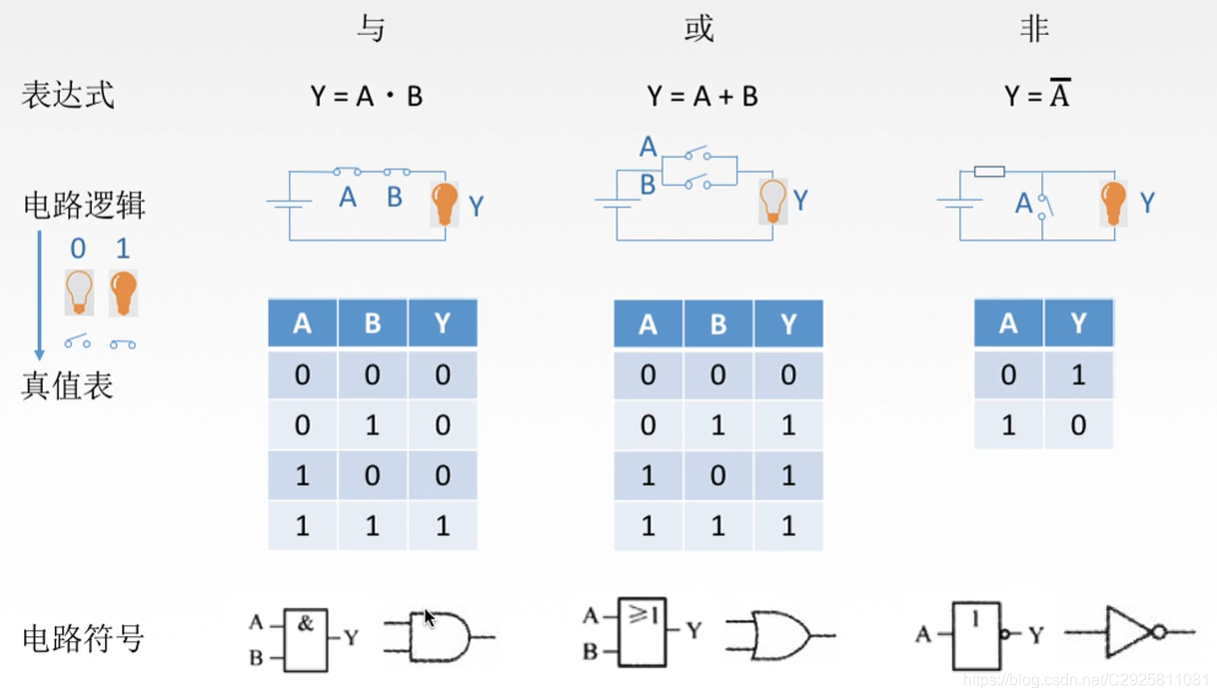

1.2 逻辑符号

可以通过与门来屏蔽一些信号

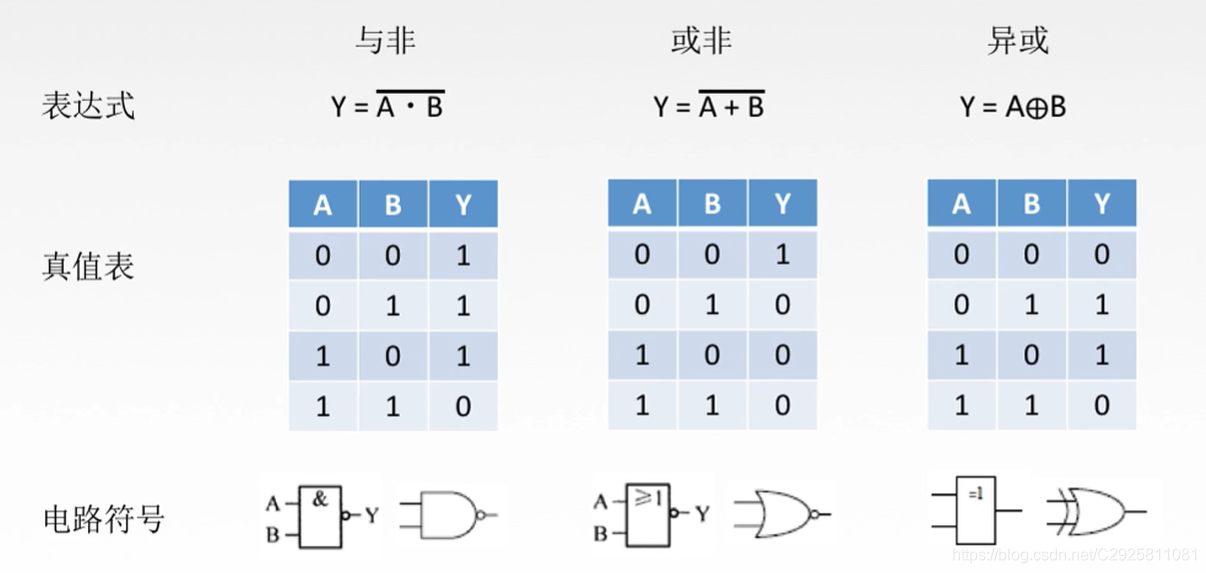

1.3 复合逻辑

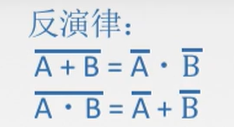

反演律:或非之间进行转换

- A和B不用的逻辑用异或表示一>A=0且B=1或A=1且B=0

异或实现加法,奇偶判断

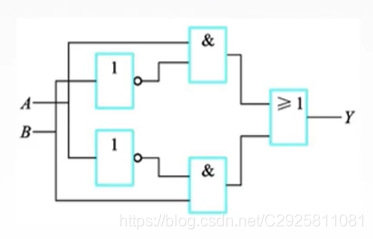

与非和或非是最强大的两个逻辑,通过与非和或非的排列组合可以表示其他所有的逻辑

2 加法器设计

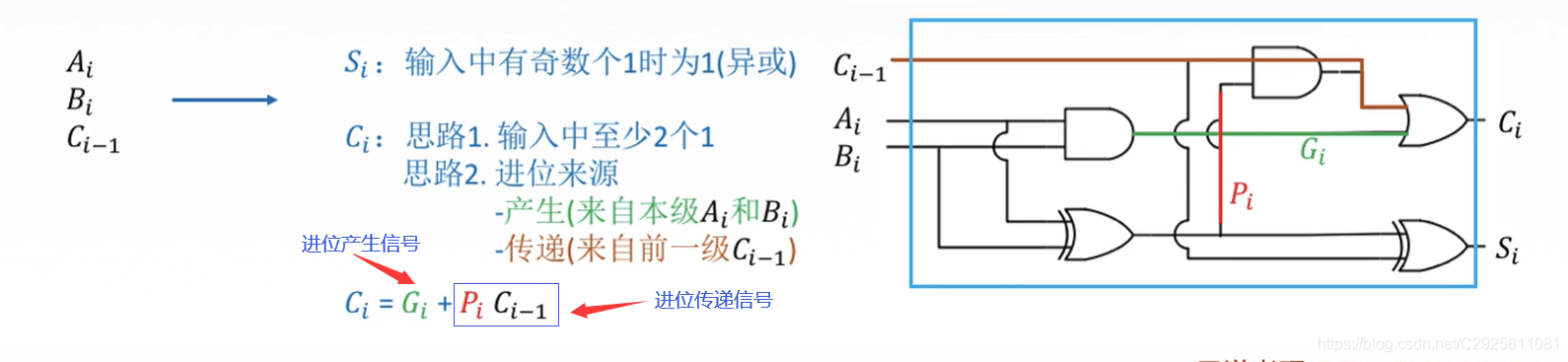

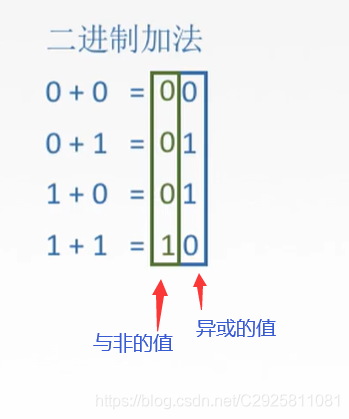

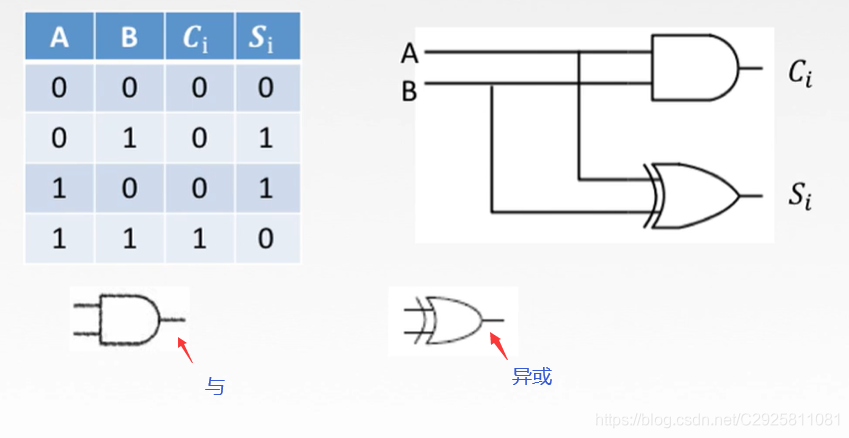

2.1 一位加法器

一位全加器:一个与门+一个或门实现一位二进制数加法

通过与门输出的是进位

通过异或门输出的是和

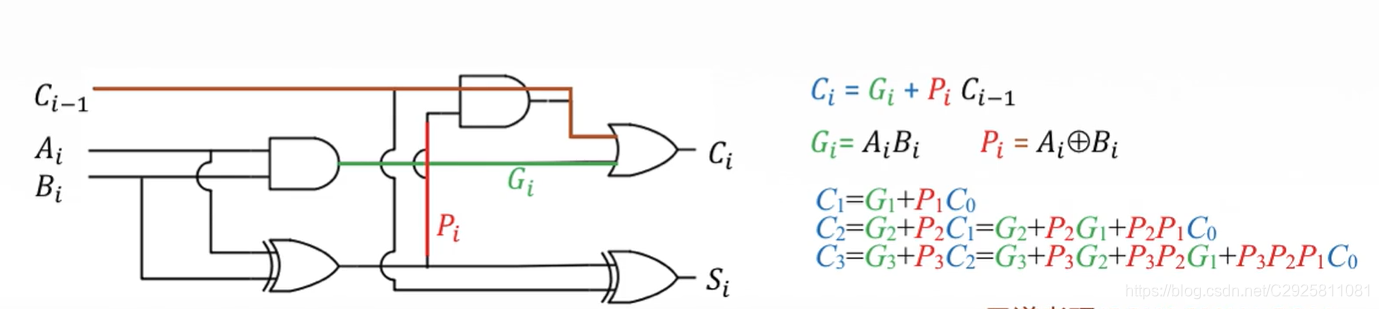

2.2 进位产生原理

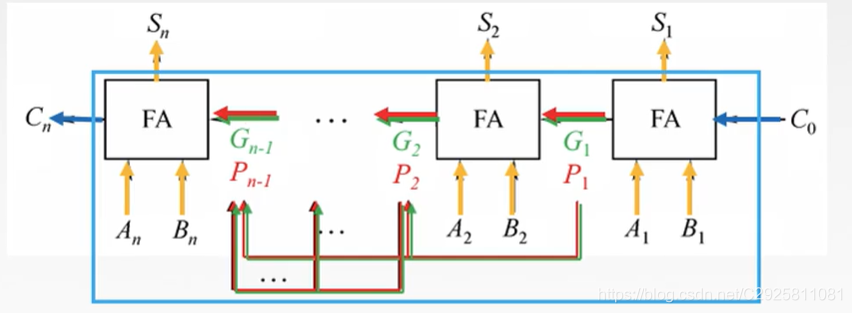

进位输出信号Ci来源于本级两个操作数做个与运算+再由本级两操作数决定是否把低级进位Ci-1往上传递的

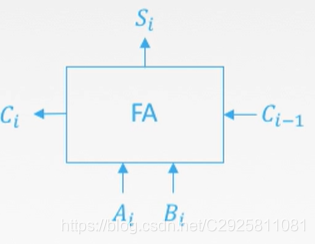

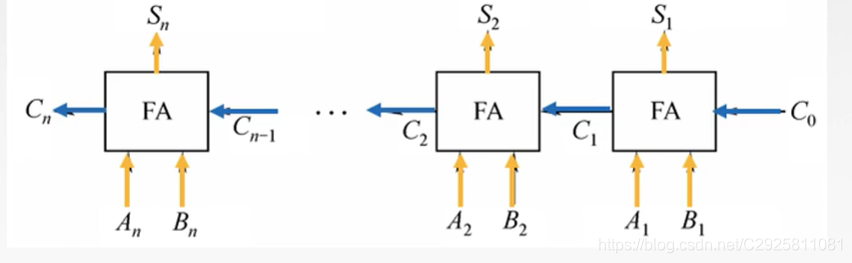

一位全加器封装起来符号表示FA

输入信号:本级A和B以及上一级的进位

输出信号:本级的和以及要传递给下一级的进位

2.2 多位二进制位加法器

- 串行加法器:只有一个全加器,数据逐位串行送入加法器中进行运算。

进位触发器用来寄存进位信号,以便参与下一次运算。

如果操作数长n位,加法就要分n次进行,每次产生一位和,并且串行逐位地送回寄存器。

- 串行进位的并行加法器:把n个全加器串接起来,就可进行两个n位数的相加。

串行进位又称为行波进位,每一级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

- 并行进位的并行加法器:各级进位信号同时形成,又称为先行进位、同时进位

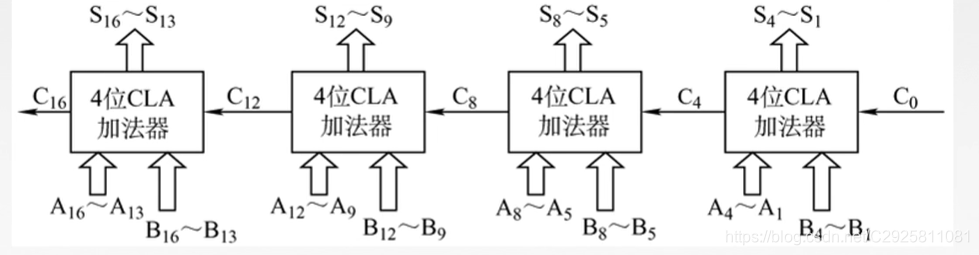

- 单级先行进位方式,又称为组内并行、组间串行进位方式。

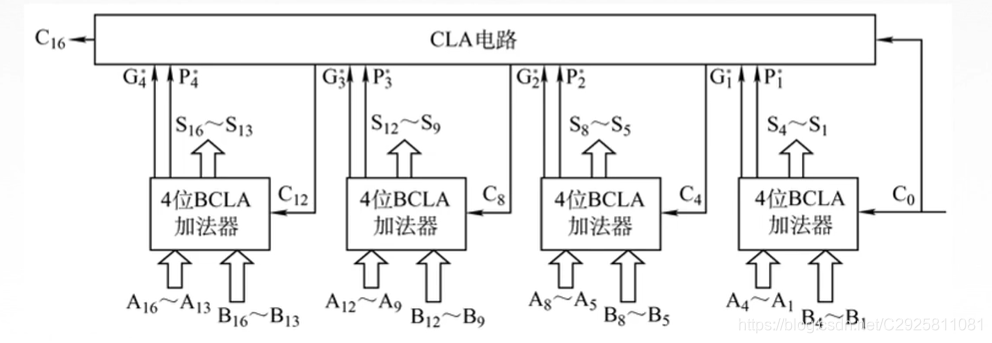

- 多级先行进位方式,又称为组内并行、组间并行进位方式

705

705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?