三、模块设计

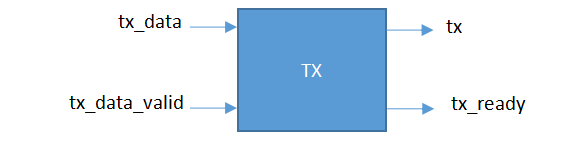

1.TX模块设计

逻辑关系:

tx_data 是输入进模块的并行数据;tx_data_valid是tx_data的使能信号;tx 是输出的每一个采样值(并转串的单bit的值);tx_ready 是模块是否可以接收新的tx_data的信号,逻辑上只有当一组(8bit)信号处理完了,它才会置1(亦或者本身置空的时候也会为1)。

设计思路:

(1) 看输出,tx和tx_ready。tx就是uart传输过程中采样的值,这里表示发射端发送出去的一位一位的值。所以TX的核心工作是把输入的并行数据转成串行数据。

(2)并转串的整个过程如下:

① IDLE:如果start_bit的起始信号(tx_start)为真,则进入START状态;否则就保持IDLE不变。

问题1)怎么定义tx_start信号?

解释:当tx_data_valid和tx_rea

订阅专栏 解锁全文

订阅专栏 解锁全文

2806

2806

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?