(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(微信Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

第九课已经完成了多字节UART通信的设计,可以在实际工程中应用了。但是一般的通信协议是有CRC校验的,有了CRC校验,就可以进一步增加数据的传输正确率。本节主要是讲述在通信协议中如何使用CRC校验,至于CRC校验的公式,CRC是如何运算的,网上的文章很多,在这儿就不具体的讲解了。

本节工程要求:系统时钟是100MHz,低电平复位,使用UART协议完成4byte数据的传输,为了保证数据传输的正确性,每帧数据添加帧头(5a),数据长度(4),CRC8校验和帧尾(a5)。UART的波特率是115200,有奇偶校验位,偶校验。

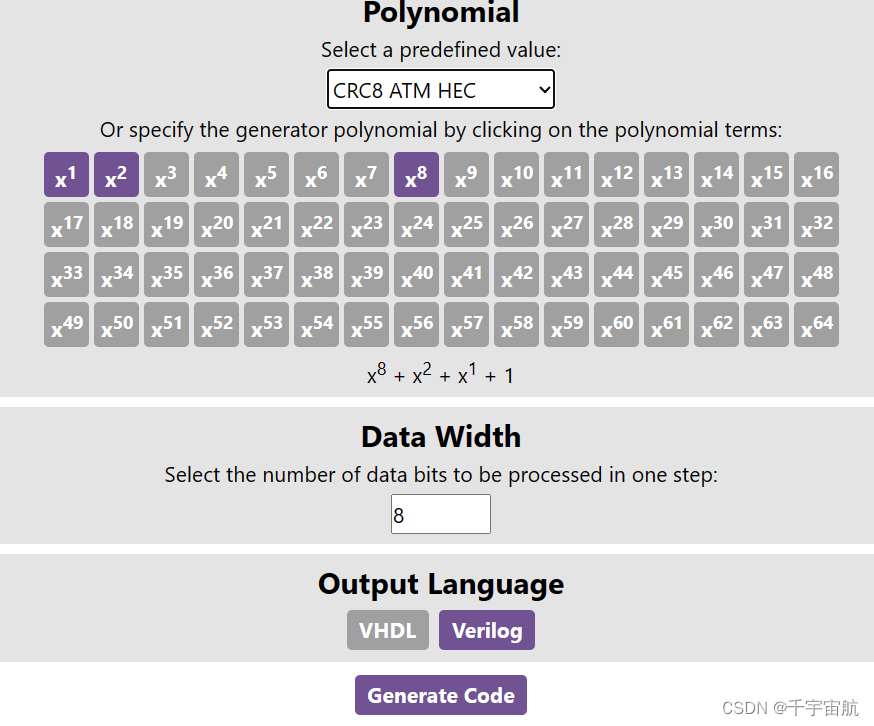

首先要设计一个CRC8模块,这是选择的多项式是X^8+X^2+X^1+1,网上有自动生成verilog代码的网站Easics CRC Tool,进行如下的设置即可以生成相应的CRC的代码。

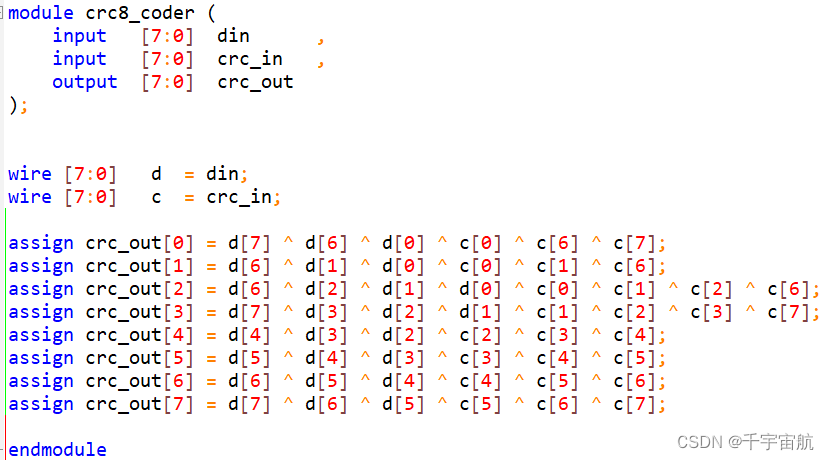

打开后代码如下所示:

笔者根据自己的习惯对该模块进行了改写,如下所示:

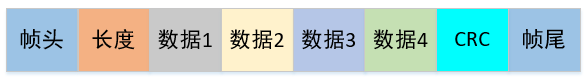

CRC8的模块设计完毕后,考虑一下UART通信协议帧的结构,和第九课相比,多了一个字节的CRC,这儿的CRC是对数据1-数据4的CRC。当然也可以是帧头+长度+数据1-数据4的CRC,这个要根据具体的要求来定。一般的协议中如果有了CRC就不会有帧尾了,本工程主要是教学,所以都保留了。

如下是数据发送和数据接收的状态流程,都是增加了CRC状态。

在发送模块中,增加了CRC状态机的设计。

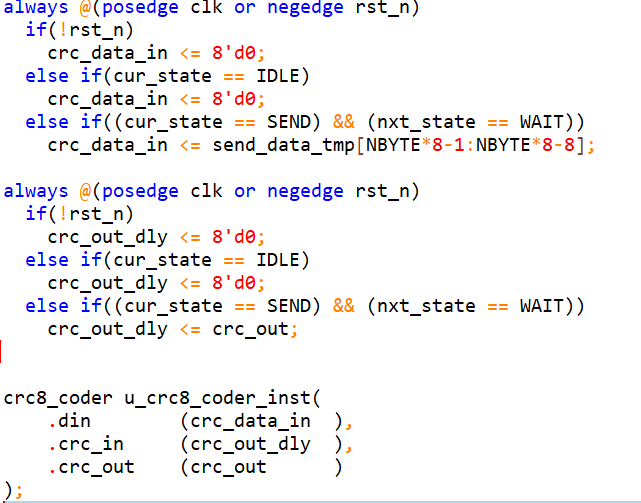

发送模块通过如下的代码完成CRC码的生成,就是将每个要发送的数据和上次计算完成的CRC数据分别送入crc8_coder模块,当4个数据发送完毕后,将crc_out信号在CRC状态内通过UART串行发送出去。

接收模块也是相应的增加了CHK_CRC状态机的设计。

发接收模块通过如下的代码完成CRC码的生成,就是将每个接收的数据和上次计算完成的CRC数据分别送入crc8_coder模块,当4个数据完成接收后,也完成了数据CRC的生成,即crc_out信号。

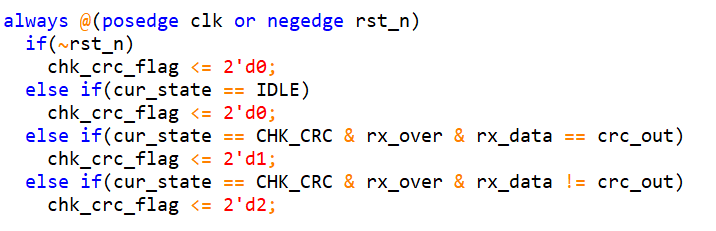

判断接收的CRC和接收模块计算的CRC是否一样,如果一样,说明接收的数据正确,如果不一样,说明接收的数据有错误。

看仿真结果,发送的数据和接收的数据是一样的,功能正确。

最后看看接收端状态cur_state=6的时候是CHK_CRC状态,此时接收模块计算的crc_out和通过UART接收到的rx_data是一样的,说明UART线上传输数据正常,没有误码的产生。

本实例的UART的协议,使用了帧头,数据长度,CRC校验,帧尾,UART的奇偶校验位等多种方式来保证数据传输的正确性!UART还是低速通信,对于PCIE,SRIO,千兆网口等接口,需要用更多的方式来保证数据传输的可靠性!

2347

2347

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?