(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

上节课完成了通用SPI主机发送模块的FPGA设计,那本节课完成通用SPI主机接收模块的FPGA设计。

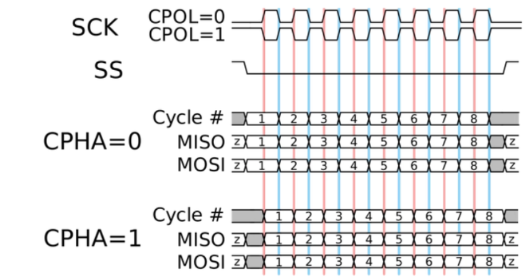

主机的接收模块是主机发送SCK和SS信号,同时解析从机发送的MISO信号,完成数据的解析。还是观察下面的图形,在CPHA=0时,在每个SCK的第一个跳变沿来采集MISO的数据;在CPHA=1时,在每个SCK的第二个跳变沿来采集MISO的数据。

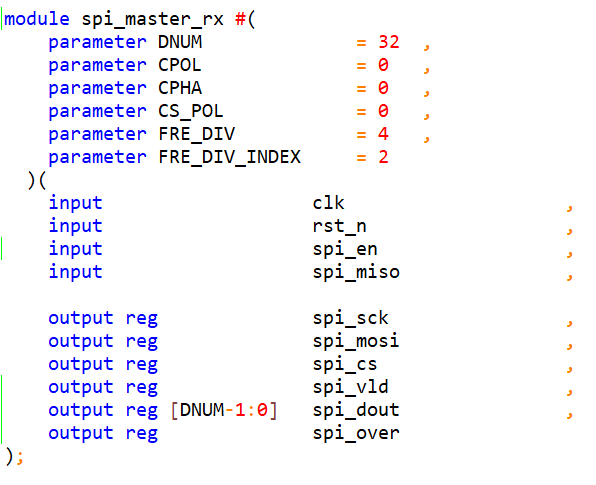

根据上面的分析,我们开始FPGA程序的设计,接口信号如下所示。

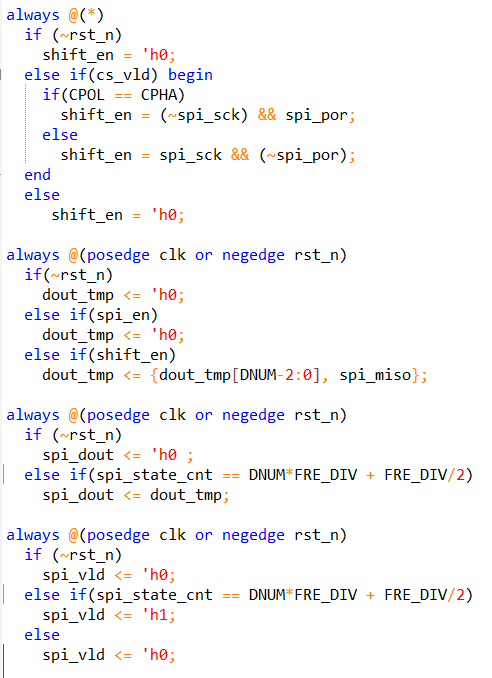

其它信号的设计和SPI主机的发送模块基本一样,就是spi_state_cnt的计数值增加了FRE_DIV/2。该模块的shift_en信号和SPI主机发送模块正好差半个SCK时钟周期,通过shift_en信号完成从机MISO信号的接收和串并转换。

新建仿真文件,模拟SPI从机发送16位的随机数据,主机完成数据的接收。

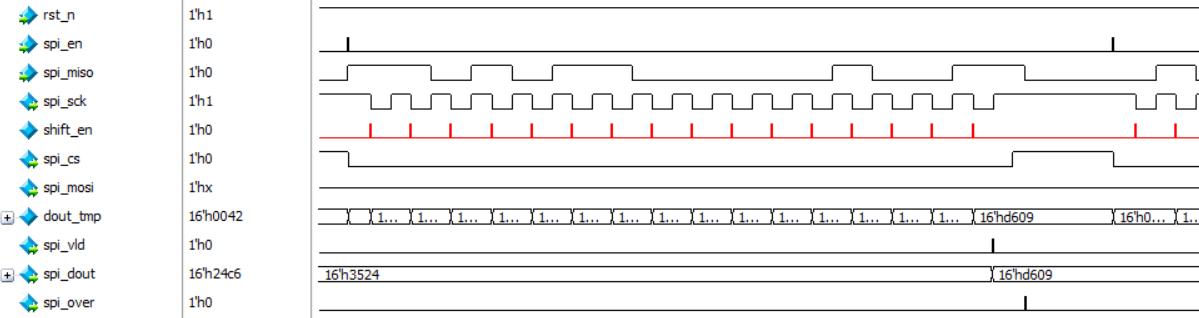

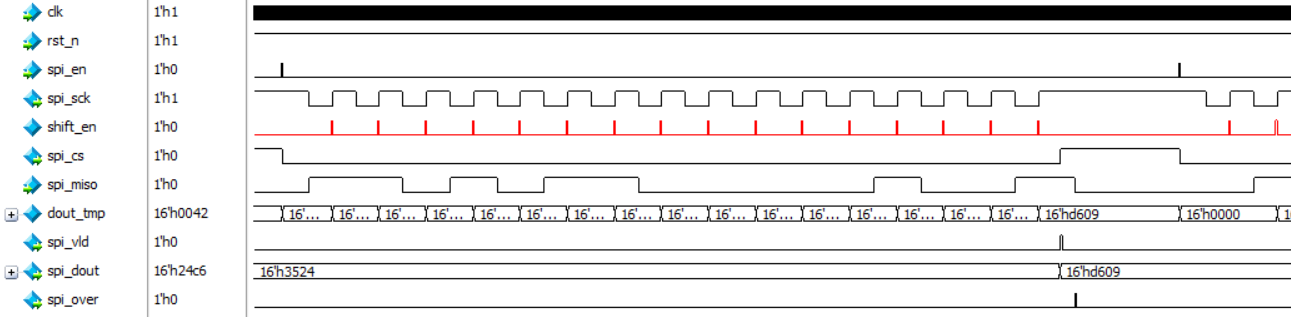

如下所示,CPOL=0和CPHA=0,在SCK时钟的第一个变化沿采集MISO线上的数据,shift_en在SCK的上升沿使能,时序正确。

如下所示,CPOL=1和CPHA=0,在SCK时钟的第一个变化沿采集MISO线上的数据,shift_en在SCK的下降沿使能,时序正确。

如下所示,CPOL=0和CPHA=1,在SCK时钟的第二个变化沿采集MISO线上的数据,shift_en在SCK的下降沿使能,时序正确。

如下所示,CPOL=1和CPHA=1,在SCK时钟的第二个变化沿采集MISO线上的数据,shift_en在SCK的上降沿使能,时序正确。

1629

1629

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?