参考手册:DS182-Kintex-7 FPGAs Data Sheet:DC and AC Switching Characteristics

XAPP587-BPI Fast Configuration and iMPACT Flash Programming with 7 Series FPGAs

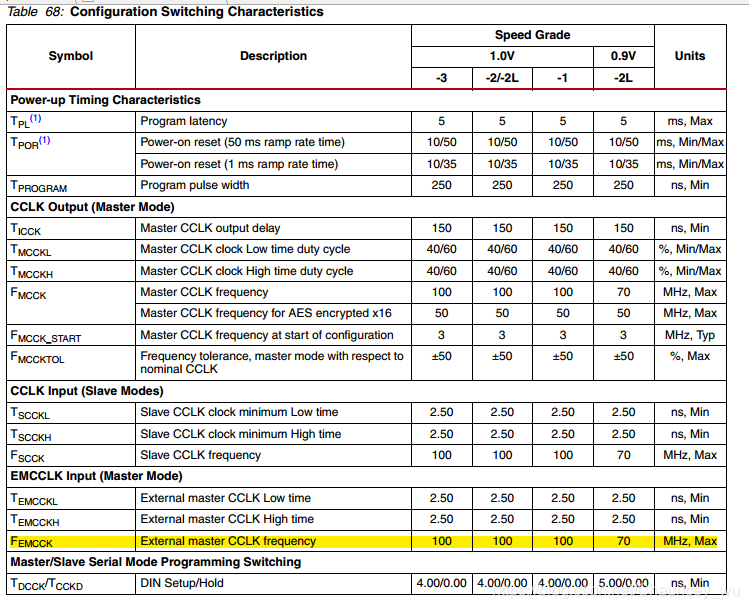

FPGA配置过程中,如果在BitGen软件中选择使用外部时钟,那么EMCCLK外接时钟的频率如何确定?

最大频率 = 1/(CLK到输出有效的延时+FPGA的建立时间+板子延时), 如果板子延时可以忽略不计,最大EMCCLK

将受到数据表规范FEMCCK的限制,最大时钟为100MHZ。

结论:EMCCLK外接时钟的频率一般来说应小于100KHZ,大于66MHZ。

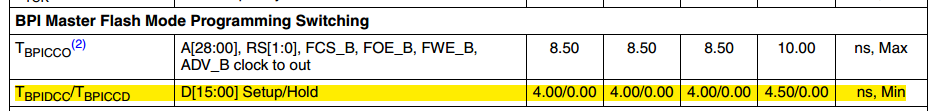

对于JS2800AP30TF型号的flash,Tchqv最大值为17ns;

BPI模式数据建立时间最小值为4ns(FPGA速度等级为-2);

3260

3260

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?