#C0307

沧海茫茫千钟粟,且拾吾昧一微尘

——《沧海拾昧集》@CuPhoenix

【阅前敬告】

沧海拾昧集仅做个人学习笔记之用,所述内容不专业不严谨不成体系

如有问题定为本集记录有谬,切勿深究

目录

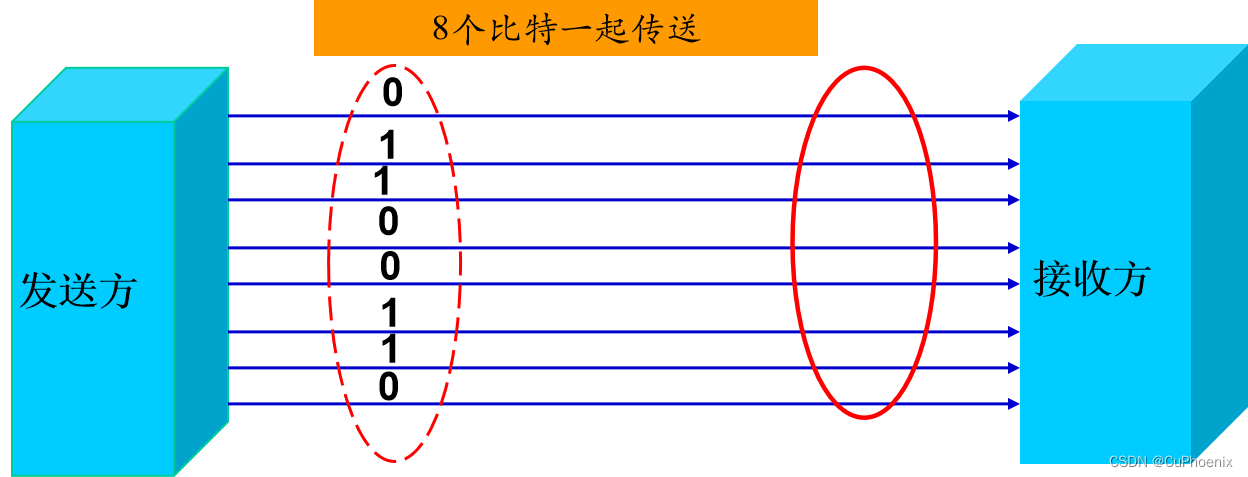

引子:并行通信

并行通信就是把一个字符的各数位用几条线同时进行传输,并行通信的信息传输速度快,信息率高。用于数据传输要求较高,距离较短的场合。

- 同步传输:CPU用一个时序信号来管理接口和设备的动作;

- 异步传输:CPU和接口设备之间只用应答信号联系;

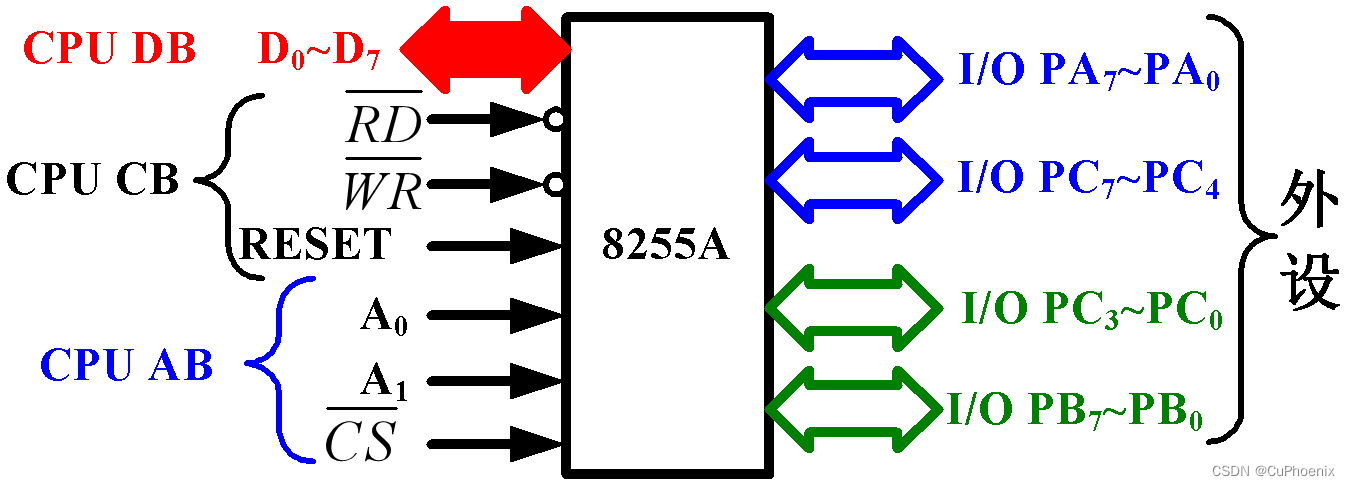

一、并行接口芯片Intel 8255A

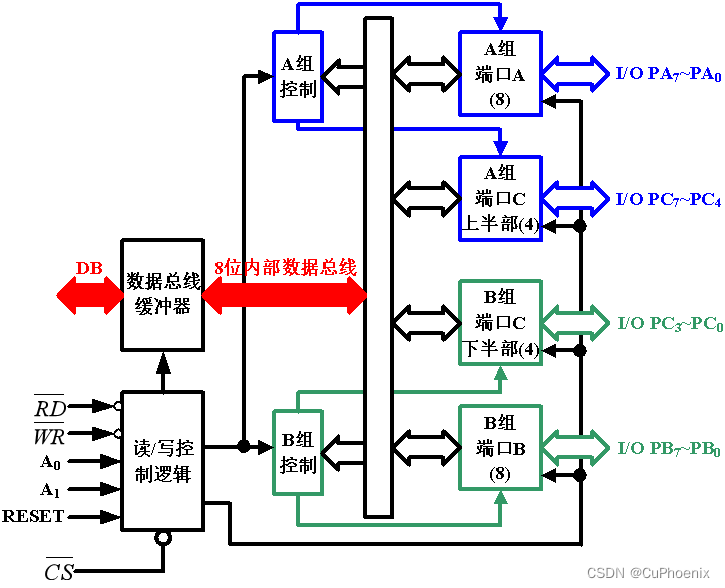

1、8255A的内部结构

- 端口A:8位,数据输入输出锁存;

- 端口B:8位,数据输入缓冲、输出锁存;

- 端口C:8位,数据输入缓冲、输出锁存;端口C也可分成2个4位端口,也可作为端口A和端口B的输入输出控制线和状态信号线,与端口A、端口B配合使用;

- A组控制和B组控制:接受CPU对控制端口的控制字,设置8255A中三个端口的工作方式;

- 读写控制逻辑电路:接受CPU发送的读写信号,其中A0、A1寻址8255A内部寄存器,共有三个数据端口,一个控制端口;

- 数据总线缓冲器:双向三态8bit数据缓冲器,与CPU的数据总线相连,同时与8255A的内部数据总线相连,接受从CPU发出的控制字, 输入输出数据, 向CPU传输8255A的状态字;

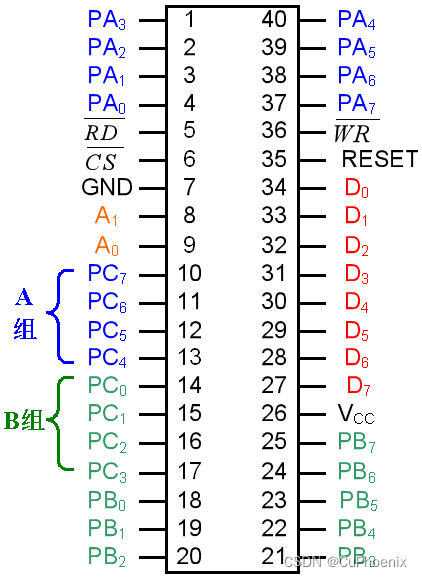

2、8255A的引脚

- PA7~PA0,PB7~PB0,PC7~PC0:端口A,B,C的引脚,用于与外设相连的并行扩展口。

- D7~D0:数据线,用于与CPU的数据总线相连,传输8255A的命令字或I/O数据。

- A1、A0:地址引脚,用于内部端口地址的选择,信号的组合决定了对哪一个端口进行操作。

- RESET:复位信号输入,高有效, 8255A内部寄存器清零, 3个端口均为输入。

- CS*:片选信号,低电平有效。

- RD*:读信号,低电平有效。

- WR*:写信号,低电平有效。

3、8255A的数据传输与引脚关系

| CS* | RD* | WR* | A1 | A0 | 操作 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 读A口 |

| 0 | 1 | 读B口 | |||

| 1 | 0 | 读C口 | |||

| 1 | 0 | 0 | 0 | 写A口 | |

| 0 | 1 | 写B口 | |||

| 1 | 0 | 写C口 | |||

| 1 | 1 | 写控制口 |

二、Inter 8255A的工作方式

| 方式0 基本输入输出方式 | 方式1 应答式输入输出方式 | 方式2 双向应答式输出输出方式 | |

|---|---|---|---|

| 端口A | 可用 | 可用 | 可用 |

| 端口B | 可用 | 可用 | 不可用 |

| 端口C | 可用 | 不可用,做联络线 | 不可用,做联络线 |

1、方式0:基本输入输出方式

- 控制方式:程序方式,是一种简单的输入 / 输出方式;

- 作无条件传输接口电路:由CPU用简单的I/O指令对三个端口进行读/写;

- 作查询式接口电路:可用任一(或多)位端口充当查询信号(但通常都是选用C口承担),由CPU用简单的I/O指令对三个端口进行读/写;

2、方式1:选通输入输出方式

- 控制方式:查询方式 / 中断方式;

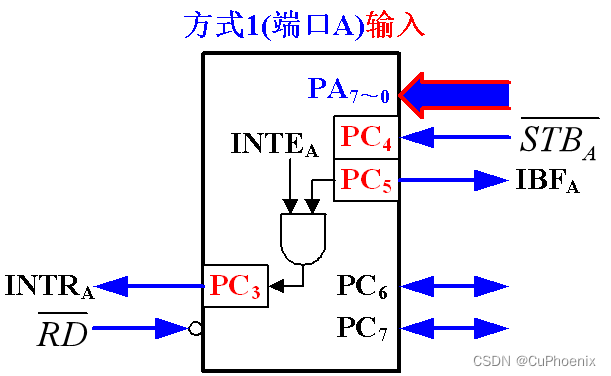

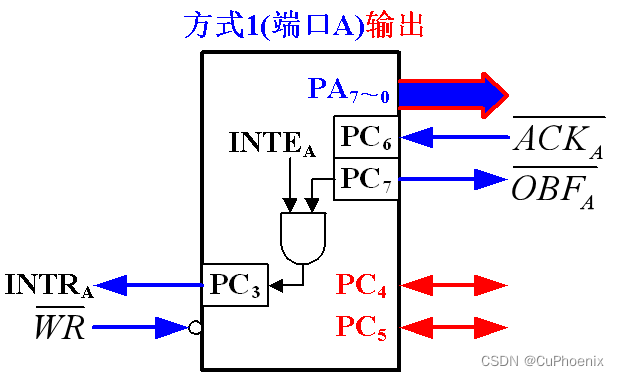

- A口 / B口工作在方式1时,C口各位做联络应答信号线,有固定的定义与时序(自动进行,不可改变);

- 在输入输出操作中,产生固定格式的状态字,供CPU查询或向CPU申请中断。CPU从端口C中读取状态字;

- 单向传送,初始化后只能向一个方向上传送,反方向传送必须再次初始化;

- 方式1时的状态字(通过C口查询):

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

|---|---|---|---|---|---|---|---|---|

| 输入 | I/O | I/O | IBF_A | INTE_A | INTR_A | INTE_B | IBF_B | INTR_B |

| 输出 | OBF_A | INTE_A | I/O | I/O | INTR_A | INTE_B | OBF_B | INTR_B |

注:输入PC4、输出PC6在物理上的连接是STB*信号,但通过软件方式设置/查询INTE信号。

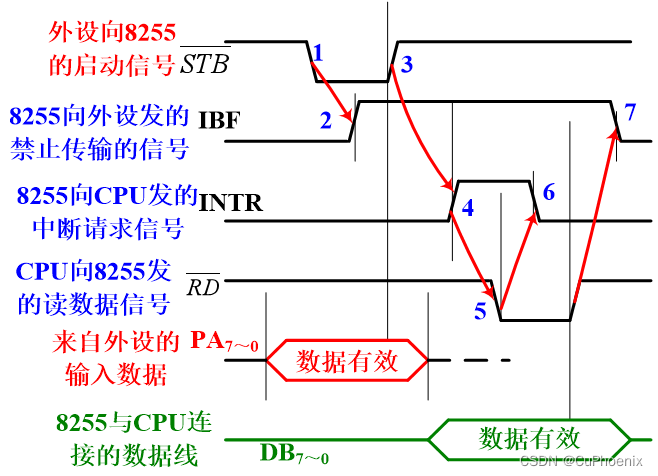

3、方式1:输入过程

| STB* | 输入,选通信号(启动信号),与外设数据同时送入。 |

|---|---|

| IBF | 输出,输入缓冲器满,由8255发往外设。 高,表示8255收到数据但未被CPU取走,通知外设不可再送数据; 低,表示CPU已取走数据,允许外设送新的数据。 |

| INTR | 输出,中断请求。用于8255向CPU申请中断,请求CPU接收数据。 |

| INTE | 中断允许信号,置1允许中断,置0屏蔽中断。 |

- 数据与STB*由外设进入8255,STB*为低,通知8255接受数据。

- 8255收到STB*信号,将IBF置为1,通知外设禁止再送入数据,同时接受数据。

- STB*信号是由外设发出,一般有效500ns,然后自动回高。

- 具备3个条件:STB*为高,IBF*为高,INTE*为高,8255向CPU发中断申请信号,通知CPU取走数据。(即数据已由外设打进8255,且8255接收到,并允许中断)

- CPU接到中断申请后,响应中断,向8255相应端口发读信号。

- 读信号的下降沿复位中断申请。

- 上升沿复位8255向外设发的IBF信号,外设得以向8255发送下一数据。

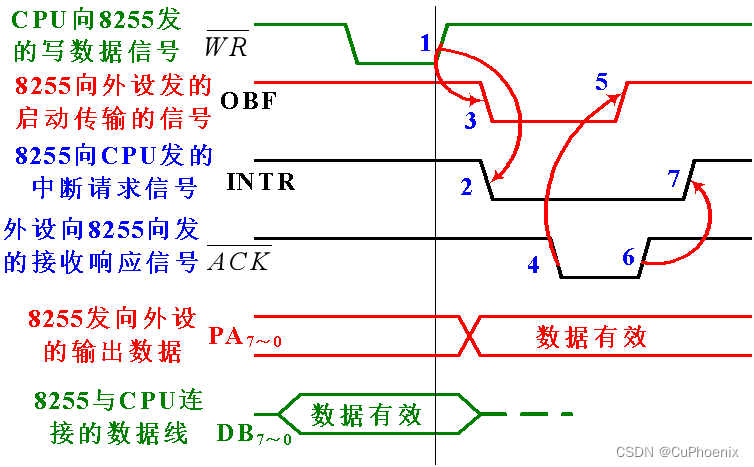

4、方式1:输出过程

| ACK* | 输入,应答信号,外设送入8255,持续一段时间后由外设撤销。 有效时表示外设已取走数据 |

|---|---|

| OBF* | 输出缓冲器满,8255A接到CPU送来的数据后,将数据和OBF*同时送往外设 相当于启动信号,通知外设开始接收数据 |

| INTR | 输出,中断请求,用于8255向CPU申请中断,请求CPU发送数据 |

| INTE | 中断允许信号,置1允许中断,置0屏蔽中断。 |

- CPU在INTR为高的情况下WR*信号有效,通过DB向8255写入数据;

- WR*信号的上升沿使INTR为低,禁止CPU继续向8255发送数据;

- WR*信号的上升沿使OBF信号有效,通知外设取走8255端口的数据;同时,CPU输入的数据也出现在8255相应的端口上;

- 外设取走数据,向8255发送应答信号ACK*

- ACK*下降沿复位OBF,上升沿复位INTR,使中断申请信号有效,8255得以继续向CPU申请中断,输出下一个数据。

5、方式2:双向应答式输入输出方式

- 控制方式:查询方式 / 中断方式;

- A口工作在方式2时,C口高5位做联络应答信号线(实质是方式1的组合),有固定的定义与时序(自动进行,不可改变);

- 在输入输出操作中,产生固定格式的状态字,供CPU查询或向CPU申请中断。CPU从端口C中读取状态字;

- 方式2时的状态字(通过C口查询):

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

|---|---|---|---|---|---|---|---|---|

| 方式2 | OBF_A | INTE_1 | IBF_A | INTE_2 | INTR_A | × | × | × |

注:两个中断允许位INTE1和INTE2要分别设置。在中服中要查询OBF和IBF两位,看是哪个操作在申请中断。

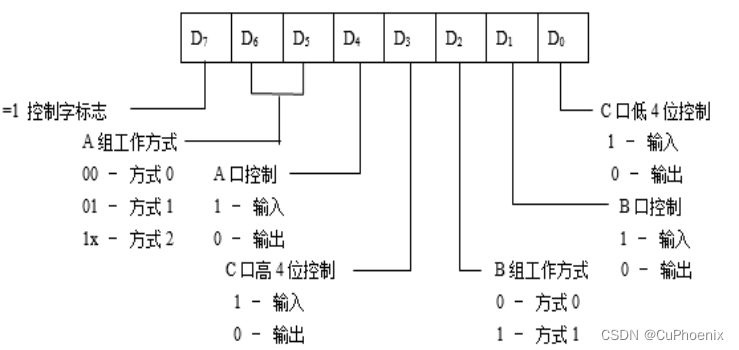

三、Inter 8255A的初始化

1、端口工作方式控制字

2、C端口置位/复位控制字

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D1 |

|---|---|---|---|---|---|---|---|

| 0 | × | × | × | PC0 ~ PC7 位选择 | 置位 / 复位 | ||

敬谢诸君。

金陵钟山之阳。

6531

6531

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?