目录

1. 简介

针对《Vitis HLS 学习笔记--理解串流Stream(2)-CSDN博客》博文的内容,做进一步说明。

2. 综合报告的差别

2.1 包含 do-while

+ Performance & Resource Estimates:

PS: '+' for module; 'o' for loop; '*' for dataflow

+--------------------+------+------+---------+--------+----------+---------+------+----------+------+----+---------+----------+-----+

| Modules | Issue| | Latency | Latency| Iteration| | Trip | | | | | | |

| & Loops | Type | Slack| (cycles)| (ns) | Latency | Interval| Count| Pipelined| BRAM | DSP| FF | LUT | URAM|

+--------------------+------+------+---------+--------+----------+---------+------+----------+------+----+---------+----------+-----+

|+ example | -| 6.45| -| -| -| -| -| no| -| -| 4 (~0%)| 92 (~0%)| -|

| o VITIS_LOOP_15_1 | -| 7.30| -| -| 2| 1| -| yes| -| -| -| -| -|

+--------------------+------+------+---------+--------+----------+---------+------+----------+------+----+---------+----------+-----+

================================================================

== HW Interfaces

================================================================

* AXIS

+-----------+---------------+-------+-------+-------+--------+-------+--------+

| Interface | Register Mode | TDATA | TKEEP | TLAST | TREADY | TSTRB | TVALID |

+-----------+---------------+-------+-------+-------+--------+-------+--------+

| A | both | 32 | 4 | 1 | 1 | 4 | 1 |

| B | both | 32 | 4 | 1 | 1 | 4 | 1 |

+-----------+---------------+-------+-------+-------+--------+-------+--------+

* TOP LEVEL CONTROL

+-----------+------------+-----------------------------------+

| Interface | Type | Ports |

+-----------+------------+-----------------------------------+

| ap_clk | clock | ap_clk |

| ap_rst_n | reset | ap_rst_n |

| ap_ctrl | ap_ctrl_hs | ap_done ap_idle ap_ready ap_start |

+-----------+------------+-----------------------------------+

================================================================

== SW I/O Information

================================================================

* Top Function Arguments

+----------+-----------+-----------------------------------------------------+

| Argument | Direction | Datatype |

+----------+-----------+-----------------------------------------------------+

| A | in | stream<hls::axis<std::complex<short>, 0, 0, 0>, 0>& |

| B | out | stream<hls::axis<std::complex<short>, 0, 0, 0>, 0>& |

+----------+-----------+-----------------------------------------------------+

* SW-to-HW Mapping

+----------+--------------+-----------+

| Argument | HW Interface | HW Type |

+----------+--------------+-----------+

| A | A | interface |

| B | B | interface |

+----------+--------------+-----------+2.2 不包含 do-while

+ Performance & Resource Estimates:

PS: '+' for module; 'o' for loop; '*' for dataflow

+-----------+------+------+---------+--------+----------+---------+------+----------+------+----+---------+----------+-----+

| Modules | Issue| | Latency | Latency| Iteration| | Trip | | | | | | |

| & Loops | Type | Slack| (cycles)| (ns) | Latency | Interval| Count| Pipelined| BRAM | DSP| FF | LUT | URAM|

+-----------+------+------+---------+--------+----------+---------+------+----------+------+----+---------+----------+-----+

|+ example | -| 6.45| 1| 10.000| -| 2| -| no| -| -| 2 (~0%)| 82 (~0%)| -|

+-----------+------+------+---------+--------+----------+---------+------+----------+------+----+---------+----------+-----+

================================================================

== HW Interfaces

================================================================

* AXIS

+-----------+---------------+-------+-------+-------+--------+-------+--------+

| Interface | Register Mode | TDATA | TKEEP | TLAST | TREADY | TSTRB | TVALID |

+-----------+---------------+-------+-------+-------+--------+-------+--------+

| A | both | 32 | 4 | 1 | 1 | 4 | 1 |

| B | both | 32 | 4 | 1 | 1 | 4 | 1 |

+-----------+---------------+-------+-------+-------+--------+-------+--------+

* TOP LEVEL CONTROL

+-----------+------------+-----------------------------------+

| Interface | Type | Ports |

+-----------+------------+-----------------------------------+

| ap_clk | clock | ap_clk |

| ap_rst_n | reset | ap_rst_n |

| ap_ctrl | ap_ctrl_hs | ap_done ap_idle ap_ready ap_start |

+-----------+------------+-----------------------------------+

================================================================

== SW I/O Information

================================================================

* Top Function Arguments

+----------+-----------+-----------------------------------------------------+

| Argument | Direction | Datatype |

+----------+-----------+-----------------------------------------------------+

| A | in | stream<hls::axis<std::complex<short>, 0, 0, 0>, 0>& |

| B | out | stream<hls::axis<std::complex<short>, 0, 0, 0>, 0>& |

+----------+-----------+-----------------------------------------------------+

* SW-to-HW Mapping

+----------+--------------+-----------+

| Argument | HW Interface | HW Type |

+----------+--------------+-----------+

| A | A | interface |

| B | B | interface |

+----------+--------------+-----------+2.3 报告差异分析

仔细分析报告,这两段Vitis HLS综合报告中,主要的差异在于Performance & Resource Estimates部分。

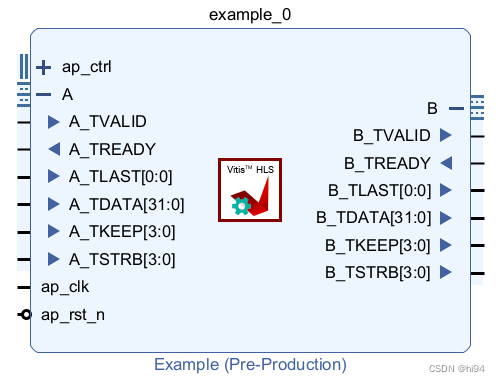

代码综合后的最后 IP 接口也是一致的,如下图所示:

- Latency (cycles),在综合报告1中,模块example和循环VITIS_LOOP_15_1的延迟(Latency)是未指定的(-),而在综合报告2中,模块example的延迟被明确为1个周期。

- Iteration Interval,综合报告2中,模块example的迭代间隔(Iteration Interval)为2,这意味着每两个周期可以开始一个新的迭代。综合报告1中没有提供这一信息。

Resource Estimates:

Flip-Flops (FF): 综合报告1中,模块example使用了4个FF,占总量的约0%,而综合报告2中使用了2个FF。

Look-Up Tables (LUT): 综合报告1中,模块example使用了92个LUT,而综合报告2中使用了82个LUT。

其他部分,如HW Interfaces和SW I/O Information,在两个报告中保持一致。

所以两者差异的本质,只是控制逻辑的细微差异,导致资源用量的稍许差异,而模块本身的功能则完全一致。

这里的分析支持博文《Vitis HLS 学习笔记--理解串流Stream(2)-CSDN博客》的结论。

3. 总结

综合报告1和综合报告2展示了相同代码在Vitis HLS中的综合结果。它们的差异主要集中在性能和资源估计方面,两个报告显示了轻微的差异,例如使用的Flip-Flops和Look-Up Tables数量略有不同。这些差异主要是由控制逻辑微小的差异所导致,而模块功能本身并未变化。总体而言,这些分析结果支持了《Vitis HLS 学习笔记--理解串流Stream(2)-CSDN博客》中的结论。

1654

1654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?