1. GIC简介

操作系统中,中断是很重要的组成部分。有了中断系统才可以不用一直轮询(polling)是否有事件发生,系统效率才得以提高。一般在系统中,中断控制分为三个部分:模块、中断控制器和处理器。其中模块通常由寄存器控制是否使能中断和中断触发条件等;中断控制器可以管理中断的优先级等,而处理器则由寄存器设置用来响应中断。

1.1 GIC结构

作为 ARM 系统中通用中断控制器的是 GIC(Generic Interrupt Controller),目前有四个版本,V1~V4(V2最多支持8个ARM core,V3/V4支持更多的ARM core,主要用于ARM64系统结构)。本文主要描述的是GIC-400,它更适合嵌入式系统,符合v2版本的GIC architecture specification。GIC-400通过AMBA(Advanced Microcontroller Bus Architecture)片上总线连接到一个或者多个ARM处理器上。

图 1.1 GIC中断控制器全局图

从图 1.1中可以看出, GIC 是联系外设中断和 CPU 的桥梁,也是各 CPU 之间中断互联的通道(也带有管理功能),它负责检测、管理、分发中断,可以做到:

1、使能或禁止中断;

2、把中断分组到Group0还是Group1(Group0作为安全模式使用连接FIQ ,Group1 作为非安全模式使用,连接IRQ );

3、多核系统中将中断分配到不同处理器上;

4、设置电平触发还是边沿触发方式(不等于外设的触发方式);

5、虚拟化扩展。

ARM CPU 对外的连接只有2 个中断: IRQ和FIQ ,相对应的处理模式分别是一般中断(IRQ )处理模式和快速中断(FIQ )处理模式。所以GIC 最后要把中断汇集成2 条线,与CPU 对接。

从图 1.2可以看出, GIC 可以清晰的划分成两个部分:分发器( Distributor )和 CPU 接口(CPU Interface )。

图 1.2 GIC中断控制器结构

其中各个子中断使能,设置触发方式,优先级排序,分发到哪个 CPU 上这些功能由分发器负责;总的中断的使能,状态的维护由接口负责。

1.1.1 分发器功能

分发器的主要的作用是检测各个中断源的状态,控制各个中断源的行为,分发各个中断源产生的中断事件到指定的一个或者多个CPU接口上。虽然分发器可以管理多个中断源,但是它总是把优先级最高的那个中断请求送往CPU接口。分发器对中断的控制包括:

(a)中断使能或禁能控制。分发器对中断的控制分成两个级别,一个是全局中断的控制(GIC_DIST_CTRL),一旦禁能了全局的中断,那么任何的中断源产生的中断事件都不会被传递到CPU接口;另外一个级别是对针对各个中断源进行控制(GIC_DIST_ENABLE_CLEAR),禁能某一个中断源会导致该中断事件不会分发到CPU接口,但不影响其他中断源产生中断事件的分发。

(b)控制将当前优先级最高的中断事件分发到一个或者一组CPU接口。

(c)优先级控制。

(d)中断属性设定,例如是电平触发还是边沿触发。

(e)中断的设定。

分发器可以管理若干个中断源,这些中断源用ID来标识,我们称之interrupt ID。

1.1.2 CPU接口功能

CPU接口主要用于和CPU进行接口。主要功能包括:

(a)使能或者禁能CPU接口向连接的CPU提交中断事件。对于ARM,CPU接口和CPU之间的中断信号线是nIRQCPU和nFIQCPU。如果禁能了中断,那么即便是分发器分发了一个中断事件到CPU接口,但是也不会提交指定的nIRQ或者nFIQ通知CPU。

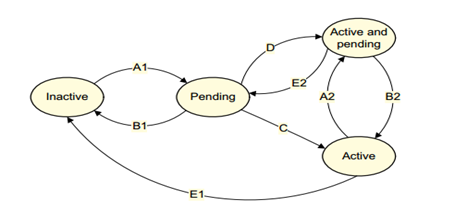

(b)ackowledging中断。CPU会向CPU接口应答中断,中断一旦被应答,分发器就会把该中断的状态从pending状态修改成active,如果没有后续pending的中断,那么CPU 接口就会deassert nIRQCPU和nFIQCPU信号线。如果在这个过程中又产生了新的中断,那么分发器就会把该中断的状态从pending状态修改成pending and active。此时,CPU接口仍然会保持nIRQ或者nFIQ信号的asserted状态,也就是向CPU通知下一个中断。

(c)中断处理完毕的通知。当中断处理器处理完了一个中断的时候,会向写CPU 接口的寄存器从而通知GIC已经处理完该中断。做这个动作一方面是通知分发器将中断状态修改为deactive,另外一方面,可以允许其他的pending的中断向CPU接口提交。

(d)设定优先级掩码。通过优先级掩码可以mask掉一些优先级比较低的中断,这些中断不会通知到CPU。

(e)设定中断抢占的策略。

(f)在多个中断事件同时到来的时候,选择一个优先级最高的通知CPU。

1.3 中断处理流程

中断的处理流程是:分发器把收集来的中断先缓存,依次把优先级最高的中断请求送往CPU接口,CPU读取一个中断,其实就是读取接口的一个寄存器,只不过这个寄存器存放的是中断号,此时中断的状态由pending转为active,CPU处理完了以后,将中断号写入GIC的接口,告诉GIC处理完了,可以将这个中断清理,如图 1.3。

图 1.3 GIC中断处理流程图

1.4 GIC中断类型

GIC 中断类型有3种:SGI(Software-generated interrupt)、PPI(Private peripheral interrupt )、SPI(Shared peripheral interrupt)。

SGI: SGI为软件可以触发的中断,统一编号为0~15,用于各个core之间的通信。

PPI: PPI为每个 core 的私有外设中断,统一编号为 16-31 。例如每个 CPU 的 local timer 即 Arch Timer 产生的中断就是通过 PPI 发送给 CPU 的(安全为29,非安全为30)。

SPI: SPI 是系统的外设产生的中断,为各个 core 公用的中断,统一编号为 32~1019 ,如 global timer 、uart 、gpio 产生的中断。

2. 参考文档

文档类:

1.gic_architecture_specification.pdf

2.DDI0471B_gic400_r0p1_trm.pdf

3.IHI 0048B, ARM Generic Interrupt Controller Architecture Specification, Ver 2.0.pdf

网址链接:

1.http://www.wowotech.NET/linux_kenrel/gic_driver.html

2.http://blog.csdn.Net/velanjun/article/details/8757862

3.http://www.ibm.com/developerworks/cn/linux/l-cn-linuxkernelint/index.html

9406

9406

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?