在verilog表达式中可以指定几种类型的操作数。最简单的类型是以完整位宽形式引用网络、变量或参数,即只给出net、variable或parameter名称。在这种情况下,构成net、variable或parameter的所有bit都将用作操作数。

如果需要矢量net、矢量reg、integer、time变量或parameter的单个bit,则应使用位选操作数。在矢量net、矢量reg、integer或time变量或parameter中,应使用部分选择操作数来引用一组相邻bit。

数组元素、数组元素的位选择或部分选择可以作为操作数引用。操作数的连接(包括嵌套连接)也可以指定为操作数,函数调用可以作为操作数。

1,矢量位选(bit-select)和部分选择(part-select)寻址

位选从矢量net、矢量 Reg、integer或time变量或parameter中提取特定bit,bit可以通过表达式寻址。如果位选择超出地址范围,或者位选择为 x 或 z,那么引用返回的值应为 x。标量、real或realtime类型的变量或参数的位选择或部分选择为非法。

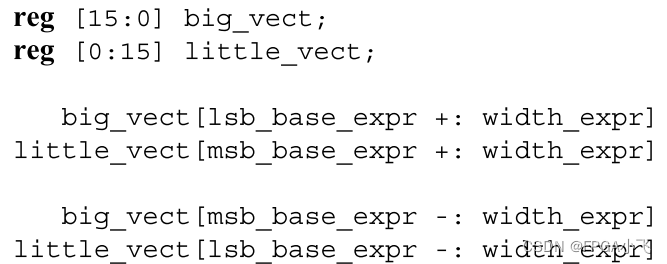

矢量net、矢量 reg、integer或time变量或parameter中的几个连续bit可被寻址,称为部分选择。有两种类型的部分选择模式:常量部分选择和索引部分选择。矢量 reg 或net的常量部分选择用以下语法给出:

![]()

msb_expr 和 lsb_expr 都必须是常整数表达式,且第一个表达式必须寻址比第二个表达式更高的有效位。矢量net、矢量 reg、integer或time变量或parameter中的索引部分选择用以下语法给出:

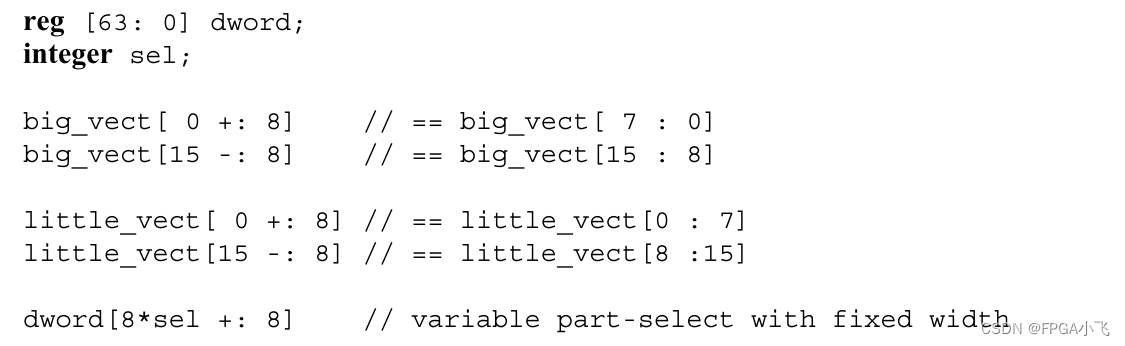

msb_base_expr 和 lsb_base_expr 应为整数表达式,width_expr 应为正整数表达式。lsb_base_expr 和 msb_base_expr 可以在运行时改变。前两个示例从基数开始按升序依次选择比特。选择的位数等于宽度表达式。后两个示例从基数开始按降序依次选择比特。

如果任何类型的部分选择所寻址的bit范围超出了矢量net、矢量 reg、integer或time变量或parameter中的地址范围,或者部分选择为 x 或 z时,则读取时将产生 x 值,但写入时对存储的数据没有影响。部分超出范围的部分选择在读取时,超出范围的位将返回 x,而在写入时,只影响在bit范围内的位。

下面博主小飞举几个例子说明其规则:

![]()

下面的示例指定了操作数索引寻址的acc 向量的单个bit:

![]()

地址访问的实际位在某种程度上由 acc 的声明决定。例如,下一个示例中的每一个 acc 声明都会导致 index 的特定值访问不同的位:

![]()

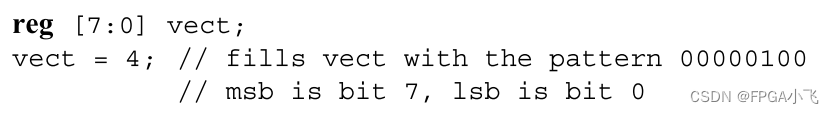

下面的示例及其后说明了位寻址的原理。代码声明了一个名为 vect 的 8 位 reg,并将其初始化为值 4:

- 如果 addr 的值是 2,则 vect[addr] 返回 1。

- 如果 addr 的值超出范围,则 vect[addr] 返回 x。

- 如果 addr 为 0、1 或 3 至 7,则 vect[addr] 返回 0。

- vect[3:0] 返回 0100 位。

- vect[5:1] 返回 00010 位。

- vect[x] 返回 x。

- vect[z] 返回 x。

- 如果 addr 的任何位为 x 或 z,则 addr 的值为 x。

注意-部分选择索引值为 x 或 z 或超出声明范围的位选或部分选择操作,也可能会被编译软件标记为编译错误。

2,数组(array)和内存(memory)数据类型的寻址

下面这个示例声明了一个包含1024 个 8bit数据的内存(memory)数据类型:

![]()

memory寻址的语法包括memory类型数据的名称和地址表达式,格式如下:

![]()

addr_expr可以是任何整数表达式;因此,可以在一个表达式内间接指定内存。下面这个示例说明了这种操作:

![]()

在本例中,mem_name[3] 的地址是名为 mem_name 的内存数组的第三个数。该值又是内存地址 mem_name[mem_name[3]]的 mem_name 地址索引。

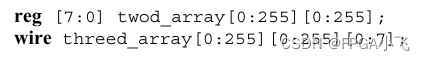

下面这个示例声明了一个 256-by-256 个的八位元素数组和一个 256-by-256-by-8 个的一位元素数组:

访问上述数组的语法应包括memory或array的名称以及每个寻址维数的整数表达式:

![]()

addr_expr 可以是任何整数表达式,数组twod_array访问的是整个8 位矢量,而数组 threed_array 访问的是三维数组的单个位。

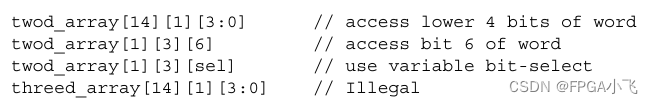

要表示memory或array中某个元素的位选或部分选,应首先通过提供每个维度的地址来选择所需的元素。一旦选定,接下来位选择和部分选择的寻址方式应与net和reg位选择和部分选择的寻址方式相同。例如下面的表示:其中最后一个表示方式就是非法的。

3,字符串(string)表示方法

Verilog HDL 运算符支持字符串的复制、连接和比较操作。复制操作由简单的赋值语句即可实现,连接操作由连接操作符提供,比较操作由等式运算符提供。

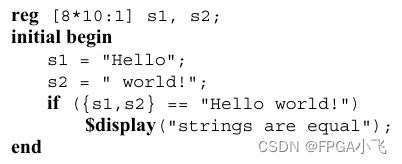

在矢量reg变量中操作字符串时,reg至少应为 8*n 位(n 为 ASCII 字符数),以保留 8 位 ASCII 编码,切记!

4,字符串值填充和潜在问题

将字符串赋值给变量时,应在存储值的左侧填充 0。填充会影响比较和连接操作的结果。比较运算符和连接运算符不应区分填充产生的零和原始字符串字符(0,ASCII NUL)。下面的示例说明了潜在的问题:

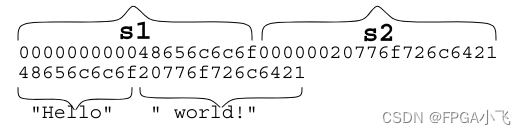

上例中的比较失败是因为在赋值过程中,字符串变量被错误填充了,如下所示:

![]()

s1 和 s2 的连接包括零填充,得到以下值:

![]()

由于字符串 "Hello world!"不包含零填充,因此比较失败,如下所示:

5,处理空字符串(NULL)

空字符串(" ")应被视为等同于 ASCII NUL("\0"),其值为零(0),不同于字符串 "0"。

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

398

398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?