Internal formats in Yosys

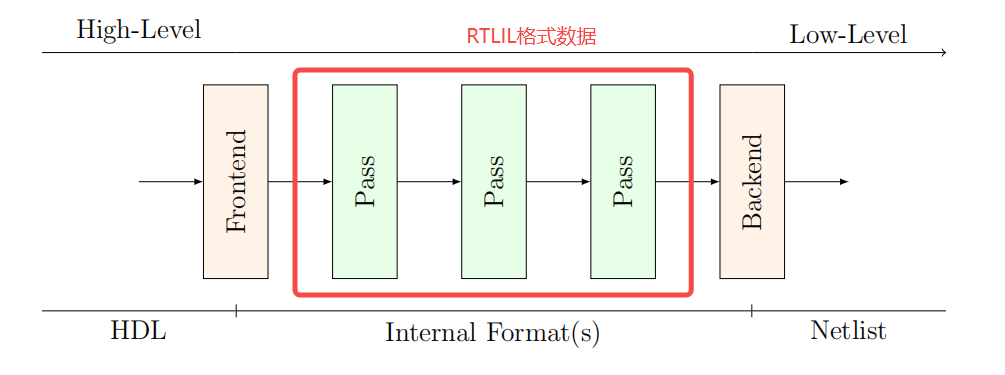

Yosys uses two different internal formats. The first is used to store an abstract syntax tree (AST) of a Verilog input file. This format is simply called AST and is generated by the Verilog Frontend. This data structure is consumed by a subsystem called AST Frontend. This AST Frontend then generates a design in Yosys’ main internal format, the Register-Transfer-Level-Intermediate-Language (RTLIL) representation. It does that by first performing a number of simplifications within the AST representation and then generating RTLIL from the simplified AST data structure.

Yosys使用了两种不同的内部格式。一种是用于存储Verilog输入文件的抽象语法树(AST),简称为AST,由Verilog Frontend生成,由AST Frontend使用。Then AST Frontend 以Yosys内部格式 RTLIL生成一个设计(Design)。AST Frontend先在AST中执行一些简化,然后从AST中生成RTLIL,即第二种内部格式。

The RTLIL representation is used by all passes as input and outputs.

RTLIL Advantages

The passes can be rearranged in a different order and passes can be removed or inserted.

Passes can simply pass-thru the parts of the design they don’t change without the need to convert between formats. In fact Yosys passes output the same data structure they received as input and performs all changes in place.

内部统一数据格式RTLIL具备拓展性;Pass指操作RTLIL数据结构的命令,操作顺序可任意改变;API/数据不需要转换。

RTLIL 表示

The RTLIL representation is basically a netlist representation.

RTLIL表示也是网表的表示,有以下特性。

An internal cell library with fixed-function cells to represent RTL datapath and register cells as well as logical gate-level cells (single-bit gates and registers).

Support for multi-bit values that can use individual bits from wires as well as constant bits to represent coarse-grain netlists.

Support for basic behavioural constructs (if-then-else structures and multi-case switches with a sensitivity list for updating the outputs).

Support for multi-port memories.

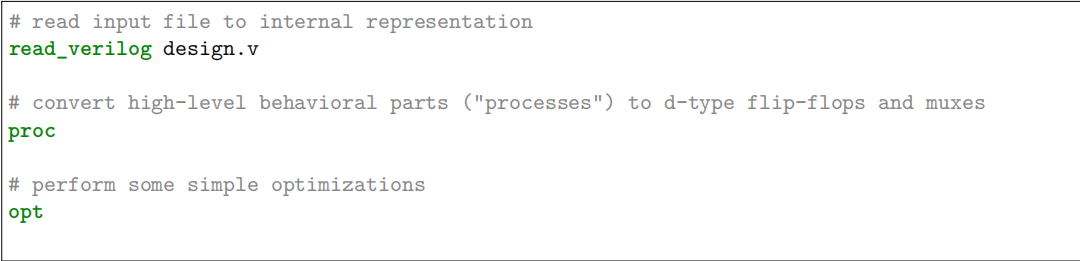

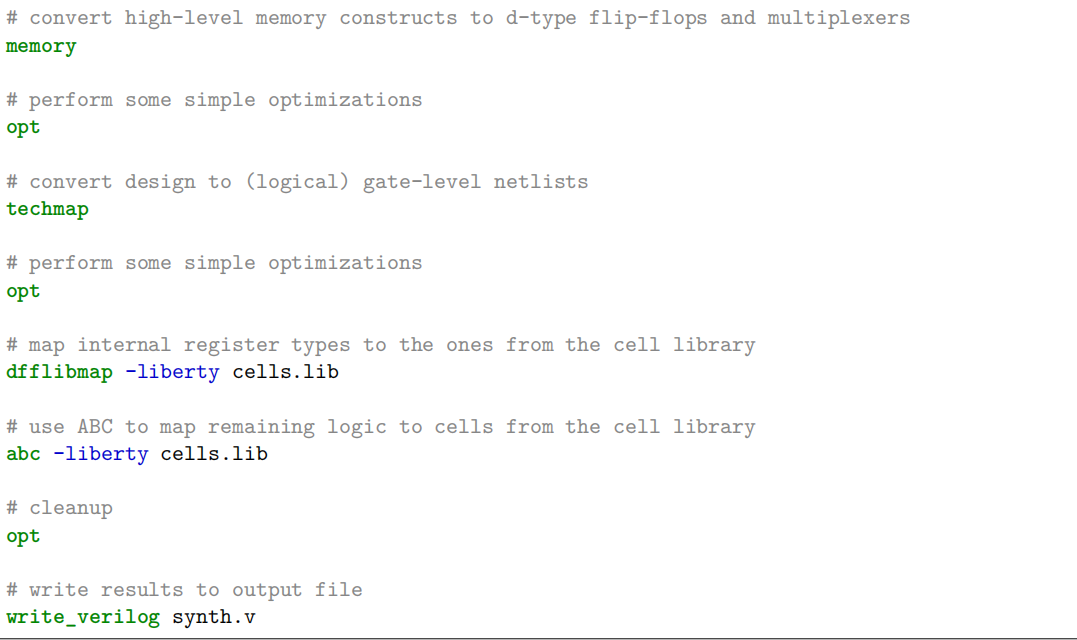

DESIGN .v To Gate-level Netlist synth.v

convert the behavioural Verilog code from the input file design.v to a gate-level netlist synth.v using the cell library described by the Liberty file.

2619

2619

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?