xilinx vivado cameralink图像接收与发送代码,最大支持并行速度100MHz,优于编解码接口芯片。

不利用解码与编码芯片,直接在FPGA内部进行接收解码和发送。

标题:基于Xilinx Vivado的CameraLink图像接收与发送设计

摘要:本文针对CameraLink图像接收与发送的需求,提出了一种基于Xilinx Vivado的解决方案。该方案利用FPGA内部进行图像数据的接收解码和发送,无需额外的解码与编码芯片,实现了最大支持100MHz并行速度的高性能图像传输。本文将详细介绍设计方案的实现思路、硬件架构、以及相应代码的开发过程,并通过详细的技术分析,展示了其在实际应用中的优势与潜力。

第一章 绪论 1.1 研究背景 1.2 研究目的和意义 1.3 研究内容与结构

第二章 CameraLink图像接收与发送的原理与规范 2.1 CameraLink协议概述 2.2 CameraLink接口工作原理 2.3 CameraLink图像传输规范

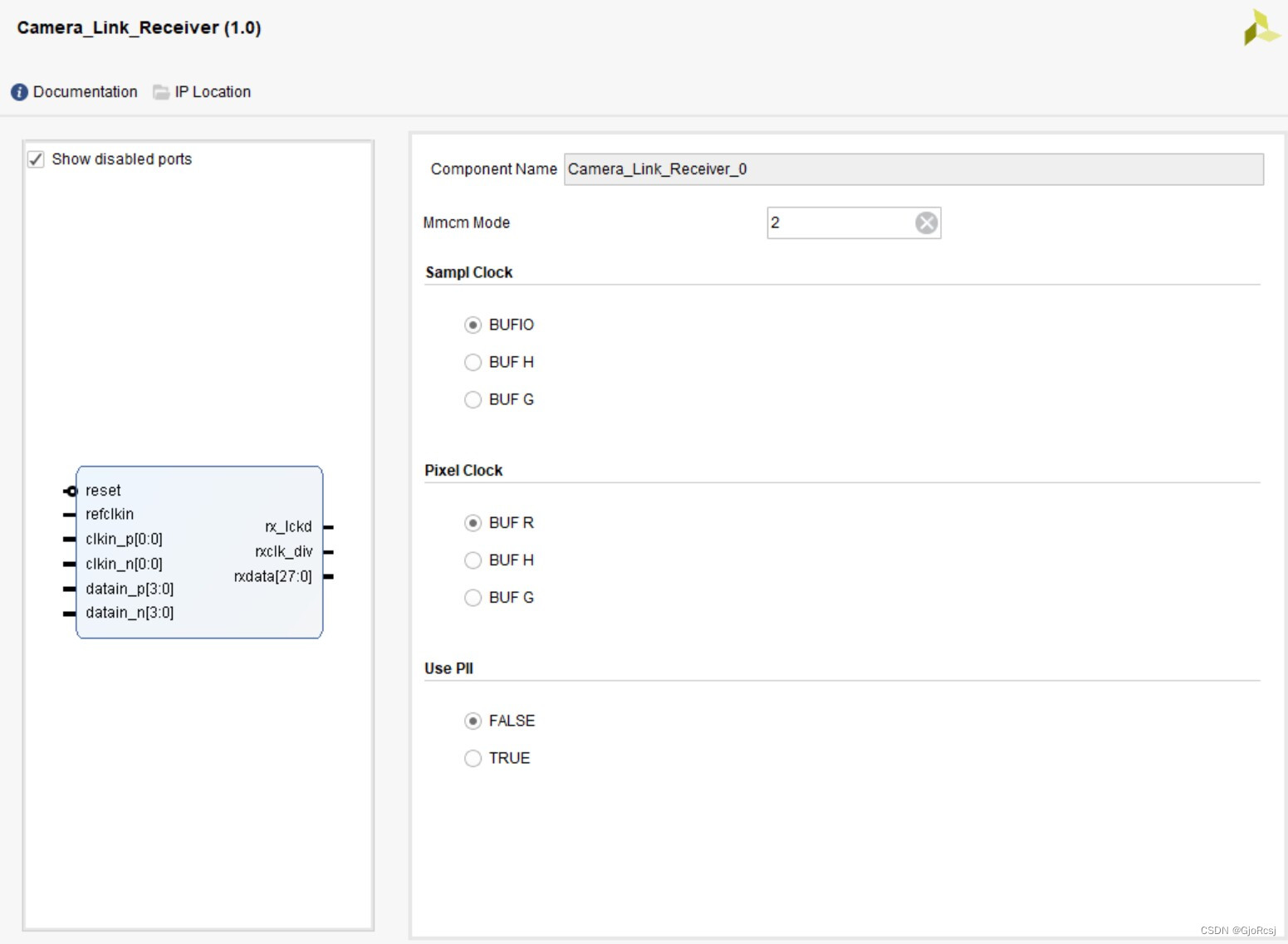

第三章 设计方案及其实现思路 3.1 Xilinx Vivado的特点与优势 3.2 图像接收与发送方案的设计思路 3.3 FPGA内部接收解码与发送的实现原理

第四章 硬件架构设计 4.1 系统整体架构设计 4.2 FPGA内部接收解码模块设计 4.3 FPGA内部发送模块设计

第五章 代码开发与优化 5.1 Vivado开发环境的搭建 5.2 CameraLink图像接收解码代码开发 5.3 CameraLink图像发送代码开发 5.4 代码的性能优化与测试

第六章 系统性能评估与分析 6.1 并行速度与传输稳定性测试 6.2 系统资源占用与功耗分析 6.3 与传统方案的对比分析

第七章 结果与讨论 7.1 图像接收与发送的实际应用情景 7.2 系统性能优势的验证与讨论 7.3 潜在的改进空间与未来发展方向

第八章 结论 8.1 主要研究成果总结 8.2 存在的问题与展望 8.3 结束语

通过对CameraLink图像接收与发送的需求进行全面的分析和研究,在本文中我们提出了一种基于Xilinx Vivado的解决方案。该方案不仅可以在FPGA内部进行接收解码和发送,还实现了最大支持100MHz并行速度的高性能图像传输。通过详细的设计思路、硬件架构、代码开发以及性能评估与分析,本文证明了该方案在实际应用中的优势与潜力。基于该方案,我们可以实现更高速度、更稳定的CameraLink图像传输,为相应应用领域的发展提供了有效的技术支持。

关键词:Xilinx Vivado;CameraLink;图像接收与发送;FPGA内部解码与编码;并行速度

相关代码,程序地址:http://lanzouw.top/649532614127.html

1274

1274

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?