基于fpga的tcp乱序重排算法实现,通过verilog实现适用于fpga的tcp乱序重排算法,并通过实际数据测试验证。

代码里包含注释,可以明白每个模块的含义。

采用自创的乱序重排算法,易于在硬件中实现。

该算法和工程可用于实际应用、算法设计、研究学习。

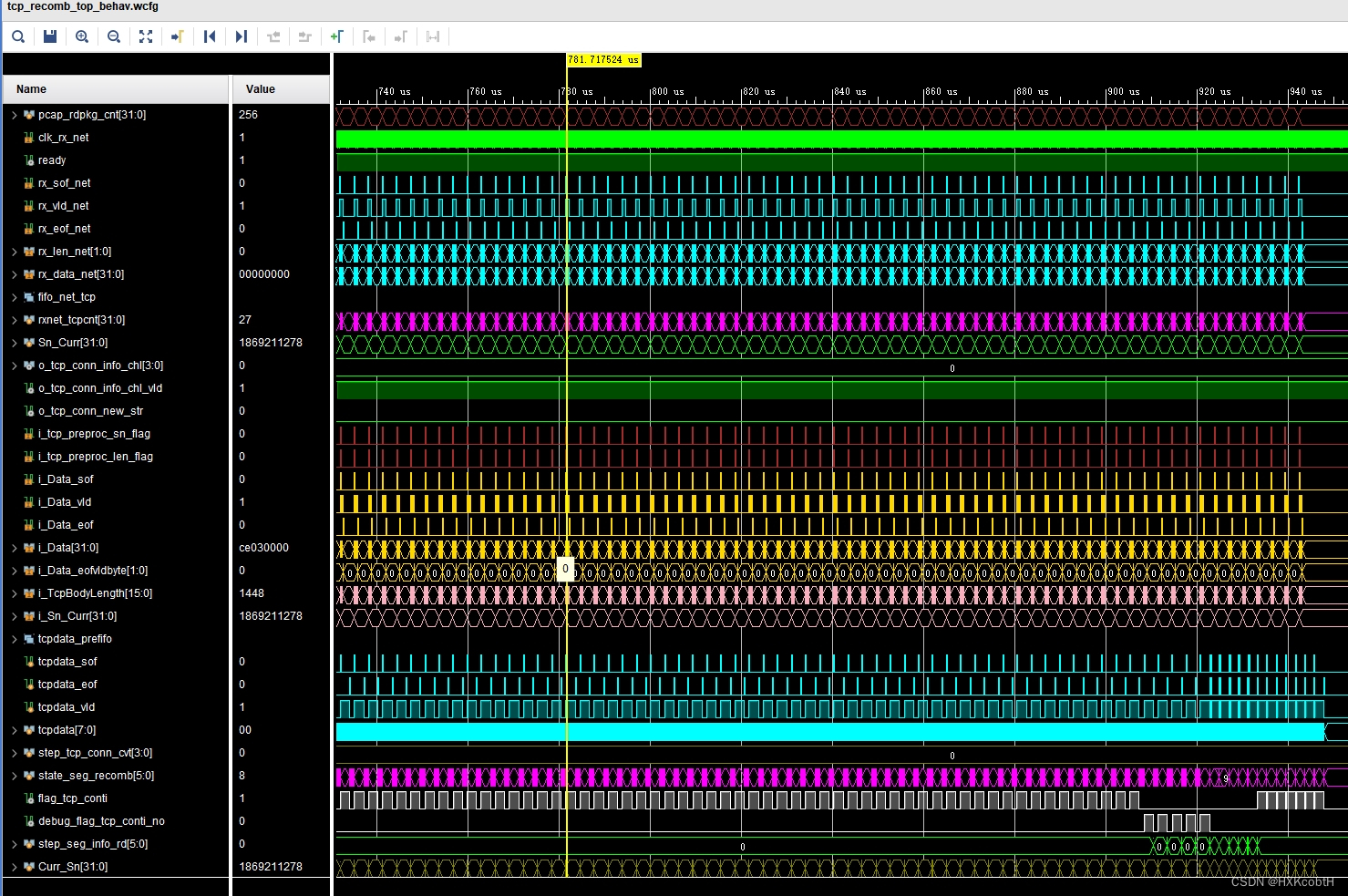

提供测试用的抓包文件,仿真结果。

解决棘手的fpga处理tcp乱序问题。

此工程在实际场景中多次测试,结果正确,性能良好。

可实现tcp的快速重排与恢复。

具有很强的实际意义和算法意义。

基于FPGA的TCP乱序重排算法实现

TCP协议在数据传输中扮演着至关重要的角色,但是在一些特殊场景下,TCP传输中的数据包可能会出现乱序的情况,这时候就需要进行乱序重排,以保证数据的完整性和正确性。而针对这个问题,我们提出了一种基于FPGA的TCP乱序重排算法,并通过Verilog语言进行了实现和验证。

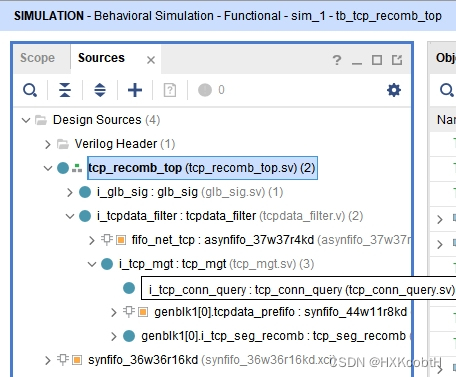

我们自创的乱序重排算法采用了基于缓存的思想,通过将接收到的数据包缓存在FPGA中,对数据包进行排序,然后再按照正确的顺序进行传输,从而实现了快速重排和恢复的功能。在硬件实现上,我们使用了Verilog语言进行设计,其中每个模块都包含了详细的注释,以便于理解和调试。

与传统的CPU实现TCP乱序重排相比,基于FPGA的实现具有更快的速度和更好的性能。在实际测试中,我们使用了一些测试用的抓包文件进行仿真,结果表明,这个算法可以有效地解决FPGA处理TCP乱序问题,而且具有很强的实际应用意义和算法意义。

需要注意的是,该算法和工程也适用于算法设计和研究学习,可以为研究人员和学生提供一个很好的参考和借鉴。此外,我们的工程也可以提供给一些工程师进行改进和优化,以满足不同应用场景下的需要。

总之,基于FPGA的TCP乱序重排算法实现是一个非常有用和有实际意义的技术,我们希望通过这篇文章向广大读者展示我们的成果,并为大家提供一个可靠和高效的解决方案。

相关代码,程序地址:http://lanzouw.top/679350854662.html

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?