目前TCP协议大多由cpu跑代码实现, 这次用FPGA的纯逻辑实现 , System Verilog编写,

下面给大家粗略讲一下我的实现方法,

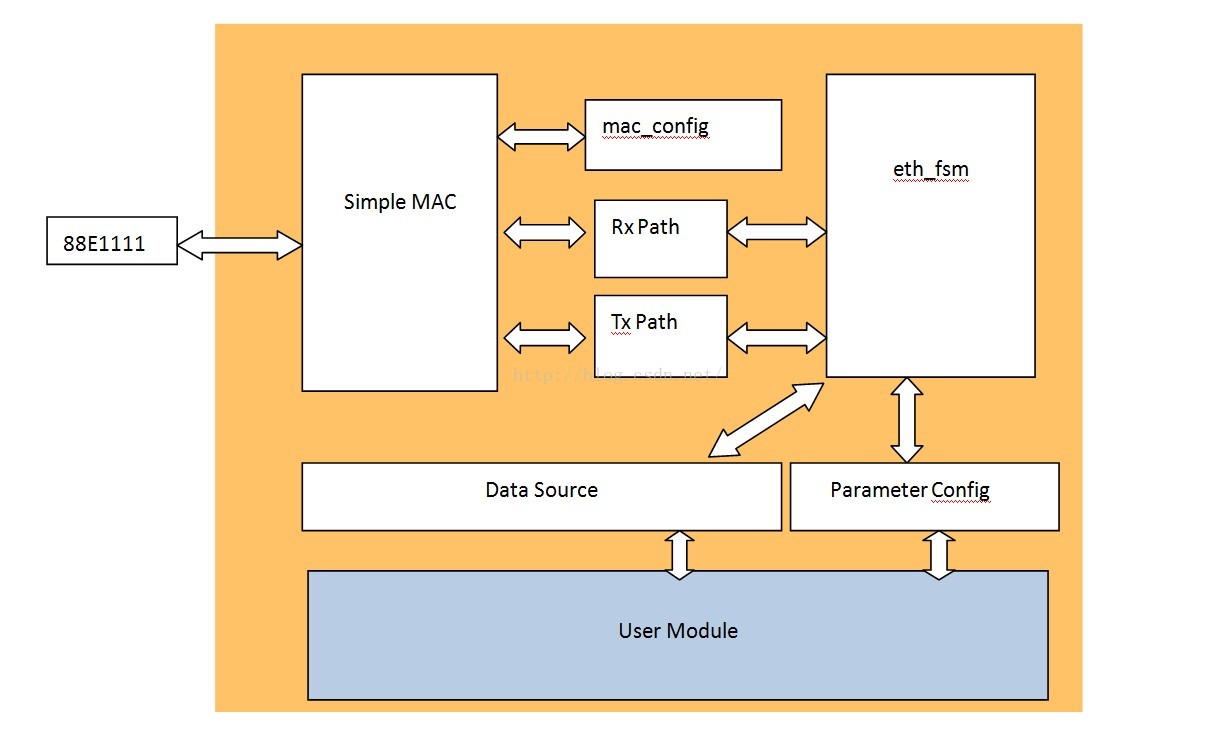

下面是工程的示意图.

这个工程由几部分组成, 外部使用了88e1111千兆以太网phy。FPGA内部有几个大的模块,

顶层模块:

//

tcpip_hw

Description

top module

Author(s):

- bin qiu, qiubin@opencores.org or chat1@126.com

Copyright (C) 2015

//

`include "tcpip_hw_defines.sv"

module tcpip_hw(

input clk,

input rst_n,

output mdc,

inout mdio,

output phy_rst_n,

output is_link_up,

input [7:0] rx_data,

output logic [7:0] tx_data,

input rx_clk,

input rx_data_valid,

output logic gtx_clk,

input tx_clk,

output logic tx_en,

//user interface

input [7:0] wr_data,

input wr_clk,

input wr_en,

output wr_full,

output [7:0] rd_data,

input rd_clk,

input rd_en,

output rd_empty

);

wire clk8;

wire clk50;

wire clk125;

wire clk125out;

wire is_1000m;

logic eth_mode;

always @(posedge clk50)

eth_mode <= is_1000m;

assign gtx_clk = clk125out;

pll pll_inst(

.inclk0(clk),

.c0(clk50),

.c1(clk125out),

.c2(clk8)

);

wire mdio_out;

wire mdio_oe;

wire reset_n;

assign mdio = mdio_oe == 1'b1 ? mdio_out : 1'bz;

rst_ctrl rst_ctrl_inst(

.ext_rst(rst_n),

.rst(reset_n),

.clk(clk50)

);

wire is_100m;

wire is_10m;

wire [7:0] tse_addr;

wire tse_wr;

wire [31:0] tse_wr_data;

wire tse_rd;

wire [31:0] tse_rd_data;

wire tse_busy;

headers_if if_headers_rx(clk50);

headers_if if_headers_tx(clk50);

ff_tx_if if_tx(clk50);

ff_rx_if if_rx(clk50);

frame_type_t rx_type;

frame_type_t tx_type;

logic rx_done;

logic [31:0] data_recv;

logic [15:0] data_recv_len;

logic data_recv_valid;

logic data_recv_start;

logic rx_done_clear;

u32_t cur_ripaddr;

u16_t cur_rport;

u16_t rx_header_checksum;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

472

472

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?