关注、星标公众号,精彩内容每日送达

来源:网络素材本文的目的是在一个神经网络已经通过python或者MATLAB训练好的神经网络模型,将训练好的模型的权重和偏置文件以TXT文件格式导出,然后通过python程序将txt文件转化为coe文件,(coe文件是为了将其写入rom,网络中的权重和偏置通过读取ROM即可,后续需要修改输入其他特征值,只需要修改input的rom里面的coe文件即可)。

设计思想

其中sigmoid函数是本次实验最大的难点,因为sigmoid函数的值是在0-1之间的小数,其值越大,说明该模型的输出是该结果的几率越大。但是verilog硬件描述语言,其计算结果只有0或1两种情况,所以要想直接通过verilog语言计算出sigmoid函数的值是比较复杂的,本次使用的方法为查找表法,通过外部其他语言计算出sigmoid函数的值,然后将其放入查找表,后续当需要使用sigmoid函数时,直接输出结果。但是这个需要不断地往里面加值,每更新一次输入,那么就往sigmoid模块里面的查找表添加上该输入的sigmoid值。

由于FPGA的计算是基于数字逻辑和二进制运算,小数计算只能通过 固定点数(即带有定点小数位的整数表示)来模拟某些浮点数计算。这需要使用额外的逻辑来实现浮点数的运算、舍入和特殊值处理。

但是本文选择一个简便的方法,选择将输入,权重 分别保留两位小数(可自己选择位数,保留越多精度越高,反之精度越低),然后分别将其乘以100,将数据全都变成带符号整数,然后将其进行乘加运算。将偏置保留4位小数并乘以10000,得到的结果除以10000然后进行sigmoid计算,后续无论添加多少层,都可以以此方法来进行计算。以下为搭建神经网络的步骤:

step1: 处理数据,将保存好的权重文件转化为coe文件,然后添加一个ROM,并将coe文件加载进 ROM里面;

module input_rom_ctr(

input sys_clk, //50MHz时钟

input rst_n, //复位,低电平有效

input [5:0] data_deep,

output reg [31:0] rom_data_r , //ROM读出数据

output reg viald,

output reg [6:0] rom_addr_rr //ROM输入地址

);

reg [6:0] rom_addr;

//产生ROM地址读取数据

always @ (posedge sys_clk or negedge rst_n)

begin

if(!rst_n)begin

rom_addr <= 7'd0;

viald <= 1'b1;

end

else if(rom_addr_rr >= (data_deep -1'd1))begin

viald <= 1'b0;

end

else if(rom_addr >= (data_deep - 1'd1))begin

rom_addr <= 7'd0;

end

else begin

rom_addr <= rom_addr+1'b1;

viald <= viald;

end

end

reg [6:0]rom_addr_r;

always @(posedge sys_clk or negedge rst_n) begin

if(!rst_n)begin

rom_addr_r <= 7'd0;

rom_addr_rr <= 7'd0;

end

else begin

rom_addr_r <= rom_addr;

rom_addr_rr <= rom_addr_r;

end

end

wire [31:0] rom_data;

always @(posedge sys_clk or negedge rst_n)begin

if(!rst_n)begin

rom_data_r <= 32'd0;

end

else begin

rom_data_r <= #2 rom_data;

end

end

//实例化ROM

input_rom rom_ip_inst

(

.clka (sys_clk ), //inoput clka

.addra (rom_addr), //input [4:0] addra

.douta (rom_data) //output [7:0] douta

);

endmodule

step2:将ROM里的数据读取出来,如果数据较少就直接使用二维数组保存数据,较多的话可以添 加一个RAM,然后通过调用RAM里面的变量搭建第一层神经网络(暂不添加sigmoid)。

input_rom_ctr input_rom( //取输入层的数据存入ram

.sys_clk (clk), //50MHz时钟

.rst_n (rst_n), //复位,低电平有效

.data_deep(5),

.rom_data_r (rom_data1), //ROM读出数据

.viald (en_wr1),

.rom_addr_rr (input_index)

);

always @(posedge clk)begin

if(en_wr1) begin

input_layer[input_index] <= rom_data1; //从rom里面读出数据,并将其写入ram/寄存器里面,后面的神经网络直接调用寄存器操作

end

else begin

input_data <= input_layer[input_index];//从ram里面读出来的数据,加载地址就得到相应的数据。

end

end

Step3:通过仿真得到第一层神经网络每个神经元的乘加结果,并加上偏置后,通过外部计算得到 sigmoid值后将其添加到sigmoid模块的lut查找模块中,如此反复,最后就可以得到一个神经 网络框架。(sigmoid函数的结果也要乘以100,作为下一层的输入),最后得到的输入层 的每个神经元的结果就代表其识别结果的概率。

module sigmoid (

input wire signed [31:0] input_value, // 输入32位有符号整数

output reg signed [31:0] sigmoid_output // 输出32位有符号整数

);

always @(*) begin //可以看做是一个查找表,将上一层的输入进入sigmoid函数来进行查找值,然后将得到的值乘以100用于保留两位小数,精度要求高的就多乘一点

case (input_value)

-2673 : sigmoid_output = 43; //上一层输入3490,是原本输入乘以100,保留两位小数乘以权重乘以100,即改结果是原本结果的10000倍,所以进sigmoid函数的应该是0.349

17232 : sigmoid_output = 85; //建议以后有更多值后继续添加,查找表越丰满,后续能使用的输入就越多。

36380 : sigmoid_output = 97;

124358 : sigmoid_output = 100;

-47650 : sigmoid_output = 1;

-5781 : sigmoid_output = 36;

3657 : sigmoid_output = 59;

-23082 : sigmoid_output = 9;

///上面是第一层隐层的结果,下面是输出层的结果。

4816 : sigmoid_output = 62;

-3390 : sigmoid_output = 42;

20652 : sigmoid_output = 89;

-4386 : sigmoid_output = 39;

-2004 : sigmoid_output = 45;

-623 : sigmoid_output = 48;

default: sigmoid_output = 0;

endcase

end

endmodule

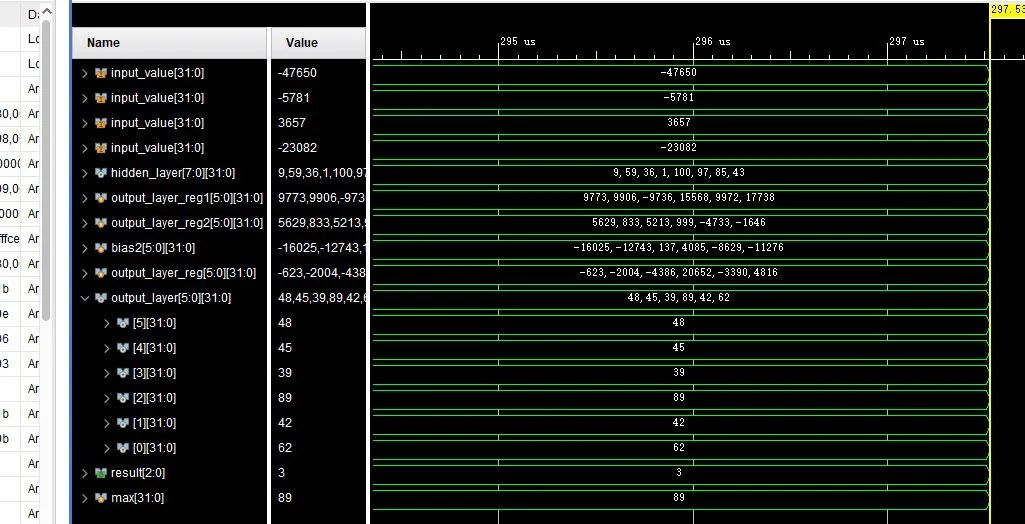

仿真结果

最后的output_layer就是输出的最后结果。

(全文完)

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?