Wafer Map Defect Patterns Classification using Deep Selective Learning 使用深度选择性学习的晶圆图缺陷模式分类

我们建议使用卷积神经网络将晶圆图缺陷分类任务作为一个图像分类问题来解决。

摘要:随着集成电路规模不断扩大,有效的成品率分析变得越来越重要,但也越来越具有挑战性。本文提出了一种基于深度选择性学习的晶圆图缺陷模式分类方法。我们提出的方法具有一个综合拒绝选项,当误分类风险较高时,模型选择避免预测类别标签。因此,在预测覆盖率和误分类风险之间进行权衡。这种选择性学习方案允许新的缺陷类别检测、概念转移检测和资源分配。此外,为了解决晶圆图分类中的类不平衡问题,我们提出了一个基于卷积自动编码器模型的数据增强框架,用于合成样本生成。我们提出的方法的有效性在WM-811k工业数据集上得到了验证,在全覆盖下,该方法的准确率达到了94%,在选择性学习的情况下,该方法的准确率达到了99%,同时成功地检测到了新的缺陷类型。

集成电路(IC)技术的不断扩展以及最先进的设计复杂性的增加,加剧了与设计健壮电路相关的挑战[1]。随着这种规模的扩大,灾难性缺陷和工艺变化成为限制IC设计产品产量的最突出因素[1]。在IC设计周期中,提高成品率的关键第一步是确定导致成品率损失最大的潜在因素,为此,晶圆图分析是关键。传统上,晶圆检查由经验丰富的工程师执行,他们可以根据晶圆缺陷模式确定故障原因。然而,这样的过程很繁琐,需要一种自动化的替代方案[2,3]。文献中提出了不同的方法来解决这一问题。特别是,机器学习技术已经被提议使用无监督和有监督的学习范式来处理这项工作[2-8]。通过无监督学习,可以构建晶圆图簇,然后经验丰富的工程师用缺陷模式标记每个晶圆图[3–5,9]。然而,用这种方法对晶圆进行缺陷标记并不简单,通常需要人类经验。另一方面,监督学习技术依赖于从晶圆图中提取的特征来构建分类模型,该模型能够根据缺陷类型对新的晶圆图进行分类[2,6,7]。上述方法依赖于一组特征来捕捉晶圆的空间特性。然而,这些晶片可以本能地被视为图像,缺陷模式是这些图像的空间特征。因此,通过使用晶圆的自然表示作为图像,可以最好地保留缺陷图案的本机空间特征。

本文提出了一种基于深度选择学习的晶圆图缺陷模式分类框架。除了通过利用晶圆的固有图像表示来实现比传统方法更高的精度外,我们提出的方法还展示了独特的功能,这些功能是为解决任务中的两个挑战而定制的。一个主要的挑战来自这样一个事实,即一些晶圆可能会显示出新的缺陷模式,而这些模式以前在培训期间没有被模型看到。在这种情况下,模型可能会给出错误的标签,从而掩盖新类型的缺陷。此外,一些晶圆图可能会显示一个以上的缺陷图案,这可能会压倒分类模型。为了处理这些情况,我们建议使用带有集成拒绝选项的卷积神经网络[10,11]。换句话说,在培训过程中,如果用户设定了风险和覆盖率之间的折衷方案,则该模型将被训练为同时优化分类和拒绝。有了这个选项,模型可以选择放弃错误分类风险很高的预测;i、 e.该模型对某些样本不进行预测,以保持较低的风险水平。显然,拒绝选项可以进一步提高所选样本上模型的准确性。它还可以用于检测新的缺陷类别和数据分布中的变化。此外,模型中未标注的晶片预计会有所不同,即工程师有兴趣检查这些晶片。因此,该模型可以帮助配置人力资源 。

其次,缺陷类的出现频率不同,这通常会导致训练过程不平衡,其中一些少数类被其他多数类所主导。在这项工作中,我们建议使用数据增强从代表性不足的类生成合成样本。特别是,我们训练卷积自动编码器,从目标类的分布生成样本,并在训练过程中使用合成样本和原始样本[12]。在WM-811k工业晶圆图数据集[13]上进行测试时,与最先进的晶圆图缺陷分类方法相比,该方法具有独特的特点,可以获得更好的结果。我们的主要贡献可以总结如下:•提出了一种利用卷积神经网络进行晶圆图缺陷分类的新方法建议的方法配备了一个集成的拒绝选项,可以利用该选项降低模型的误分类风险选择性学习功能可用于新缺陷检测、数据更改检测和资源分配。

WM 811K工业晶片图数据集(13),其中包含九种不同的晶片图案。这些图案是通过在晶圆上用合格或不合格标记芯片位置来获得的。图1显示了每种**缺陷类型的样本晶圆图:中心缺陷、圆环缺陷、边缘位置缺陷、边缘环缺陷、随机缺陷、位置缺陷、接近满缺陷、划痕缺陷和无缺陷。**如图1所示,晶圆图使用

大小为256×256像素的单通道灰度图像表示,具有3个像素级别:0、127和255。像素级为0的位置(即图1中的黑色像素)是那些不属于晶圆的位置。像素级别为127的灰色像素表示带有合格标签的管芯位置,而白色像素表示带有不合格标签的管芯位置。

目标是训练一个能够将晶片分类为相应缺陷类型的模型。在使用WM-811k工业数据集的作品中,最先进的方法依赖于从晶圆图中提取的一组特征,并结合支持向量机(SVM)分类器2]。在这种方法中,特征提取步骤可能会破坏晶圆图中的一些重要信息。直观地说,晶圆图可以被视为图像,缺陷图案是这些图像的空间特征。因此,在其图像表示中使用晶圆图可以最好地保留缺陷信息。[因此,在这项工作中,我们提出了一个使用深度选择性学习的晶圆图缺陷检测框架,该框架具有卷积神经网络和集成拒绝选项。此外,我们建议使用围绕卷积自动编码器构建的数据增强方案来解决晶圆分类任务中的不平衡问题。

在我们的工作中,**我们为CNN模型配备了一个拒绝选项,当预测失误的风险很高时,该选项允许模型避免对特定样本进行预测[10,11]。该选项提供了风险和覆盖率之间的折衷,其中覆盖率是一种反映模型不放弃预测的概率的度量。换句话说,如果与预测失误相关的成本很高,用户可以选择以降低覆盖率为代价来降低风险。在解决晶圆图缺陷分类问题时,该选项非常方便,因为该模型可以避免在两种不明确的情况下进行预测。第一种情况是晶圆上出现了一个新的缺陷图案,而在培训过程中没有看到,第二种情况是晶圆上出现了一个以上的已知图案。使用拒绝选项的目的是促使模型避免在这两种情况下进行预测,以及任何其他被认为有风险的情况下进行预测。**关于此类模型适用性的更多细节见第IV-D节。选择性模型是一对(f,g),其中f是预测函数,g是选择函数,作为f[10,17]的二进制限定符

数据增强:

在许多分类任务中,类别不平衡是一个关键的挑战,可能会阻碍分类器的性能[19,20],这需要在数据准备期间解决。在晶圆缺陷分类问题中,不同的图案具有不同的发生概率,这导致了不平衡问题,应在预处理阶段加以解决。在这项工作中,我们选择使用数据扩充来解决不平衡问题[19,21]。其关键思想是为代表性不足的类生成合成样本,以扩充原始数据集并减少类不平衡的影响。**第一步是学习表示不足的类的基本分布,以便从学习的分布中抽取新的示例。这可以使用经过训练的自动编码器网络来完成,通过编码-解码方案学习目标类中样本的潜在空间表示[12,22,23]。经过训练后,编码块可以生成原始图像的潜在空间表示,当通过解码块时,期望能够以高精度重新生成原始图像。然而,如果在解码阶段之前将小扰动添加到潜在空间表示中,则可以生成与原始样本接近的新合成样本,并用于扩充数据集。**由于当前问题中的样本是图像,我们建议在数据增强框架中使用卷积自动编码器作为核心引擎。

A 90nm 103.14 TOPS/W Binary-Weight Spiking Neural Network CMOS ASIC for Real-Time Object Classification

一种用于实时目标分类的90nm 103.14tops/W二元权重尖峰神经网络CMOS专用集成电路

本文介绍了一种用于实时图像分类的低功耗90nm CMOS二值加权尖峰神经网络(BW-SNN)专用集成电路。该芯片通过容纳整个5层BW-SNN的脉动阵列最大限度地实现数据重用,数据访问需要最小的片外带宽。该芯片实现了97.57%的实时瓶装饮料识别准确率,每次推理仅消耗0.62uJ。出于比较目的,它实现了98.73%的MNIST手写字符识别准确率,每次推理仅消耗0.59uJ。瓶装饮料的识别速度为300 fps,这对于许多其他实时应用来说已经足够了。在0.6V电压下,峰值效率点为103.14TOPS/W,这比我们已知的其他设计要好。通过标准化为28nm技术节点,与最先进的设计相比,该ASIC的效率提高了5倍,硬件成本降低了7倍。

本文旨在为CNN结构设计一种节能的专用SNN硬件。

INVITED: Computation on Sparse Neural Networks and its Implications for Future Hardware 特邀:稀疏神经网络的计算及其对未来硬件的影响

神经网络模型广泛应用于解决计算机视觉、个性化推荐、自然语言处理等具有挑战性的问题。这些模型计算量非常大,达到了现有服务器和物联网设备的硬件限制。因此,在最大限度地保持精度的同时,以更少的计算量找到更好的模型结构是一个热门的研究课题。在各种旨在降低计算复杂度的机制中,识别模型权重和激活中的零值以避免计算它们是一个很有前途的方向。本文从稀疏算法、软件框架和硬件加速等方面综述了稀疏神经网络计算的研究现状。我们观察到,除了高效的模型执行策略外,对稀疏结构的搜索可以成为高质量模型探索的通用方法。我们讨论了权重参数数量和模型结构对模型精度的影响。相应的模型分别位于权重主导和结构主导区域。我们表明,对于实际复杂的问题,在权重占主导的区域搜索大型稀疏模型更为有利。为了实现这一目标,需要新的方法来搜索合适的稀疏结构,需要开发新的稀疏训练硬件来促进稀疏模型的快速迭代。

Late Breaking Results: A Neural Network that Routes ICs 最新成果:一个路由ICs的神经网络

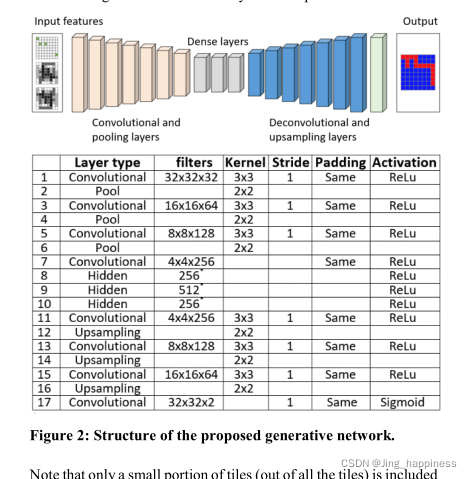

提出了一种全局路由器,它可以从路由电路中学习,并自主地路由不可见的布局。这种方法的独特之处在于将全局路由重新定义为一个经典的图像处理问题。成像问题通过一个深度学习系统得到有效解决,该系统由一个可变自动编码器和自定义损失函数组成。这种全新的路由方法为全局路由并行化提供了一种自然的方式。深度路由器是在一个看不见的64×64 ISPD’98基准电路上设计、训练和测试的。测试结果表明,与最先进的FastRoute路由器相比,路由器的可路由性降低了3.2%,运行时的加速比超过5倍。

全局布线是物理集成电路(IC)设计的一个基本步骤,通过在特定技术限制下将放置的IC元件的引脚与网络连接,在布局(即矩形全局布线片的网格)内生成布线路径。最优全局路由问题是一个NP完全问题。为了降低设计复杂性,提出了近似启发式算法,在合理的时间内产生次优路由。传统路由器通常呈现以下流程。首先,将单个网络分解为多个管脚到管脚的布线目标,并使用寻路算法求解每个目标。接下来,利用基于rip和重路由的算法,在一定的拥塞和设计约束下优化初始路由解决方案。现有全局路由器的一个主要限制是底层算法的串行性,这使得大规模并行多处理器硬件上的并行化不太实用。还提出了统计和概率方法(即强化ML、深层ML或遗传算法)来增强传统的全局路由流[1]-[4]。据作者所知,所有现有的学习增强型解决方案都使用标准的全局路由设计流程,带有一个或多个ML增强型设计阶段。在一些方法中,可以预测拥塞图,并将其用于更有效的rip和重路由迭代线长优化[1,2]。还探索了用遗传算法代替整个优化阶段[1,3]。

请注意,与传统路由器类似,所有这些方法都显示出基本的设计限制:(i)路由过程的迭代性质,(ii)解决方案的次优性,以及(iii)无法有效利用GPU。在这项工作中,提出了一种全新的深度全局路由方法。通过这种方法,经过训练的神经网络(NN)根据全局布线图块(即输入特征)接收管脚的位置和容量,并输出完全布线的布局。这是通过将全局路由问题映射到二维图像到图像操作问题来实现的。最终图像(即布线布局)是从输入图像(即放置的管脚和瓷砖容量)变分自动编码器[5](VAE)一步生成的,VAE是解决图像处理问题的经验证的ML体系结构。有了NNs,路由问题自然可以在现有的GPU平台上并行处理。本文证明了一种设计合理的深度神经网络能够在训练过程中有效地学习路由模式,并在推理过程中检测模式,精确地确定首选的路由启发式算法。因此,这项工作的三个主要贡献是:

**1)用深度NN路由一个看不见的布局,2)一个统一的单步非迭代路由流,3)并行路由系统地运行在GPU硬件上。

假设一个典型的全局布线问题,在该问题中,布局被分割成矩形块,给出了每个块的初始布线容量,并且需要解决许多布线目标。**

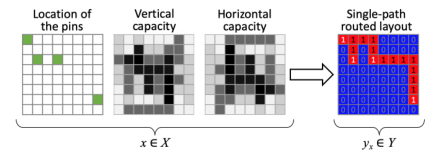

单网布线目标定义为位于特定分幅处的一组管脚,以及布局中每个分幅的更新容量。布线网络由一组相邻的、容量非零的瓦片定义,这些瓦片连接布线目标中的所有管脚。考虑下面的定义,将路由问题映射到有监督的ML任务上,如图1所示。

ParaGraph: Layout Parasitics and Device Parameter Prediction using Graph Neural Networks

段落:布局寄生和使用图形神经网络的设备参数预测

抽象的版图相关寄生和器件参数显著影响集成电路性能,通常是原理图和版图设计之间收敛缓慢的原因。电路设计者通常根据过去的经验来估计寄生效应,这会导致设计者之间的差异和潜在的不准确。在本文中,我们提出了一个图形神经网络模型,通过将电路原理图转换为图形,并利用基于图形图像、关系GCN和图形注意网络的关键建模技术来预测网络寄生和设备参数。此外,集合建模的使用在很大范围内提高了预测值的模型精度。该模型在大型工业电路数据集上进行训练,平均预测R2为0.772(比XGBoost好110%),并将平均模拟误差从设计师估计的100%以上降低到10%以下。

在较新的工艺节点中,网络寄生和物理设备参数对电路布局的依赖性变得越来越重要,只有在布局完成后才能对电路性能进行准确评估。本文提出了一种仅基于电路原理图预测网络寄生和布局相关器件参数的技术。在开始布局过程之前准确预测这些变量有两个主要好处。首先,包含网络寄生和布局相关的设备参数可能会降低电路性能。这通常会导致设计师执行一个迭代过程,在布局后调整设备尺寸,以实现拨号性能,这一过程可能需要多次迭代才能使电路和布局修改趋于一致。由于新技术节点中的DRC规则越来越复杂,单个布局迭代可能需要几天或几周的时间,因此这将大大增加劳动强度。第二,寄生参数和器件参数是包括在寄生感知优化技术中的重要因素,如[1]所示。一个精确的预测器可以帮助优化引擎找到代表真正布局后优化的设计点。之前的工作预测了亚微米技术(如130nm和90nm工艺节点)中的布局寄生和设备参数[2]。他们的方法使用布局构造来构建每个设备的估计布局,并相应地计算设备的几何结构。他们使用线性回归模型根据数量和大小估算净电容

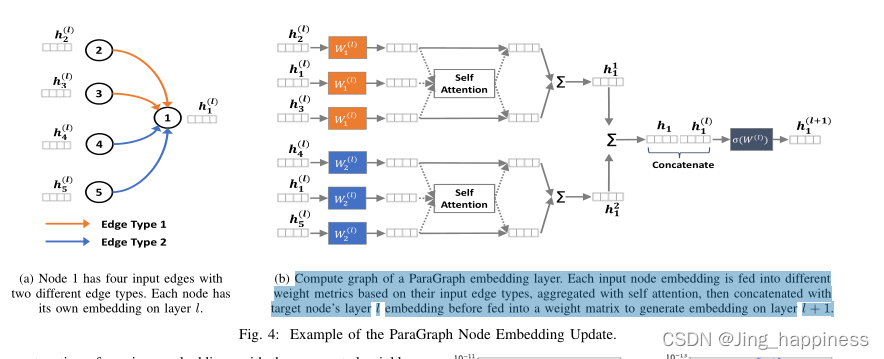

我们设计了自己的图形网络(第段),该网络融合了最先进的GNN模型的关键思想,如GraphSage[4]、Relational GCN[5]和graph Attention network[6],同时将网络调整为具有异构节点和边类型的异构图,以适应电路预测问题域。结果显示,与最先进的GNN模型和XGBoost相比,性能提高了10%-110%。3.我们引入了一种集成建模方法,在0.01fF到10pf的大范围内提高寄生电容的预测精度。论文的结构如下。第二节定义了要预测的布局寄生和设备参数、输入特性和图形构建过程。第三节介绍了各种图形神经网络,并给出了段落模型。第四节介绍了处理大范围预测值的集合建模方法。第五部分介绍了基于大量工业电路培训的实验结果。

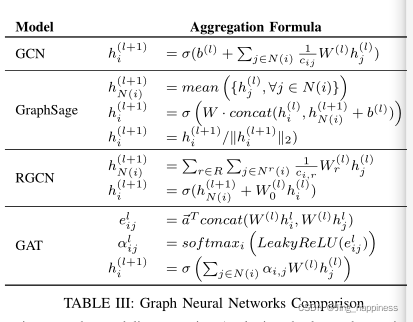

图神经网络(GNN)是图领域的深度学习模型[8],基于两个核心思想:图嵌入和邻域聚合。图嵌入通过将图节点、边、子图及其对应的特征转换为低维向量空间表示来学习嵌入特征。邻居聚集通过聚集来自其局部邻域内节点的信息来学习节点的嵌入属性,类似于卷积神经网络(CNN)中对相邻图像像素的卷积。与Deep walk[9]和node2vec[10]等通过简单的嵌入查找将节点映射到向量嵌入的直接嵌入方法相比,基于GNN的方法可以推广到网络从未见过的图,因为图结构直接并入学习算法中。有四种广泛使用的GNN模型:图卷积网络(GCN)[3]、图年龄[4]、关系GCN(RGCN)[5]和图注意网络(GA T)[6]。这些模型在如何聚合相邻信息方面有所不同。表三显示了这些GNN模型的比较。

表III中列出的所有GNN模型(RGCN除外)都假设该图是同质的,这意味着该图中只有一种节点类型和边类型。尽管RGCN可以为不同的边类型建模,但它仍然局限于单一类型的节点。

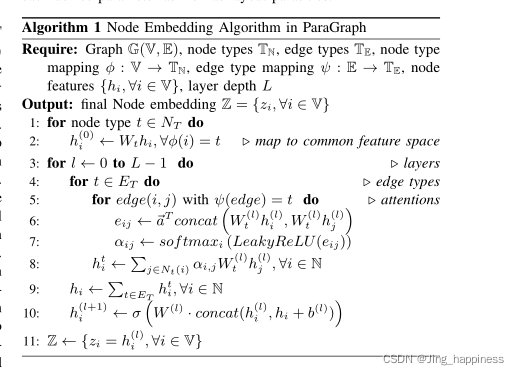

这是有问题的,因为从电路原理图转换的图形是异构的。它们包含多个节点类型,对应于网络和各种类型的设备(晶体管、电阻器、电容器等),其中每个节点类型都有独特的特征尺寸,如表II所示。此外,不同节点类型(网络)之间存在不同的边关系→ 晶体管门→ 晶体管源等)。这导致图形网络包含比GNN通常学习的同质图更多的信息,因此需要开发能够处理电路图的图形模型。不存在众所周知的异构GNN模型,电路图的问题域是唯一的。因此,我们开发了自己的模型。我们称之为GNN模型段落。它包括一个节点嵌入模型和几个完全连接(FC)层,这些层将节点嵌入作为输入,并生成布局寄生或设备参数的预测。我们训练独立的模型来预测每个设备参数以及布局寄生。

模型节点嵌入过程

1222

1222

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?