一、创作目的

掌握组合逻辑电路的分析与设计。掌握真值表、逻辑函数表达式、卡诺图化简基本概念和方法。

二、组合逻辑电路原理

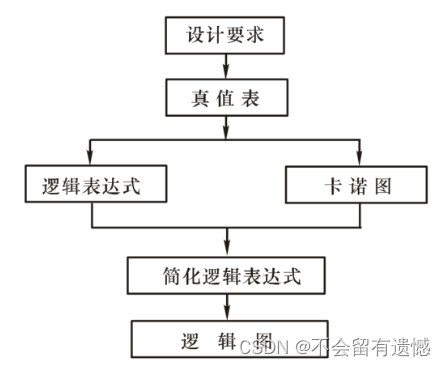

使用中、 小规模集成电路来设计组合电路是最常见的逻辑电路。 设计组合电路的一般步骤如图

3-1

所示。

图

3-1

组合逻辑电路设计流程图

根据设计任务的要求建立输入、 输出变量, 并列出真值表。 然后用逻辑代数或卡诺图

化简法求出简化的逻辑表达式。 并按实际选用逻辑门的类型修改逻辑表达式。 根据简化后

的逻辑表达式, 画出逻辑图, 用标准器件构成逻辑电路。 最后, 用实验来验证设计的正确

性。

1、组合逻辑电路–四路表决器

原理:用“与非门”设计一个表决电路,当四个输入端A、B、C、D中有三个及以上为“1”时,输出端才为“1”。

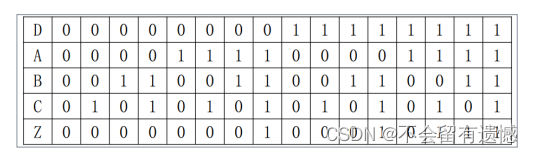

设计步骤: 根据题意列出真值表如表3-1 所示, 再填入卡诺图表3-2 中。

表

3-1

真值表(横排改为竖排)

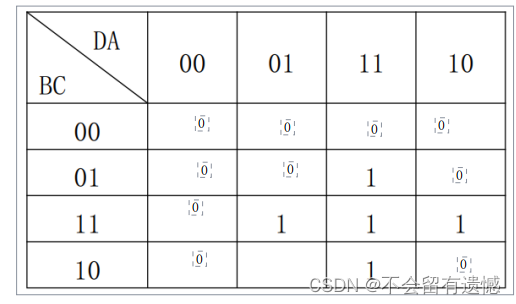

表 3-2

由

卡诺图

得出逻辑表达式, 并演化成

“

与非

”

的形式:

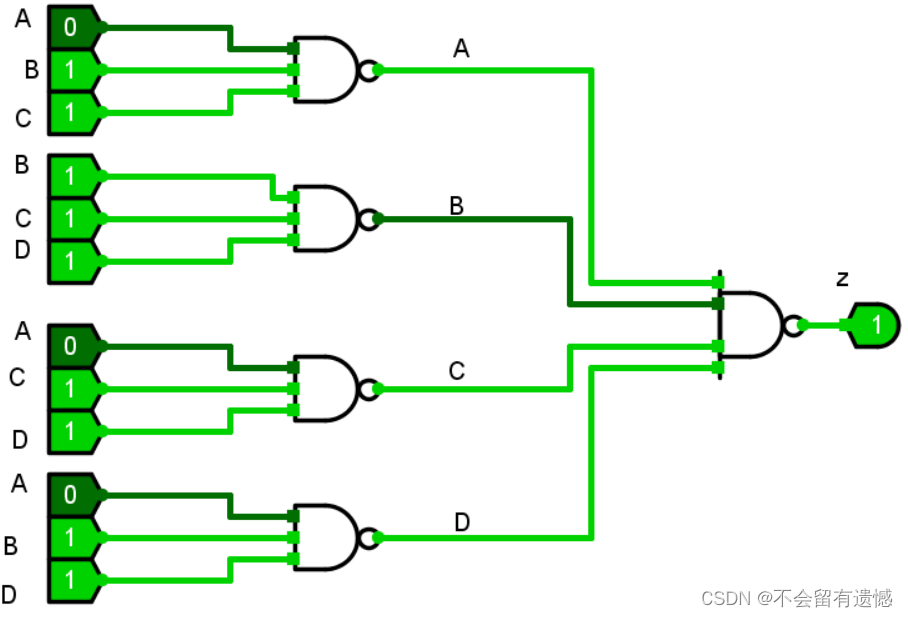

根据逻辑表达式可画出仿真电路图,如下所示:

二、用表决器将投票结果显示在LED屏上

7段数码显示管(LED)是由7个单独LED二极管组合而成(忽略小数点),经常用来显示0-9这些数字。它可以用4个输入项A、B、C、D和7个输出项a~g的逻辑关系真值表来表达。

CD4511芯片能够完成这种对应关系的转换。

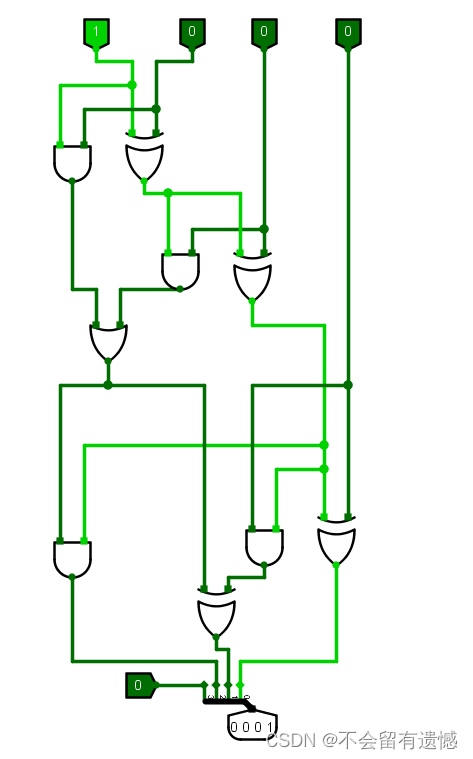

由原理图可知,7段数码显示管只能将二进制转换为十进制数字显示,所以要先将投票为1的全部结果相加,再将其转化为二进制。我们可以用全加器来实现4位数的相加,其电路仿真图如下所示

三、组合逻辑电路化简

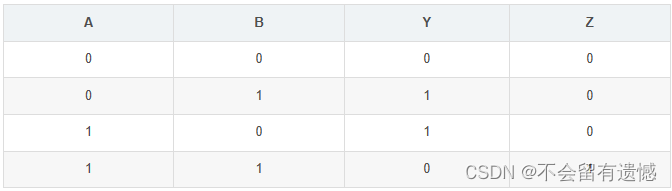

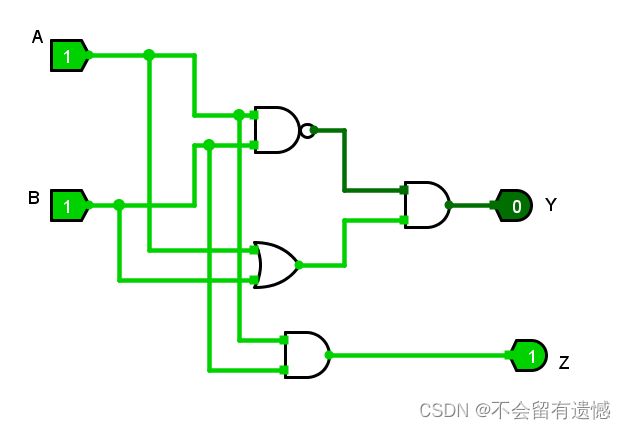

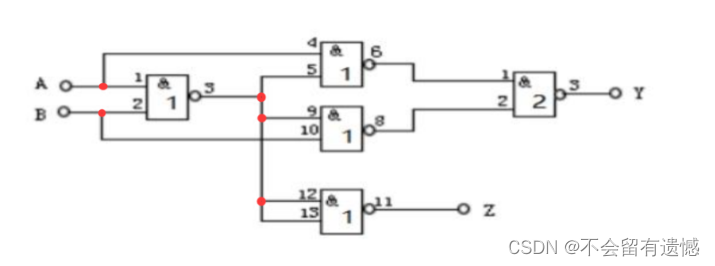

根据组合逻辑电路图,得出Y与Z的逻辑表达式,并重新设计一个新的简化电路。

其逻辑电路图真值表如下:

由此可列出Y和Z的逻辑表达式:

Y=(A'+B')(A+B);Z=AB

在logisim的电路仿真图如下:

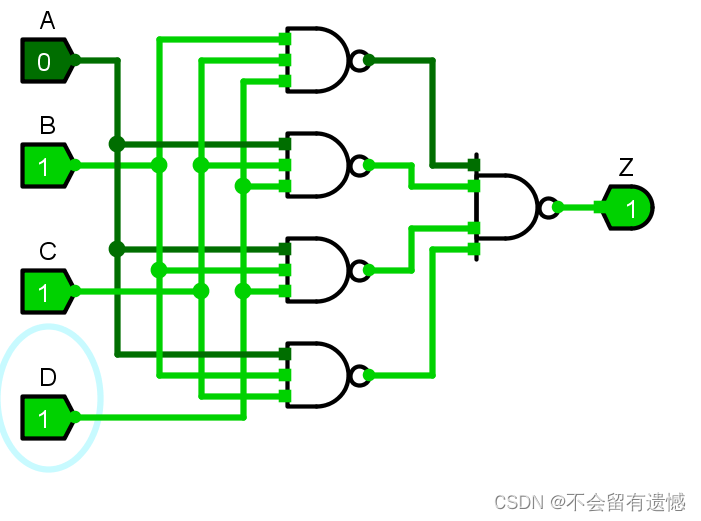

四、在Logisim中使用分析组合逻辑电路功能完成四路表决器

电路图如下:

本文介绍了组合逻辑电路的设计过程,包括真值表、逻辑表达式的求解、四路表决器实例、LED显示应用及全加器的使用。并通过Logisim软件进行电路仿真和简化。

本文介绍了组合逻辑电路的设计过程,包括真值表、逻辑表达式的求解、四路表决器实例、LED显示应用及全加器的使用。并通过Logisim软件进行电路仿真和简化。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?