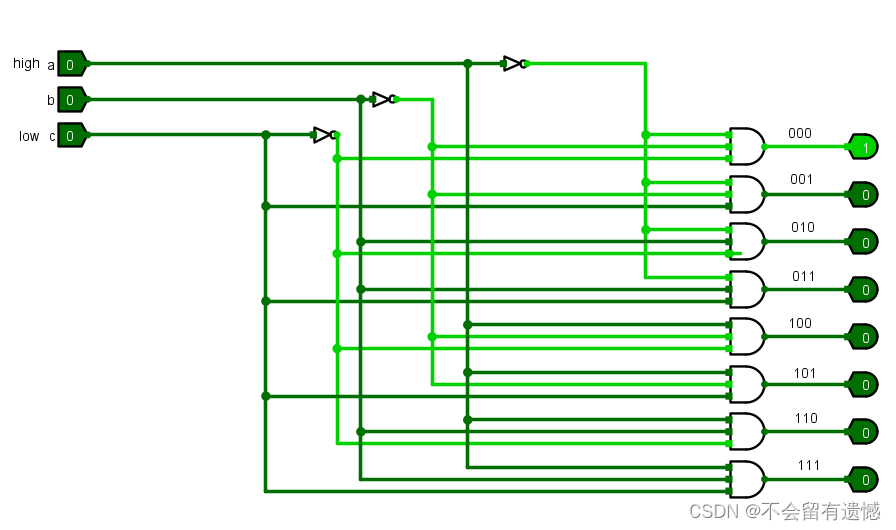

1.首先使用Logsim绘制一个3-8译码器电路图,列出3-8译码器的逻辑真值表。

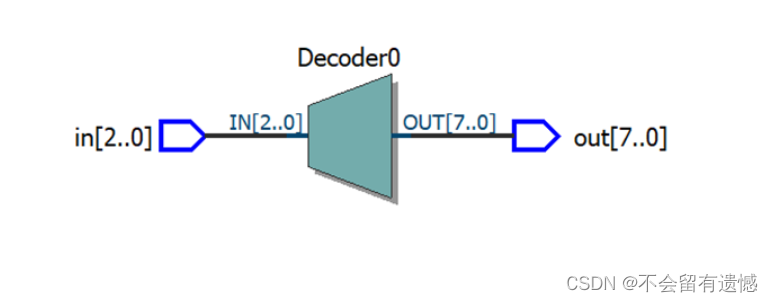

2.然后采用Verilog编程(if-else或者case)设计一个3-8译码器,生成RTL原理电路图

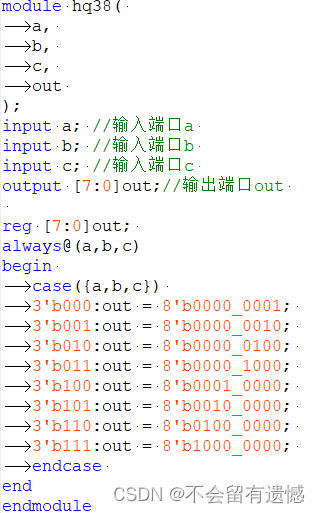

其代码如下:

3.modelsim电路仿真

代码:

仿真结果:

4.分析并回答下列问题:

1)Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

答:生成的电路图已经把原始设计的中间电路综合简化为一个模块。结果一致。

2) Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以? (即是否可以把 output reg [7:0] out 改为 output [7:0] out) 修改后会出现什么错误?为什么会出错?

答:wire型数据常用来表示以assign关键字指定的组合逻辑信号。模块的输入输出端口类型都默认为wire型。reg型表示的寄存器类型。always模块内被赋值的信号,必须定义为reg型,代表触发器。而我们上面使用的输出信号是在always模块内被赋值所以使用reg类型而非wire类型。删掉output reg 中的reg后会被默认位wire类型,但wire可以有多个驱动器,reg只能有一个,因此会报错。

485

485

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?