文档下载地址:

https://download.csdn.net/download/IT_Scratch/87618612?spm=1001.2014.3001.5501

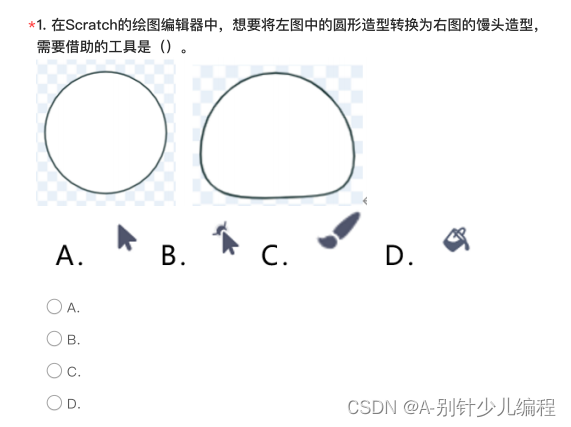

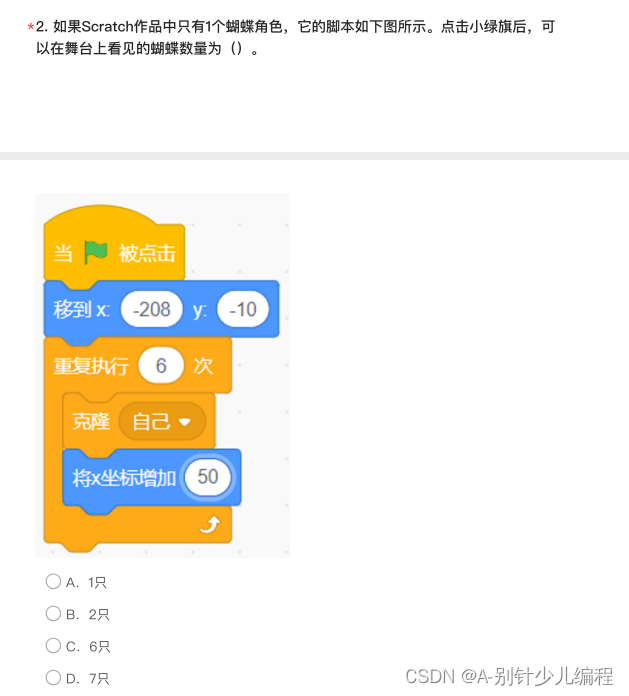

2023年NOC初赛-Scratch(⼩学低年级组-

卷2)

文档下载地址:

https://download.csdn.net/download/IT_Scratch/87618612?spm=1001.2014.3001.5501

3594

3594

3688

3688

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?