第一周

在这里在这里https://blog.csdn.net/JCMLSY/article/details/105450490

第二周

-

格雷码好难记啊,但是结合卡诺图我又可以了 (0~15格雷码速记大法)

-

对于一个逻辑函数,任意两个最小项的与,结果为0 【最小项与最大项的性质】

-

奇数个1连续异或结果为1,偶数个1连续异或结果为0。

-

【最小项和最大项之间的关系】

- 解析如下(感谢大佬的解答):

- 对偶运算的性质

- 异或与同或的神奇性质【可用真值表证明】

- 【易错概念】对偶与取非完全没关系!!!非常容易弄混!!!

- 异或运算满足结合律【可用真值表证明】

- 解析如下:

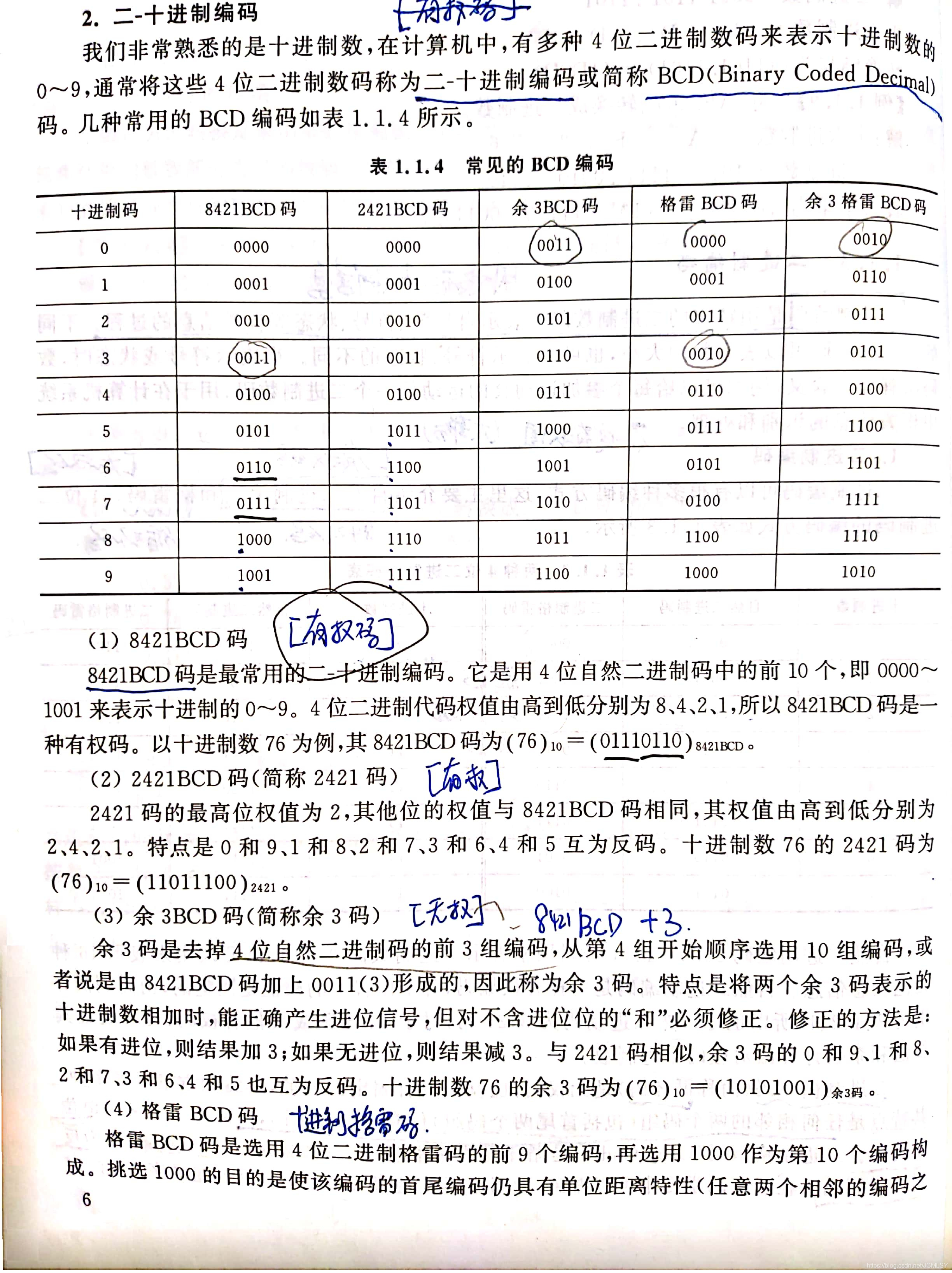

- 首先什么是8421BCD码? 请翻到课本P6

- 什么是校验位?百度百科告诉我们:

第三周

- VerilogHDL中,b被赋成新值a的操作并不是立刻完成,而是在块结束时才完成,且块内多条赋值语句在块结束时同时赋值的形式,被称为非阻塞赋值方式,赋值语句为b<=a.

- TTL逻辑门电路的输入端悬空,相当于输入高电平。

- CMOS逻辑门电路的输入端悬空,相当于输入电平不确定(所以CMOS门输入端不可以悬空)

- 扇出系数反映了逻辑门的带负载能力,是指逻辑门能够驱动同类们的最大个数。

- 输出端直接相连可以实现“线或”功能的逻辑门是ECL门。

- 某两输入TTL与非门,其中一个输入端A接低电平0.2V,另一个输入端B悬空,用万用表测量B端的电压,最可能的值为0.2V。

- 某两输入TTL与非门,其中一个输入端A通过5kΩ电阻接地,另一个输入端B悬空,用万用表测量B端的电压,最可能的值为1.4V

- TTL三态门:0,1,高阻态

- 在不影响逻辑功能的情况下,CMOS与非门多余的输入端可以接高电平

- 和CMOS相比,ECL最突出的优势在于工作速度快。

- 通过适当的连接和控制,可以实现双向传输的门电路是三态输入的门电路。

- 一个逻辑函数的任意两个不同最小项的乘积恒等于零。【√】

- 一个逻辑函数可能有几种最简式,但其两种标准形式具有唯一性。【√】

- 一个逻辑函数的全部最大项之几恒为零。【√】

- 在同一个逻辑函数的两种标准形式中,其最小项下标集合与最大项下标集合为互补集。【√】

- 用卡诺图化简法求函数的最简或与式,应该圈0,且每个圈对应一个和项。【√】

- always块与assign块语句是并发执行的,assign语句一定要放在always块之外。【√】

第四周

- 在不影响逻辑功能的情况下,CMOS与非门多余的输入端可以通过电阻接电源VDD。

- 晶体管饱和越深,带灌电流负载能力越强,但工作速度越慢(√)【要提高反相器带灌电流负载能力,关键在于加大晶体管的饱和深度,增加IB,增大RC,减小IRC,饱和越深,带负载能力越强】

- 对TTL电路而言,通过电阻接电源和大电阻接地均等效于接入高电平。低电阻接地等效于接入低电平。

- 两个反相器并联使用,可以增加驱动能力。(√)

- TTL与非门的开门和关门电平越接近阈值电压VT,噪声容限越大,抗干扰能力越强。(√)

- 反相器的拉电流负载电阻过小时,主要对输出的高电平产生影响。(√)【拉电流主要影响高电平,灌电流主要影响低电平】

- ECL门工作速度快的原因是晶体管不进入饱和状态,输出还能实现“线或”功能。

- OC、OD “线与”

- TTL门电流驱动能力比CMOS门强,CMOS门噪声容限高于TTL门。

第五周

- 在组合逻辑电路中,任意时刻的输出由该时刻的输入决定。(与过去的输入无关)

- 若输入信号源提供反变量,对于最简与或式,一定可用两级与非门实现。

- 或与表达式变换为或非-或非表达式时,只要将该或与表达式两次求反,再使用**反演律(摩根定理)**就可以得到或非-或非表达式。

- 4位二进制数加法运算电路,可以采用4个全加器级联的方式来实现。

- 采用SSI设计组合电路逻辑时,往往追求逻辑门数最少。

- 无法用VerilogHDL语言描述电压比较器LM311

- 对于TTL门电路,加大晶体管的饱和深度可以提高其带灌电流负载的能力。

- 在VerilogHDL中,非阻塞赋值是指在过程块内当前赋值语句不会阻断其后的语句,该操作只能用于“initial”块和“always”块中的reg型变量赋值。

- 基于SRAM的FPGA器件,在每次上电后必须进行一次配置。

- 一个仅由各种逻辑门构成的数字电路一定是组合逻辑电路。 【X,时序逻辑电路也可以仅有各种逻辑门组成】

第六周

KiCad给👴整懵了

15万+

15万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?