以下在数字系统设计(verilog)学习过程中联系过的实验,在这里进行记录。

1.问题主干:

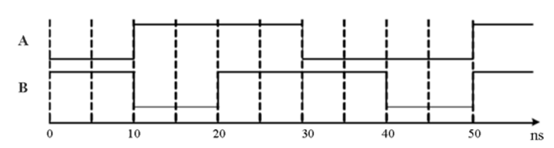

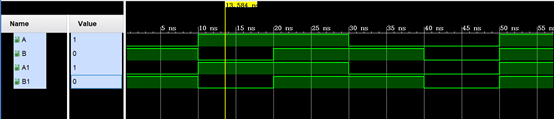

区别begin-end与fork-join语句块,并生成特定信号波形。

2.内容分析:

Begin_end是串行块,其中每条语句是按顺序从上至下工作;而fork_join是并行块,其中每条语句是并行执行的。

与一般对硬件电路工作原理的理解不同,begin_end是可以综合的,即可以生成对应的硬件电路;而fork_join是不能综合的,没有对应的硬件电路,一般仅在testbench文件中使用来进行测试使用。

Begin_end中,每句话前如果有延时语句,那么这个延时是前一句话结束到这句话开始的延时,延时逐句累加,而fork_join语句中每句话前面的延时是这句话开始时间到fork块开始的时间。

根据以上分析,可以在同一个tb文件中通过这两种不同的方式生成同样的两组测试信号。

3. 参考程序:

.v文件:

`timescale 1ns/1ps

module checkfile(A,B,A1,B1);

output reg [0:0] A,B,A1,B1;//下面将会通过过程赋值语句对aba1b1进行赋值,他们是否为wire类型呢?

initial begin

#0 A=0;B=1;

#10 A=1;B=0;

#10 A=1;B=1;

#10 A=0;B=1;

#10 A=1;B=1;

end

initial fork //这里会提示error或者warning,fork_join无法被综合

#0 A1=0;

#0 B1=1;

#10 A1=1;

#10 B1=0;

#20 A1=1;

#20 B1=1;

#30 A1=0;

#30 B1=1;

#40 A1=0;

#40 B1=0;

#50 A1=1;

#50 B1=1; //fork_join的每条语句前面都必须有延时,否则就是从fork开始零延时直接执行

join

endmodule

4. 实验结果

可以看到,两组波形完全相同。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?