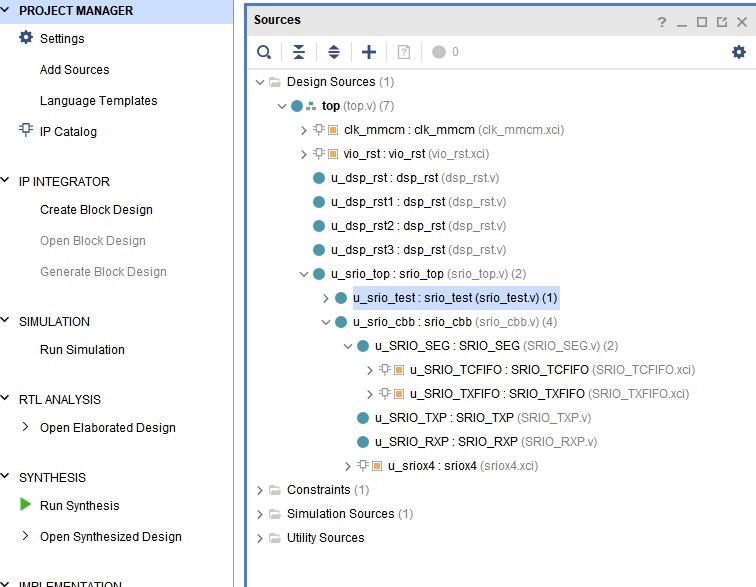

xilinx vivado verilog srio开发,包含维护包、读写和门铃等功能,顶层封装为fifo,操作简单,简单修改即可应用到实际工程中,附含srio使用说明文档和免费license

ID:36468694416686028

又在写bug啊

Xilinx Vivado是一款强大的FPGA开发工具,可用于实现各种复杂的数字电路设计。在Vivado中,Verilog是一种常用的硬件描述语言,可用于编写高效、可靠的FPGA设计代码。本文将围绕使用Xilinx Vivado和Verilog开发SRIO(Serial RapidIO)进行展开,介绍SRIO的功能、原理、设计、验证以及应用等方面的内容。

SRIO是一种高速串行总线协议,适用于高性能计算、数据中心和通信等领域。它提供了高带宽、低延迟的数据传输,并支持多种拓扑结构和链路配置。在许多应用中,SRIO被广泛用于连接FPGA与其他设备、模块或系统,实现高效的数据交换和通信。

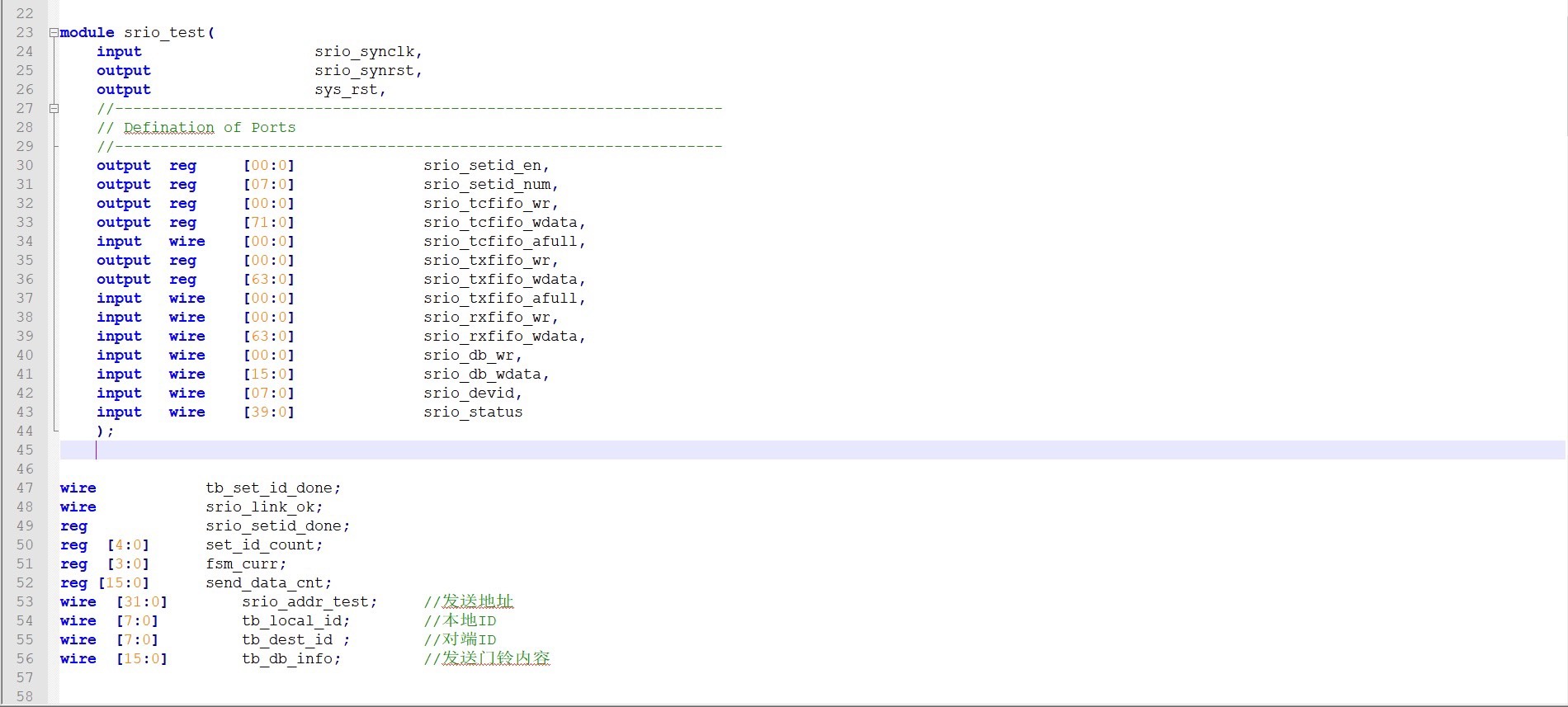

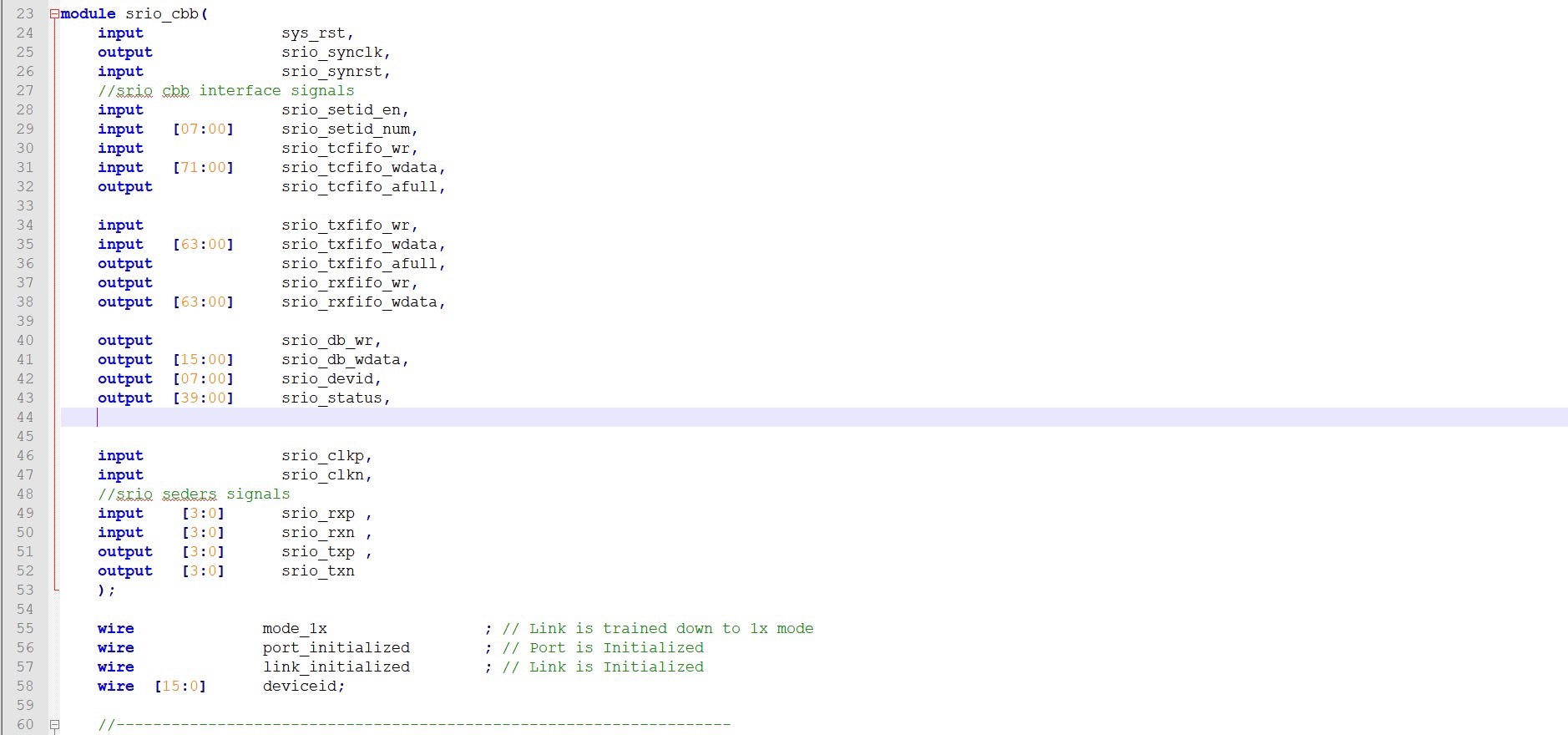

本文将以FIFO顶层封装为例,展示如何在Xilinx Vivado中使用Verilog开发和维护SRIO的读写和门铃功能。FIFO作为一个简单的例子,具有很好的可扩展性和可重用性,可应用于各种实际工程中。通过简单的修改,我们可以将其应用于不同的场景和需求。

首先,我们需要了解SRIO的基本原理和工作方式。SRIO协议定义了一系列的数据包格式、传输规则和控制信号,用于实现可靠的数据传输和通信。在设计过程中,我们需要仔细考虑SRIO协议的特性和限制,确保设计的正确性和性能。

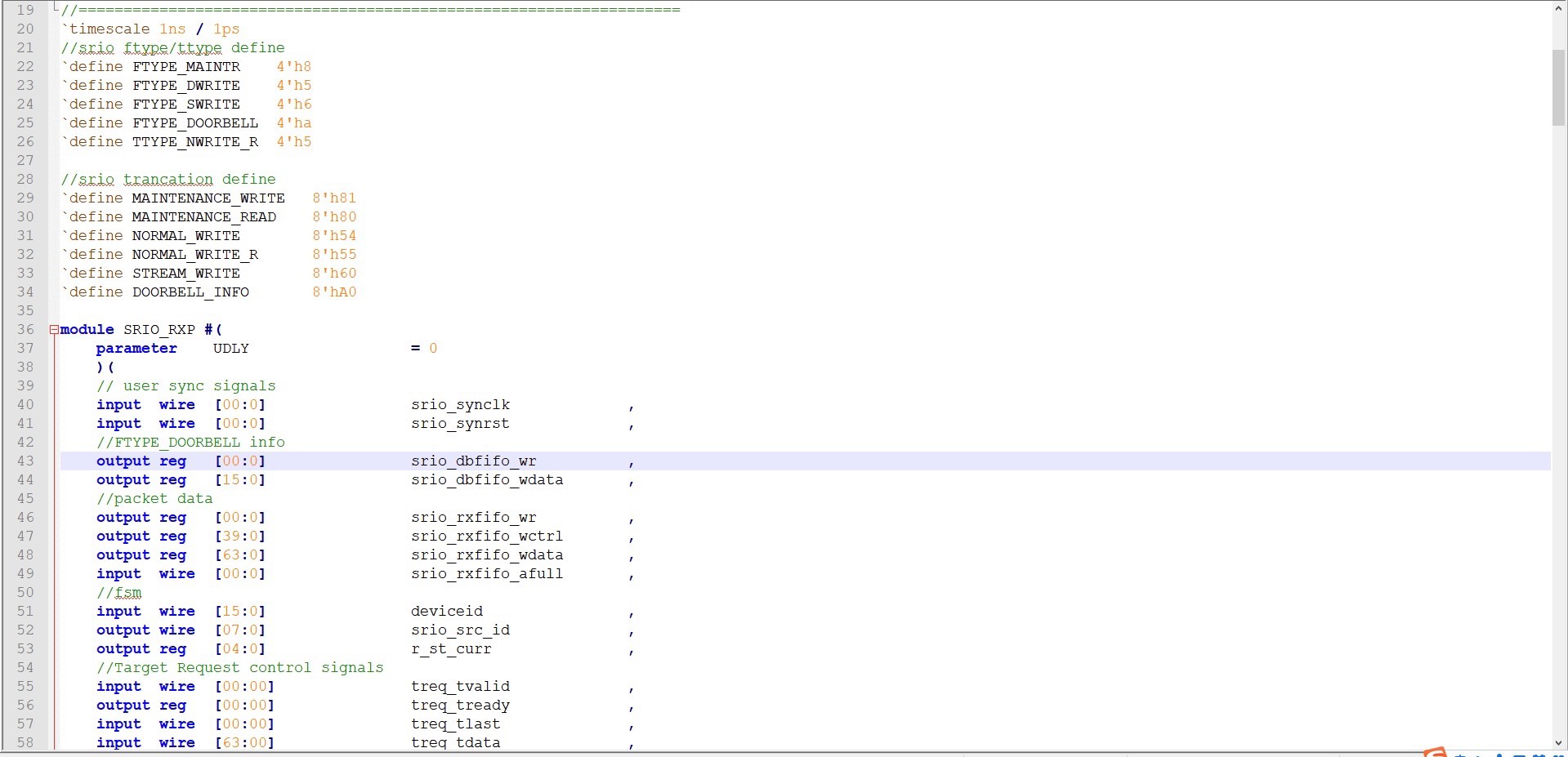

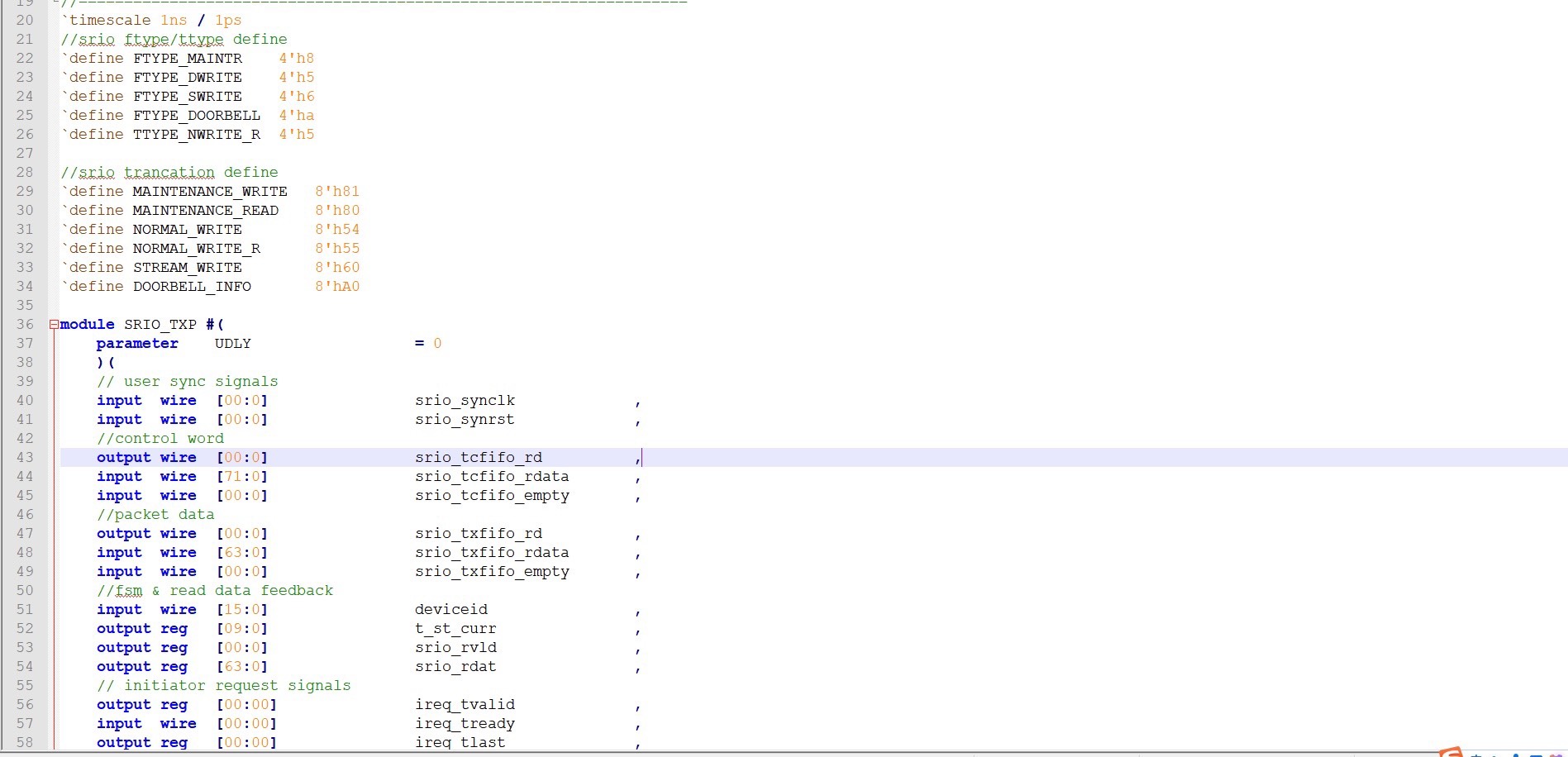

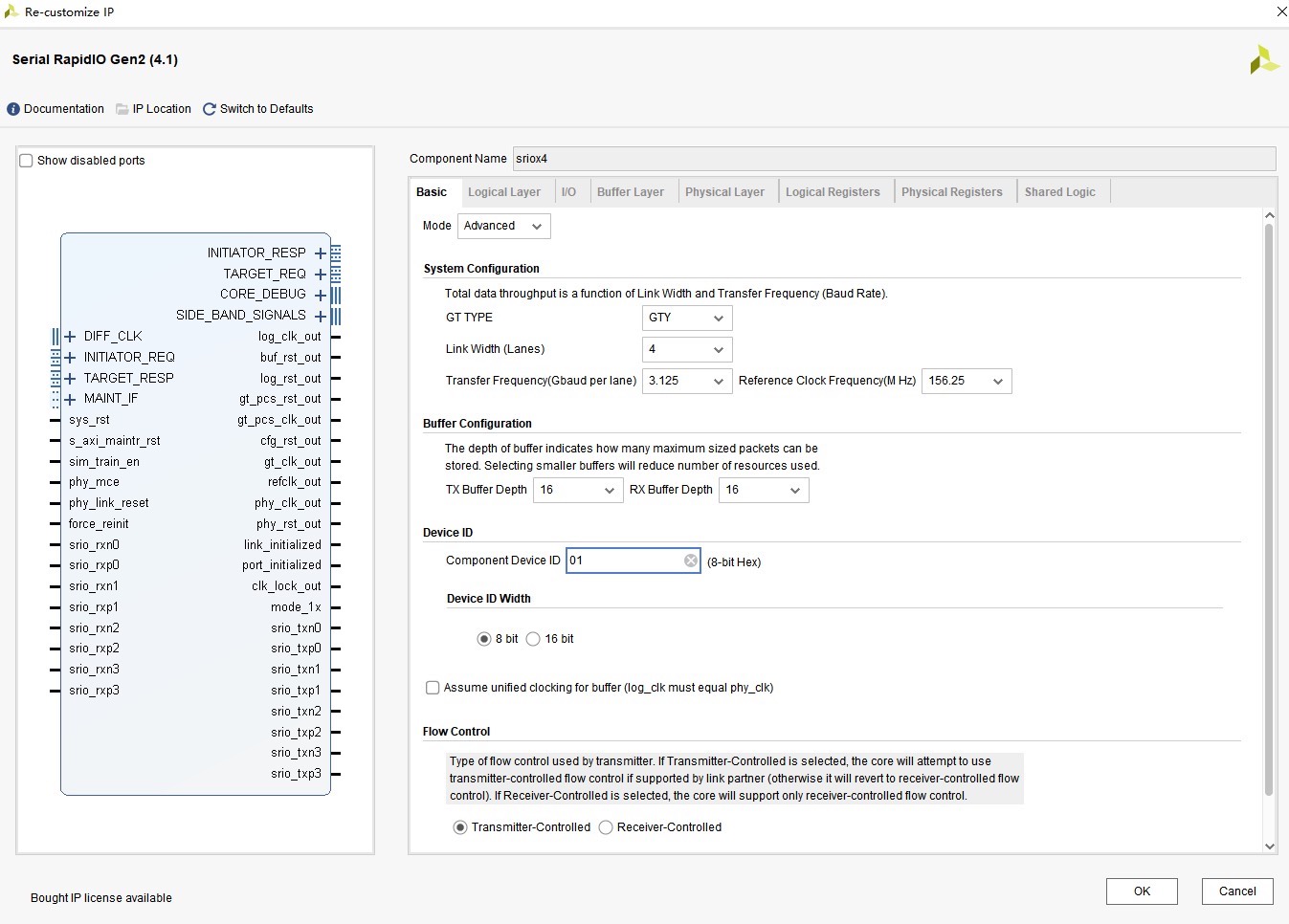

接下来,我们将介绍如何使用Xilinx Vivado进行SRIO的Verilog设计。Vivado提供了丰富的工具和资源,可帮助我们快速进行SRIO的设计和验证。我们可以使用Vivado中的IP核生成器、Block Design和Constraint Wizard等工具,来快速搭建和配置SRIO的模块和接口。

然后,我们将详细讲解SRIO的读写和门铃功能的设计和实现。读写功能允许FPGA与外部设备之间进行数据传输,可以实现高速数据读取和写入。门铃功能则用于实现事件通知和异步通信,可以在需要时触发特定的操作和处理。

在设计完成后,我们需要对SRIO进行验证和测试,确保其功能正确和稳定。Vivado提供了丰富的仿真和调试工具,可帮助我们进行全面的测试和验证。我们可以通过仿真、时序分析和硬件调试等方法,来验证SRIO的功能和性能,并进行必要的修复和优化。

最后,我们还将附上SRIO的使用说明文档和免费许可证,以便更多人可以通过简单的修改和应用,将SRIO集成到自己的实际工程中。这些文档和许可证将帮助用户更好地了解和使用SRIO,并提供必要的支持和指导。

通过本文的介绍和实例,相信读者对于在Xilinx Vivado中使用Verilog开发和维护SRIO的读写和门铃功能有了更深入的理解和认识。SRIO作为一种高速串行总线协议,将为FPGA开发者提供更多的选择和灵活性,帮助其实现高效的数据交换和通信。我们期待更多人能够通过本文的指导和示例,掌握SRIO的设计和应用技

【相关代码,程序地址】:http://fansik.cn/694416686028.html

423

423

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?