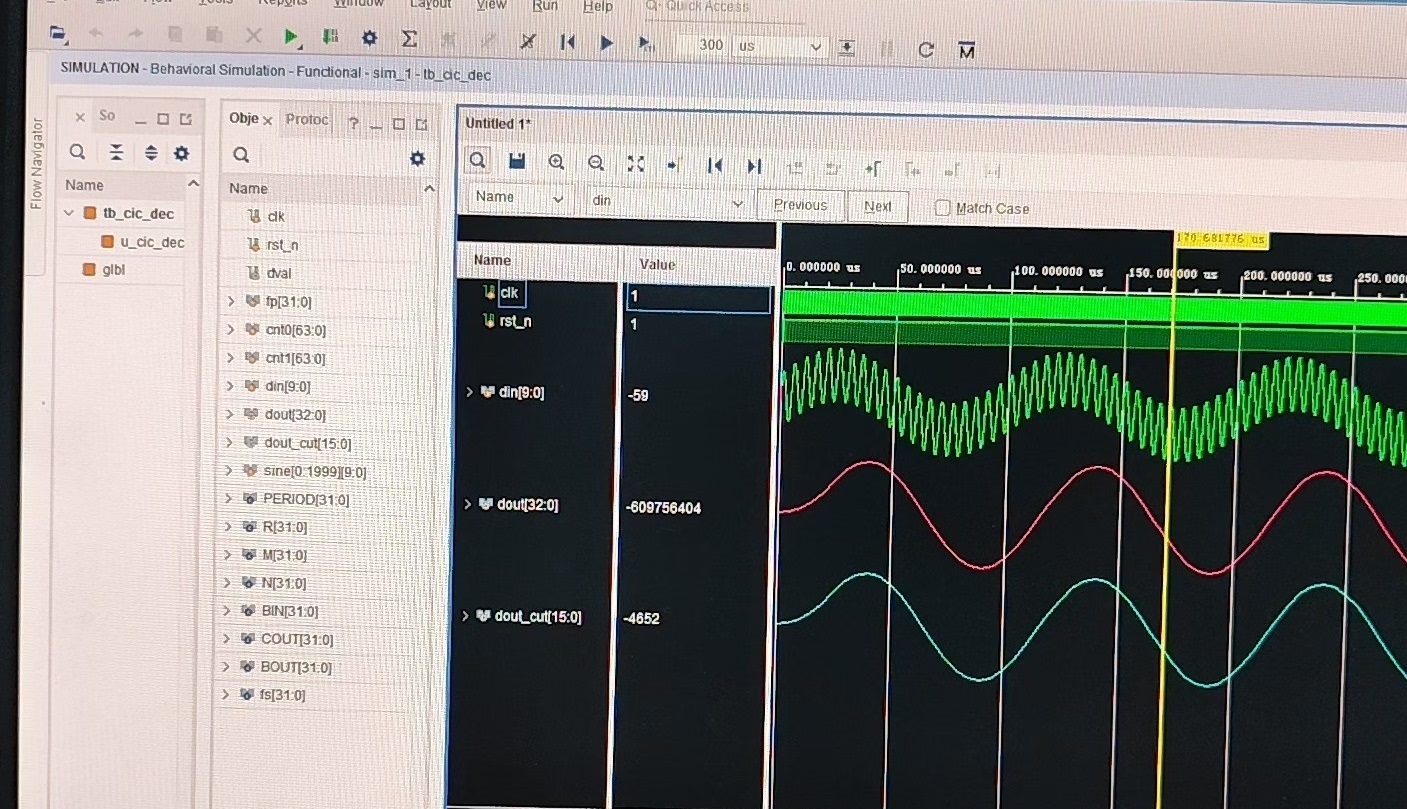

FPGA实现 CIC抽值滤波 滤波器 verilog 仿真和matlab simulink仿真 vivado ise quartus软件均可以,匹配滤波器系数生成等 含说明 doc,电子ZL售出不退,这个需要一定的数字信号处理知识和熟练操作相应软件,目前还做不到手把手的教,不太熟练的,发vivado工程,一键跑程序得出图1和图3所示

ID:1920669757527532

FPGA_2049

FPGA实现 CIC抽值滤波 滤波器 verilog 仿真和matlab simulink仿真 vivado ise quartus软件均可以,匹配滤波器系数生成等 含说明 doc,电子ZL售出不退,这个需要一定的数字信号处理知识和熟练操作相应软件,目前还做不到手把手的教,不太熟练的,发vivado工程,一键跑程序得出图1和图3所示,希望理解

在现代通信和信号处理系统中,滤波器是一种重要的组件,用于去除信号中的不需要的频率分量。CIC(Cascaded Integrator Comb)抽值滤波器作为一种高效的数字滤波器,被广泛应用于FPGA(Field Programmable Gate Array)实现的信号处理系统中。本文将探讨FPGA实现CIC抽值滤波器的原理和方法,并介绍了使用Verilog进行仿真和Matlab Simulink进行仿真的过程。同时,我们还将介绍如何使用Vivado、ISE和Quartus等软件进行匹配滤波器系数生成,并提供相应的说明文档。

首先,让我们来了解一下CIC抽值滤波器的原理。CIC滤波器是一种基于累加器和组合器的数字滤波器,其核心思想是通过级联多个累加器和组合器来实现高效的抽值滤波。CIC滤波器的输出是输入信号的抽值版本,可以通过调整累加器的阶数和差分延迟,以满足不同的抽值倍数和滤波要求。

在FPGA实现CIC抽值滤波器时,Verilog是一种常用的硬件描述语言,可以用于描述CIC滤波器的结构和功能。通过Verilog语言,我们可以定义滤波器的输入和输出接口,以及各个级联累加器和组合器之间的连接关系。同时,Verilog还支持仿真功能,我们可以使用仿真工具对CIC滤波器进行功能验证和性能评估。

除了Verilog仿真外,Matlab Simulink也是一种常用的仿真工具,可用于模拟和验证CIC抽值滤波器的性能。Simulink提供了丰富的信号处理模块和系统建模工具,可以方便地搭建CIC滤波器的仿真模型,并对其进行仿真分析。通过Simulink仿真,我们可以更直观地了解CIC滤波器的输入输出特性,以及滤波器参数对性能的影响。

在实际使用中,我们可以根据需要选择合适的软件平台来实现CIC抽值滤波器。Vivado、ISE和Quartus等软件都是常见的FPGA开发工具,它们提供了丰富的功能和资源,可以支持CIC滤波器的设计和实现。根据具体的开发环境和需求,我们可以选择其中一种软件,并按照相应的流程和指导进行操作。

对于匹配滤波器系数的生成,我们可以利用Vivado、ISE或Quartus等软件提供的工具和功能进行实现。这些软件通常都配备了系数生成工具,可以根据滤波器的设计参数和要求,自动生成匹配滤波器的系数。通过生成的系数,我们可以更准确地配置CIC滤波器,以满足不同的滤波需求。

在实际操作中,我们意识到CIC抽值

以上相关代码,程序地址:http://coupd.cn/669757527532.html

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?