Circuits>Combinational logic>Basic Gates

1.wire

功能:

将输入in和输出out连接起来

收获:

代码:

module top_module (

input in,

output out);

assign out = in;

endmodule

2.GND

功能:

将输出接地

收获:

代码:

module top_module (

output out);

assign out = 1'b0;

endmodule

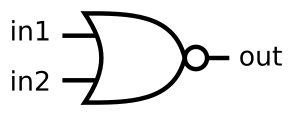

3.NOR

功能:

收获:

或非门

代码:

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1|in2);

endmodule

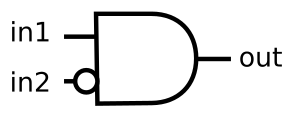

4.Another gate

功能:

收获:

与或非以及各种的国外流行符号和逻辑符号以及常用符号。

代码:

module top_module (

input in1,

input in2,

output out);

assign out = in1&(~in2);

endmodule

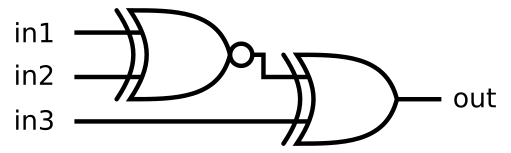

5.Two gates

功能:

收获:

代码:

module top_module (

input in1,

input in2,

input in3,

output out);

assign out = (~(in1^in2))^in3;

endmodule

6.More logic gates

功能:

各种逻辑门电路

收获:

了解了各种门电路的符号以及英文表达。

代码:

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and = a&b;//与

assign out_or = a|b;//或

assign out_xor = a^b;//异或

assign out_nand= ~(a&b);//与非

assign out_nor = ~(a|b);//或非

assign out_xnor= ~(a^b);//异或非

assign out_anotb=a&~b;

endmodule

7.7420 chip

功能:

收获:

代码:

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ~(p1a&p1b&p1c&p1d);

assign p2y = ~(p2a&p2b&p2c&p2d);

endmodule

8.Truth tables

功能:

对于组合逻辑电路来说,一个输入对应一个固定的输出,即真值表,将真值表转换成逻辑表达式。

收获:

复习最小项和卡诺图,将真值表转换为卡诺图,然后变成表达式,再进行转换。

代码:

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

assign f = (x3&x1)|((~x3)&x2);

endmodule

9.Two-bit equality

功能:

检查输入的两个两位数据是否相等

收获:

代码:

也可以是使用assign z = (A[1:0] == B[1:0]);

module top_module ( input [1:0] A, input [1:0] B, output z );

assign z = (A-B)?1'b0:1'b1;

endmodule

10.Simple circuit A

功能:

z = (x^y)&x

收获:

代码:

module top_module (input x, input y, output z);

assign z = (x^y)&x;

endmodule

11.Simple circuit B

功能:

根据波形,反向写出代码。

收获:

根据波形,转换为卡诺图,从而写出表达式。

代码:

module top_module ( input x, input y, output z );

assign z = ~(x^y);

endmodule

12.Combine circuits A and B

功能:通过使用mt2015 q4a函数和mt2015 q4b

收获:根据电路图写代码,先写子模块,再写top模块。

代码:

module top_module (input x, input y, output z);

//

wire z0,z1,z2,z3;

//

assign z = (z0|z1)^(z2&z3);

mt2015_q4a mt2015_q4a_inst0(

.x(x),

.y(y),

.z(z0)

);

mt2015_q4a mt2015_q4a_inst1(

.x(x),

.y(y),

.z(z2)

);

mt2015_q4b mt2015_q4b_inst0(

.x(x),

.y(y),

.z(z1)

);

mt2015_q4b mt2015_q4b_inst1(

.x(x),

.y(y),

.z(z3)

);

endmodule

module mt2015_q4a(input x,input y,output z);

assign z = (x^y)&x;

endmodule

module mt2015_q4b(input x,input y,output z);

assign z = ~(x^y);

endmodule13.Ring or vibrate?

功能:

写一个模块,两个输入,两个输出,根据输入判断输出是响铃还是震动

收获:

对于硬件来说,设计一个电路或者针对一个功能设计一段代码,设计思想应该采用从后往前的思想,不像软件一样,采用的是if之类的,对于硬件使用的是assign需要从输出想输入。

代码:

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

assign motor = (ring&vibrate_mode)?1'b1:1'b0;

assign ringer = (ring&(~vibrate_mode))?1'b1:1'b0;

endmodule

14.Thermostat

功能:根据冷热控制空调、加热器和电扇的开关,也可以单独控制电扇。

收获:根据要求设计代码和电路。

代码:

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

//

//

assign heater = too_cold&mode;

assign aircon = too_hot&(~mode);

assign fan = fan_on|heater|aircon;

endmodule

15.3-bit population count

功能:

统计输入数据1的个数

收获:

也可以将其转换成真值表的形式,再使用逻辑表达式,最后描述出来。

代码:

module top_module(

input [2:0] in,

output [1:0] out );

assign out = in[0] + in[1] + in[2];

endmodule

16.Gates and vectors

功能:

根据输入比较相邻是否相等,是否都是1,是否出现1.

收获:

对于与或比较好写,对于按位比较是否相等,并且按位输出,可以按照异或处理。

代码:

module top_module(

input [3:0] in,

output [2:0] out_both,

output [3:1] out_any,

output [3:0] out_different );

assign out_both = in[3:1]&in[2:0];

assign out_any = in[3:1]|in[2:0];

assign out_different = (in[3:0]^{in[0],in[3:1]});

endmodule

17.Even longer vectors

功能:

16.的拓展,输入100位数据进行操作。

收获;

代码:

module top_module(

input [99:0] in,

output [98:0] out_both,

output [99:1] out_any,

output [99:0] out_different );

assign out_both = in[99:1]&in[98:0];

assign out_any = in[99:1]|in[98:0];

assign out_different = in[99:0]^{in[0],in[99:1]};

endmodule

396

396

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?