Circuits>Sequential Logic>Latches and Flip-Flops

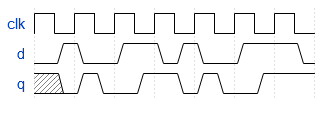

1.D flip-flop

功能:

D触发器,上升沿触发,具有存储一比特的功能。

收获:

代码:

注:修改,对于时钟模块,应该使用非阻塞。

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

always@(posedge clk)

begin

q = d;

end

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

endmodule

2.D flip-flop

功能:

八位触发器,上升沿触发输出。

收获:

代码:

module top_module (

input clk,

input [7:0] d,

output reg [7:0] q

);

always@(posedge clk)

begin

q <= d;

end

endmodule

3.DFF with reset

功能:

同步带高电平复位的八位上升沿触发器。

收获:

代码:

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output reg [7:0] q

);

always@(posedge clk)

begin

if(reset)

q <= 8'b0;

else

q <= d;

end

endmodule

4.DFF with reset value

功能:

同步高电平复位到0x34,下降沿触发的八位触发器。

收获:

代码:

module top_module (

input clk,

input reset,

input [7:0] d,

output [7:0] q

);

always@(negedge clk)

begin

if(reset)

q <= 8'h34;

else

q <= d;

end

endmodule

5.DFF with asynchronous reset

功能:

异步高电平复位,上升沿触发。

异步:asynchronous 同步:synchronous

收获:

代码:

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk or posedge areset)

begin

if(areset)

q <= 8'b0;

else

q <= d;

end

endmodule

6.DFF with byte enable

功能:

16位二进制触发器,同步低电平复位,上升沿触发,两个使能输入存储。

收获:

代码:

module top_module (

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output [15:0] q

);

reg [15:0] s;

always@(posedge clk)

begin

s[15:8] = byteena[1]?d[15:8]:s[15:8];

s[7:0] = byteena[0]?d[7:0]:s[7:0];

if(~resetn)

q <= 16'b0;

else

q <= s;

end

endmodule

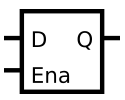

7.DFF with byte enable

功能:

这是一个锁存器。

收获:

代码:

module top_module (

input d,

input ena,

output q);

reg s;

assign q = s;

always@(*)

begin

if(ena)

s = d;

end

endmodule

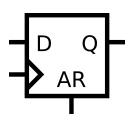

8. DFF

功能:

异步复位

收获:

代码:

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output q);

always@(posedge clk or posedge ar)

begin

if(ar)

q <= 1'b0;

else

q <= d;

end

endmodule

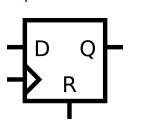

9.DFF

功能:

同步复位

收获:

代码:

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

always@(posedge clk)

begin

if(r)

q <= 1'b0;

else

q <= d;

end

endmodule

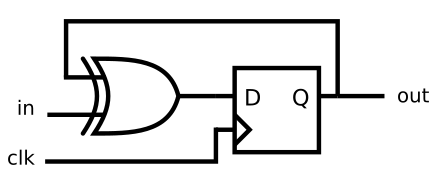

10.DFF+gate

功能:

收获:

代码:

module top_module (

input clk,

input in,

output out);

wire s;

reg a;

assign out = a;

always@(posedge clk)

begin

a <= in^out;

end

endmodule

11.Mux and DFF

功能:

该电路是由三个红圈子模块构成的,把红圈模块写出来。

收获:

一个大电路是由很多个小电路,小模块组成的,要先把小模块写好,再进行拼接。

代码:

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

wire d;

assign d = L?r_in:q_in;

D D_inst0(

.d(d),

.clk(clk),

.q(Q)

);

endmodule

module D(input d,input clk,output q);

always@(posedge clk)

begin

q <= d;

end

endmodule12.Mux and DFF

功能:

收获:

代码:

module top_module (

input clk,

input w, R, E, L,

output Q

);

//

wire a,b;

//

assign a = E?w:Q;

assign b = L?R:a;

D D_inst0(

.d(b),

.clk(clk),

.Q(Q),

.q()

);

endmodule

module D(input d,input clk,output Q,output q );

assign Q = s;

assign q = ~s;

reg s;

always@(posedge clk)

begin

s <= d;

end

endmodule13.DFF and gates

功能:

收获:

代码:

module top_module (

input clk,

input x,

output z

);

//

wire Q0,Q1,Q2;

wire d0,d1,d2;

wire q1,q2;

//

assign d0 = x^Q0;

assign d1 = x&q1;

assign d2 = x|q2;

assign z =~(Q0|Q1|Q2);

D D_inst0(

.d(d0),

.clk(clk),

.set(1'b0),

.Q(Q0),

.q()

);

D D_inst1(

.d(d1),

.clk(clk),

.set(1'b0),

.Q(Q1),

.q(q1)

);

D D_inst2(

.d(d2),

.clk(clk),

.set(1'b0),

.Q(Q2),

.q(q2)

);

endmodule

module D(input d,input clk,input set,output Q,output q);

//

reg s;

//

assign Q = s;

assign q = ~s;

always@(posedge clk or posedge set)

begin

if(set)

s <= 1'b0;

else

s <= d;

end

endmodule

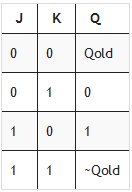

14.Create circuit from truth table

功能:

JK触发器

Qold是上一次Q输出的值

收获:

代码:

module top_module (

input clk,

input j,

input k,

output Q);

//

reg s;

//

assign Q = s;

always@(posedge clk)

begin

s <= 1'b0;

case({j,k})

2'b00: s <= s;

2'b01: s <= 1'b0;

2'b10: s <= 1'b1;

2'b11: s <= ~s;

default: s <= 1'b0;

endcase

end

endmodule

15.Detect circuit from truth table

功能:

检测输入位数的变化,检测上升沿。

收获:

代码:

自己想法代码:(繁琐,易错)不建议使用

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

//

reg [7:0] a,a_old,comp;

//

assign pedge = comp;

always@(posedge clk)

begin

comp = 8'b0;

a = in;

comp = a^a_old;

comp[0] =comp[0]?(a[0]?1'b1:1'b0):1'b0;

comp[1] =comp[1]?(a[1]?1'b1:1'b0):1'b0;

comp[2] =comp[2]?(a[2]?1'b1:1'b0):1'b0;

comp[3] =comp[3]?(a[3]?1'b1:1'b0):1'b0;

comp[4] =comp[4]?(a[4]?1'b1:1'b0):1'b0;

comp[5] =comp[5]?(a[5]?1'b1:1'b0):1'b0;

comp[6] =comp[6]?(a[6]?1'b1:1'b0):1'b0;

comp[7] =comp[7]?(a[7]?1'b1:1'b0):1'b0;

a_old = a;

end

endmodule

参考代码:(简单,不易错)建议使用

module top_module(

input clk,

input [7:0] in,

output reg [7:0] pedge);

reg [7:0] d_last;

always @(posedge clk) begin

d_last <= in; // Remember the state of the previous cycle

pedge <= in & ~d_last; // A positive edge occurred if input was 0 and is now 1.

end

endmodule

16.Detect both edges

功能:

检测输入数据变化,上升下降都检测。

收获:

代码:

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

//

reg [7:0] in_old,comp;

//

assign anyedge = comp;

always@(posedge clk)

begin

in_old <= in;

comp <= in^in_old;

end

endmodule

17.Edge capture register

功能:

输入32位数据,捕获数据变化下降沿,并在对应位输出1,同步复位。

收获:

代码:

module top_module (

input clk,

input reset,

input [31:0] in,

output reg [31:0] out

);

//

reg [31:0]in_old;

//

always@(posedge clk)

begin

in_old <= in;//存储一个周期的数据

if(reset)//复位

out <= 32'b0;

else if(in == in_old)//如果和上一个周期的数据比较没有改变,输出值不用改变

out <= out +32'b0;

else///输出值有改变

begin

for(int i=0;i<32;i++)

begin

if(!out[i])//对应位数输出值不为1,进行捕获

out[i] <= in_old[i]?(~in[i]):1'b0;

else

out[i] <= 1'b1;

end

end

end

endmodule

18.Dual-edge triggered flip-flop

功能:

收获:

试了很多种想法,总是达不到理想的情况,最后上网找到别人的代码,借鉴了一下,这里写下思考。

思考:首先明确了在一个always里不能同时出现posedge clk 和 negedge clk 两种情况,那么我的想法就是使用两个always将对敏感信号分开,既然不可以在一个里边对信号的上升沿和下降沿同时敏感,那么可以使用两个模块分别对上升沿下降沿进行敏感,但是在之后什么时候轮到哪个采用了很多办法,总是在时序上和要求差了些。对于这个使用异或代码,进行分析,首先使用两个模块,这和我的想法一样,但是它是将两个模块的结果交叉运用,这样就做到了,轮流检测。使用异或可以做到,如果是上升沿,那么输出q = q2^d^q2=d,如果是下降沿,那么输出的是q = q1^q1^d=d,两个相同的数做异或,结果全为0,一个全零的数和d做异或,结果还是d,所以非常巧妙地解决了敏感两个时钟沿,并且解决了直接赋值会出现的多个驱动问题。

代码:

module top_module (

input clk,

input d,

output q

);

//

reg q1,q2;

//

always@(posedge clk)

begin

q1 <= q2^d;

end

always@(negedge clk)

begin

q2 <= q1^d;

end

assign q = q1^q2;

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?