2024 年 8 月 7 日 — 世界领先的纳米电子学和数字技术研究和创新中心 Imec 在荷兰费尔德霍芬的 ASML-imec 高数值孔径 EUV 光刻实验室展示了使用 0.55NA EUV 扫描仪曝光后获得的图案化结构。低至 9.5 纳米(19 纳米间距)的随机逻辑结构、具有 30 纳米中心到中心距离的随机通孔、22 纳米间距的 2D 特征以及 P32nm 的 DRAM 特定布局是在单次曝光后打印的,使用的材料和基线工艺由 imec 及其合作伙伴在 imec 的高级图形化计划框架内针对高数值孔径 EUV 进行优化。凭借这些结果,IMEC 证实了生态系统已准备好实现单次曝光高分辨率高 NA EUV 光刻。

继最近在荷兰费尔德霍芬开设 ASML-imec 高数值孔径 EUV 光刻实验室后,客户现在可以使用 (TWINSCAN EXE:5000) 高数值孔径 EUV 光刻机,利用客户自己的设计规则和布局开发私有高数值孔径 EUV 用例。

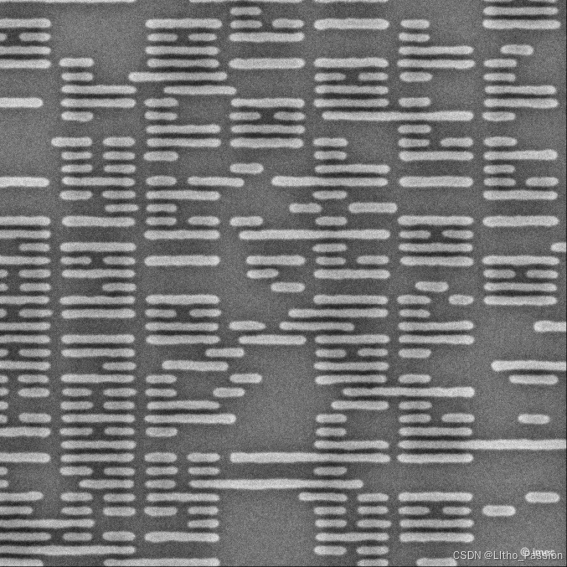

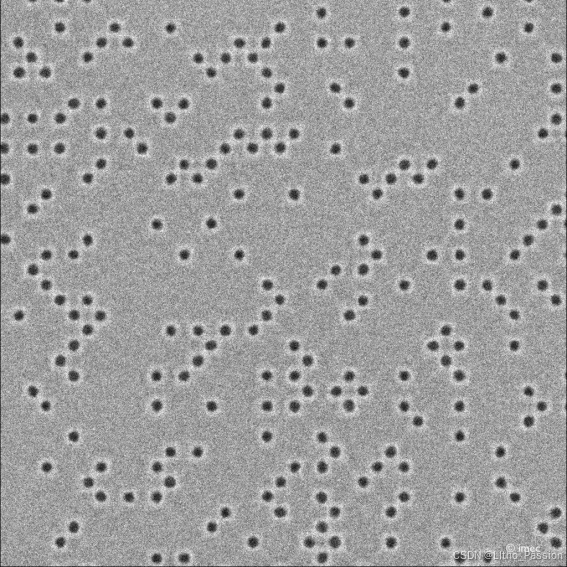

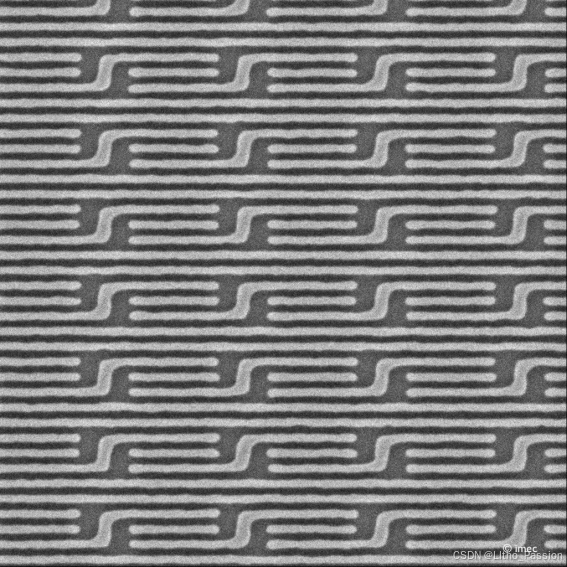

Imec 已成功图案化具有 9.5nm 密集金属线的单次曝光随机逻辑结构,对应于 19nm 间距,实现了低于 20nm 的尖端到尖端尺寸。中心到中心距离为 30nm 的随机通孔展示了出色的图形保真度和关键尺寸均匀性。此外,P22nm 间距的 2D 特征表现出出色的性能,凸显了高 NA 光刻技术实现 2D 布线的潜力。

图1:9.5nm逻辑结构

图2:30nm随机通孔

图3:P22 2D特征

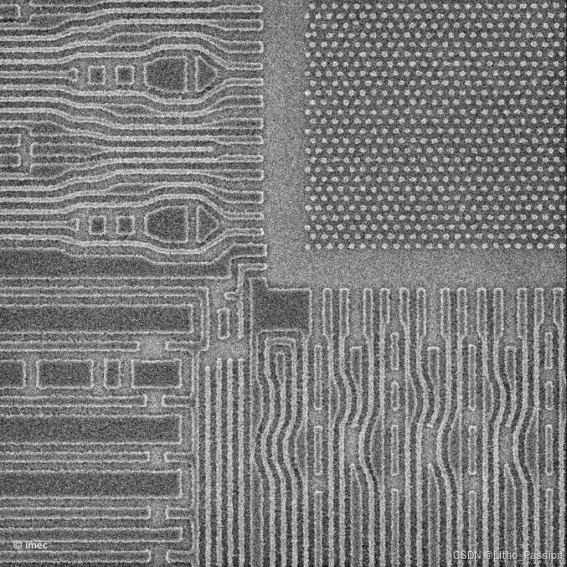

除了逻辑结构之外,imec 还成功地在一次曝光中设计了将存储节点着陆板与 DRAM 的比特线外设集成在一起的设计。这一成就突显了高数值孔径技术的潜力,即用 1 次曝光取代多个掩模层的需求。

图4:存储节点着陆版和DRAM 比特线外设集成

这些突破性成果是在 imec 和 ASML 与其合作伙伴密切合作进行密集准备工作之后取得的,为第一代高数值孔径 EUV 光刻技术准备了图形化生态系统和计量。在曝光之前,imec 准备了专用的晶圆堆栈(包括高级光刻胶、底层和光掩模),并将高数值孔径 EUV 基线工艺(如光学邻近校正 (OPC)、集成图案化和蚀刻技术)转移到 0.55NA EUV 扫描仪。

imec计算技术和系统/计算系统扩展高级副总裁Steven Scheer表示:“我们很高兴能在ASML-imec联合实验室展示世界上首个高数值孔径启用的逻辑和内存模式,作为对行业应用的初步验证。结果展示了高数值孔径 EUV 的独特潜力,可实现大比例 2D 特征的单印成像,提高设计灵活性并降低图形化成本和复杂性。展望未来,我们期望为我们的图形生态系统合作伙伴提供有价值的见解,支持他们进一步完善高数值孔径 EUV 特定材料和设备。

imec 总裁兼首席执行官 Luc Van den Hove 表示:“结果证实了长期预测的高数值孔径 EUV 光刻技术分辨率能力,可在一次曝光中针对低于 20nm 间距的金属层。因此,高 NA EUV 对于继续逻辑和存储器技术的维度扩展将发挥重要作用,这是将路线图深入“埃时代”的关键支柱之一。这些早期演示只有在 ASML-imec 联合实验室的建立下才成为可能,这使我们的合作伙伴能够加速将高 NA 光刻技术引入制造。

免责声明:

本板块主要聚焦半导体相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源。所发布的文章或者引用的内容若存在版权等问题,请留言联系删除,谢谢。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?