一、基础知识

1. 简介

I2C 总线是一种串行、半双工总线,主要用于近距离、低速的芯片之间的通讯。

I2C 总线有两根双向信号线,一根数据线 SDA 用于收发数据,一根时钟线 SCL 用于通讯双方时钟同步。

I2C 总线是一种多主机总线,总线上器件分为主机和从机。主机有权发起和结束一次通信,从机只能被主机呼叫。总线上多个主机同时启动时,会进行冲突检测和仲裁防止错误产生。每个器件(拥有唯一地址 7bit)都可以作为主机,也可以作为从机。

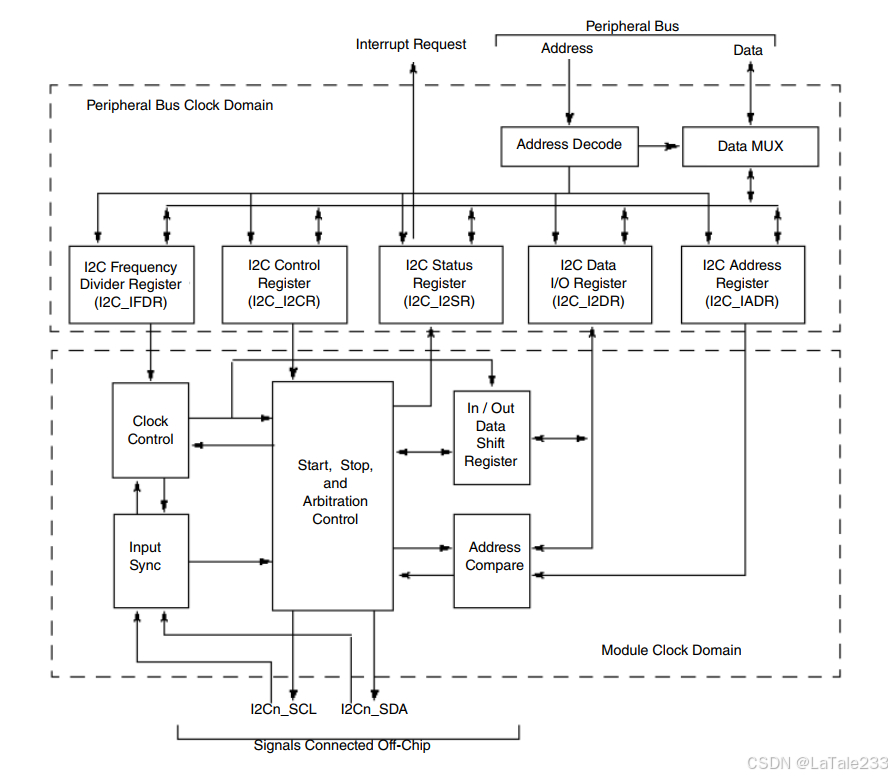

2. 硬件框架

参考: im6uxll 芯片手册

1. 模式

- 在标准模式下,I2C⽀持⾼达100 kbits / s的数据传输速率。

- 在快速模式下,可以实现⾼达400 kbits / s的数据传输速率。

对于每个块操作而言,在标准模式(Standard mode)和快速模式之间没有特别的配置要求。区分标准模式和快速模式的是数据传输速率

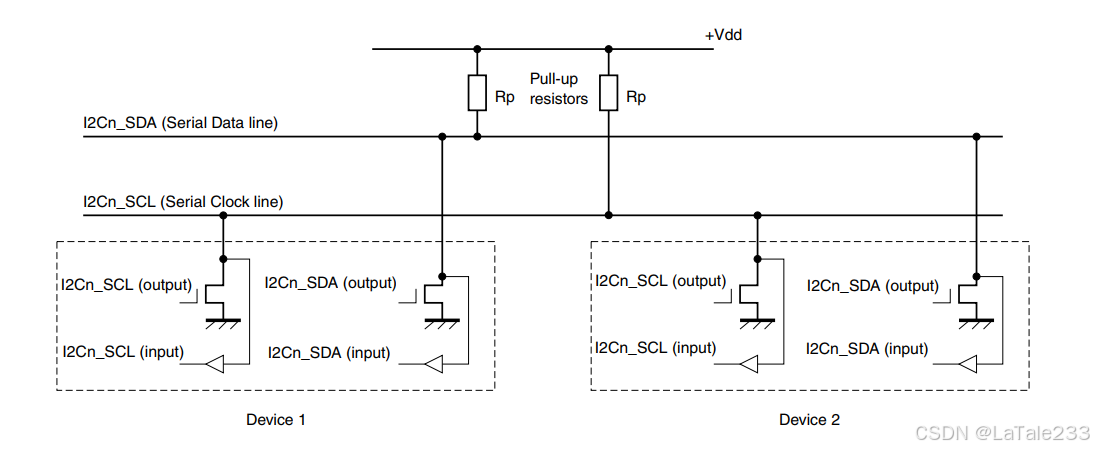

2. 外部信号

为了符合 I2C 规范,所有连接到 I2Cn_SCL 和 I2Cn_SDA 信号的设备必须具有开漏(open-drain)或集电极开路(open-collector)输出。外部上拉电阻在两条线上实现了逻辑与(AND)功能。

I2Cn_SCL 和 I2Cn_SDA 的输入也需要通过在 IOMUX 中设置 SION 位来手动启用,前提是相应的引脚(PADs)已被选择为 I2C 功能。

3. 时钟

I2C有两个输⼊时钟

- 外设时钟:此与时钟用于外设总线寄存器的读/写操作。

- 模块时钟:这是 I2C 的功能时钟。串行位时钟频率从模块时钟派生。模块时钟和外设时钟是同步的。为了实现快速模式下的 400 kbps 操作,模块时钟的最小频率应为 12.8 MHz。

| 时钟名称 | 时钟根 | 描述 |

|---|---|---|

| ipg_clk_patref | perclk_clk_root | 模块时钟 |

| ipg_clk_s | ipg_clk_root | 外设访问时钟 |

3. 软件框架

1. 通讯过程

- 主机发起其实信号启用仲裁

- 主机发送一个字节数据指明从机地址和后续字节的传送方向

- 被寻址的从机发送应答信号回应主机

- 发送器发送一个字节数据

- 接收器发送应答信号回应发送器

- 重复 4 和 5 进行通讯 。。。。。。

- 通讯完成后主机发送停止信号释放总线

2. 起始信号和停止信号

- SCL 为高电平时,SDA 由高变低表示起始信号。

- SCL 为高电平时,SDA 由低变高表示停止信号。

- 起始信号和停止信号都由主机发出,起始信号产生后总线处于占用状态,停止信号产生后总线处于空闲状态。

3. 字节传送和应答

I2C 总线通讯时每个字节为八位长度。数据传输时,先传高位后传低位;发送器发送完一个字节数据后接收器必须发送一位应答来回应发送器,即一帧数据有 9 位。

4. 同步信号

IIC 总线在进行数据传输时,SCL 为低电平期间发送器向数据线上发送一位数据,再次期间数据线上的信号允许变化;SCL 为高电平期间接收器从数据上读取一位数据,在此期间数据线上信号不允许变化,必须保持稳定。

5. 典型 IIC 时序

1. 主机向从机发送数据

2. 从机向主机发送数据(寻址完成后)

3. 主机先向主机发送数据,然后从机在向主机发送数据

6. 仲裁程序

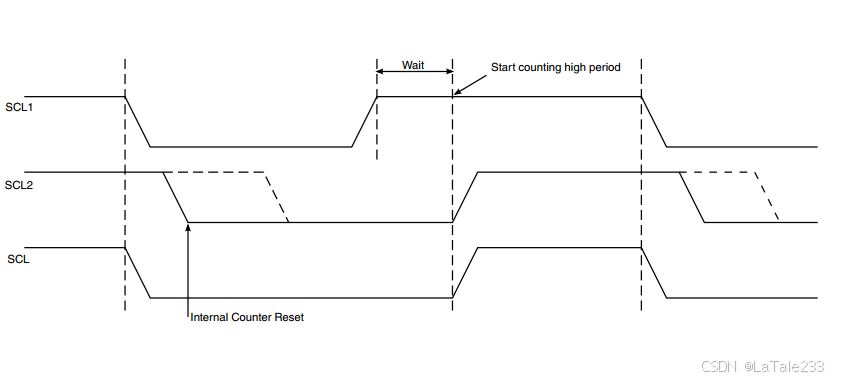

如果多个设备同时请求总线,时钟信号的生成由一个同步过程决定,其中低电平周期等于所有设备中最长的时钟低电平周期,而高电平周期等于最短的时钟高电平周期。数据仲裁过程确定了竞争设备的相对优先级。

如果一个设备在发送逻辑高电平时,另一个设备发送逻辑低电平,那么该设备将输掉仲裁,并立即切换到从设备接收模式,停止驱动 I2C 总线的数据线 (I2C_SDA)。在这种情况下,从主设备模式切换到从设备模式不会生成停止条件。同时,硬件会在 I2C 状态寄存器(I2C_I2SR[IAL])中设置仲裁丢失标志,表示仲裁失败。

7. 时钟同步

由于采用了与门逻辑(wire-AND logic),SCL 上的高电平到低电平的过渡会影响所有连接到总线的设备。当主设备将 SCL 拉低时,所有设备开始计数它们的低电平周期。当某个设备的时钟进入低电平时,它会保持 SCL 为低电平,直到时钟进入高电平状态。然而,如果其他设备的时钟仍然处于低电平周期,那么该设备时钟的低电平到高电平的变化可能不会改变 SCL 的状态。因此,低电平周期最长的设备会保持同步时钟 SCL 为低电平。

低电平周期较短的设备在此期间进入高电平等待状态。当所有参与的设备都计数完它们的低电平周期后,同步时钟 SCL 被释放并拉高。此时,设备时钟与 SCL 状态之间没有差异,所有设备开始计数它们的高电平周期。第一个完成高电平周期的设备会再次将 SCL 拉低。

8. 握手

时钟同步机制可以作为数据传输中的握手信号。在完成一个字节传输(9位)后,从设备可以将 SCL 拉低。在这种情况下,时钟同步机制会暂停总线时钟,并强制主设备的时钟进入等待状态,直到从设备释放 SCL。

9. 时钟拉伸

从设备可以使用时钟同步机制来降低传输比特率。在主设备将 SCL 拉低后,从设备可以将 SCL 拉低一段时间,然后释放它。如果从设备的 SCL 低电平周期长于主设备的 SCL 低电平周期,那么最终的 SCL 总线低电平周期将被拉长。

10. 复位

I2C 可以通过以下方式进行复位:

- 全局复位:对整个 I2C 进行硬件异步复位。

- 软件复位:通过内部复位对整个 I2C 进行复位(除了 I2C_IADR 和 I2C_IFDR 寄存器),复位是通过取消 I2C_I2CR[IEN] 位的使能来触发的。

11. 中断

该模块只有一个中断,通过设置 I2C_I2CR[IIEN] 位来启用。中断会在以下任意一种条件下生成:

- 完成一个字节的传输(在第九个时钟的下降沿设置中断)。

- 在从接收模式下接收到与自身特定地址匹配的地址。

- 仲裁丢失。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

310

310

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?