http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0471c/BABDCIEH.html

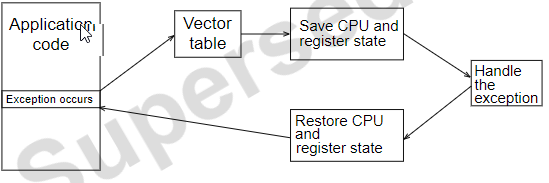

exception handling process

1.exception desc

2.vector table

Example 36. Typical vector table using a literal pool

AREA vectors, CODE, READONLY

ENTRY

Vector_Table

LDR pc, Reset_Addr

LDR pc, Undefined_Addr

LDR pc, SVC_Addr

LDR pc, Prefetch_Addr

LDR pc, Abort_Addr

NOP ;Reserved vector

LDR pc, IRQ_Addr

FIQ_Handler

; FIQ handler code - max 4kB in size

Reset_Addr DCD Reset_Handler

Undefined_Addr DCD Undefined_Handler

SVC_Addr DCD SVC_Handler

Prefetch_Addr DCD Prefetch_Handler

Abort_Addr DCD Abort_Handler

IRQ_Addr DCD IRQ_Handler

...

END

3.processor register

The ARM architecture defines an unprivileged User mode containing 15 general purpose registers, a PC, and a CPSR. In addition there are other privileged modes, each containing a SPSR and a number of banked out registers.

Typically, an application runs in User mode, but handling exceptions requires a privileged mode. An exception changes the processor mode, and this in turn means that each exception handler has access to a certain subset of the banked out registers:

its own Stack Pointer (SP)

its own LR

its own SPSR

five additional general purpose registers (FIQ only).

Each exception handler must ensure that other registers are restored to their original contents on exit. You can do this by saving the contents of any registers that the handler requires onto its stack and restore them before returning.

Use of System mode for exception handling

Corruption of the link register can be a problem when handling multiple exceptions of the same type.

ARMv4 and later architectures include a privileged mode called System mode, to overcome this problem. System mode shares the same registers as User mode, it can run tasks that require privileged access, and exceptions no longer overwrite the link register.

Note

System mode cannot be entered by an exception. The exception handlers modify the CPSR to enter System mode.

The processor response to an exception

This describes the processor response to an exception. You must ensure that the exception handler saves the system state when an exception occurs and restores it on return.

Processors that support Thumb state use the same basic exception handling mechanism as processors that do not support Thumb state. An exception causes the next instruction to be fetched from the appropriate vector table entry.

When an exception is generated, the processor performs the following actions:

Copies the CPSR into the appropriate SPSR. This saves the current mode, interrupt mask, and condition flags.

Switches state automatically if the current state does not match the instruction set used in the exception vector table.

Changes the appropriate CPSR mode bits to:

Change to the appropriate mode, and map in the appropriate banked out registers for that mode.

Disable interrupts. IRQs are disabled when any exception occurs. FIQs are disabled when an FIQ occurs and on reset.

Sets the appropriate LR to the return address.

Sets the PC to the vector address for the exception.

964

964

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?